発明は産業の起爆剤であるがその発明には高度の技術レベルの知識を必要とする

場合が多い。なかなか専門外の人間にはその発明の重要性が理解できない。技術

開発の進歩につれて別の人が再発見して自分が初めての考案者だと誤解している

場合も生じている。まわりの人間もそう誤解しつつも、企業の商品開発化の努力が

加速されてゆく。特に戦塵を切る企業は他社の追従を避ける為に発明の内容を素人

に詳しく説明・解説することはしない。無駄な努力と見なされる。発明は専門知識の

ある人間が理解できるレベルの説明で十分である。それで知的財産権が正当に主張

できれば、それで発明として効力を有することになるからである。だれも発明者を認定

する組織はない。特許庁や発明協会は一般世間からは発明に関する専門家集団と

見なされているが、実は特許庁や発明協会の取り扱う発明項目は多種多様でその1つ

1つの発明の専門家が存在するわけではない。しかし、特許の請求範囲を定義する

文書に関しては十分に理解できる程度の専門弁理士をかかえている必要がある。

各特許の審査においてはそれなりに個別に委員会を設定して、その特許が本当に

世界最初の発明特許であるかどうかの判断程度はできる能力があると世間一般は

特許庁や発明協会には期待している。特許庁や発明協会権威ある組織である。今

の最大の問題は日本の知的財産の日本国特許が日本語で記載されているだけで、

英文で記載されておらず英文を公用語とする国際社会にはその存在が全く今迄知ら

れないままになり真の発明は誰か誤解されたままになる危険がいつも存在する。

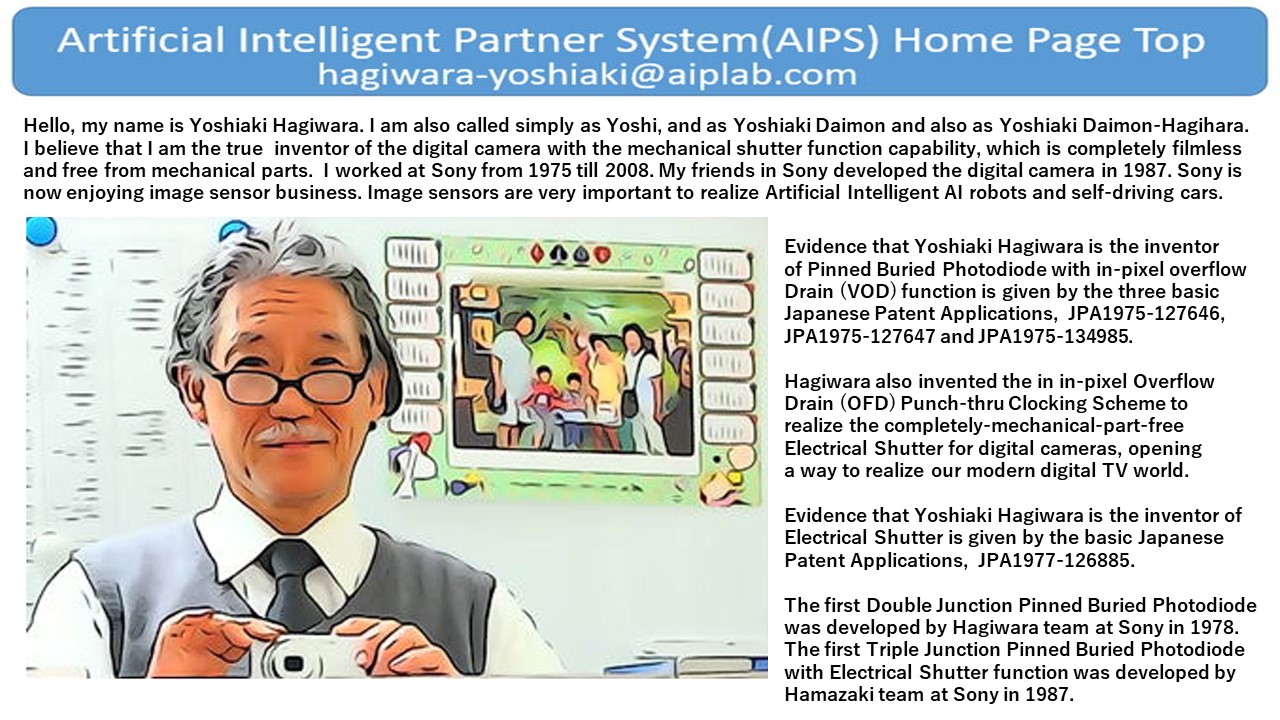

1975年に出願の萩原の3件の特許もその典型的なケースである。

********2021年9月21日(火)萩原良昭のつぶやき********

すでにMOSFETのような素子の特許は最初にカナダで、1925年10月22日に出願され

ていた。US 1745175 "Method and apparatus for controlling electric current"first

filing in Canada on October 22, 1925.

その特許は「弱い」(実動しない)ものだった。理論は正しいが、MOS容量構造の酸化膜

とシリコン表面の界面準位(Qss)の制御手段がまだまだ不完全である事が実は要因で

1960年の後半まで待つ必要があった。

1945年に戦争が終わると、米国のベル研究所に固体物理学部門ができた。そこで、

ショックレーと化学者スタンレー・モルガンが指揮することになった。他のメンバーとしては、

ジョン・バーディーン、ウォルター・ブラッテン、物理学者のジェラルド・ピアソン、化学者の

ロバート・ギブニー、電子工学者のヒルバート・ムーア、および数人の技術者がいた。彼ら

の当面の目標は、真空管増幅器の代替となる固体(半導体)を見つけることだった。

1946年の冬までに十分な結果が得られ、バーディーンはフィジカル・レビュー誌に表面

準位についての論文を送った。ブラッテンは表面準位の研究の為、半導体の表面に強い

光を当てる実験を始めた。そこからさらに論文が書かれ、一部はショックレーと共同で、

初期の実験が失敗した原因が推測できるようになった。

研究が軌道に乗ったのは、半導体と導体の導線の接触点を電解液に浸すという実験を

行ってからのことである。ムーアは入力信号の周波数を容易に変更できる回路を組み

立てた。

ショックレーの助言に従い、ピアソンはpn接合の接合部分にホウ酸グリコール(蒸発

しない粘性のある化学物質)の小滴を置き、そこに電圧を印加してみた。これによって

ついに増幅作用が観測されるようになった。ベル研究所の弁理士は間もなく、ショック

レーの電界効果の原理が既に予測され、ユリウス・エドガー・リリエンフェルトが1930年

にそれを利用した装置の特許を取得済みであることを発見した。

1947年の暮れになり、バーディーンとブラッテンは2人で点接触型トランジスタの発明と

その原理試作に成功した。その2人上司であったがショックレーはその2人の功績に全く

関与していない出来ごとだった。

その後、今から73年前(1948)、米国のベル研究所で点接触型トランジスタが一般公開

された。ベル研究所の弁理士はその時4つのトランジスタの関連特許を出願することを

進めた。衝突を避けて4つの特許のうちの1つに関しては、バーディーンとブラッテンに

よる点接触型設計のみを扱った。

他の3つの特許(先に出願)は、バーディーン、ギブニー、ブラッテンを発明者として電解質

を使ったトランジスタの特許(MOStトランジスタ型特許)とした。

つまり、ショックレーはこれらのトランジスタの基本特許出願書に発明人として名を一つも

発明者として連ねていなかった。この事実はあまり知られていない。ショックレーは電界

効果のアイデアが再発見し自分が最初のその発明者だと誤解した。

すでにMOSFETのような素子の特許は最初にカナダで、1925年に出願されており

ベル研究所の弁理士はショックレーの電界効果のアイデアは周知情報と見なした。

そこで、ショックレーは「点接触型トランジスタは壊れやすく製造が難しい」と考えた。

むしろ、ショックレーは独自に点接触型ではなく接合型のトランジスタを作る作業を

続けた。そちらの方が量産しやすいと予想したためである。ライバル意識が効果を

発揮した。ショックレーはまた、点接触型トランジスタの動作原理の説明や少数

キャリア注入の可能性についても完全には納得していなかった。ショックレーは

「サンドイッチ構造」トランジスタと自ら名付けたものについてより徹底的な説明を

考え、1949年4月7日にその動作原理の証明を得た。

これによって生まれた発明が接合型トランジスタで、1951年7月4日に報道陣に

対して発表を行った。この発明の特許は1951年9月25日に発効。その後、様々な

製造技法が考案されたが、最終的には拡散とフォトリソグラフィによる製造が急速

に広まった。間もなく点接触型トランジスタを圧倒するようになり、しばらくの間市場

を支配することになった。

ショックレーはさらに2年間、ベル研究所でトランジスタの改良に取り組むグループ

を指揮した。 ショックレーの接合型トランジスタが実用化された。一方でショックレー

は558ページの大著 Electrons and Holes in Semiconductorsを書き上げ、1950年

に出版した。その中でショックレーはドリフト-拡散モデルを説明し、半導体内の電子

の流れを表す微分方程式を記している。ショックレーのダイオード方程式もその中に

記されていた。トランジスタの改良や新たな半導体素子を発明しようとする科学者に

とって、この著作は一種の「聖書」となった。

今から73年前(1948)、米国のベル研究所でトランジスタが一般公開された。その

6年後には、テキサス・インスツルメンツ(TI)社が生産を開始、真空管が固体素子に

変わることのインパクトがいくら大きいとはいえ、信じがたいスピード感であった。それ

から2年後にはショックレー、バーデイーン、ブラッテンの3人がトランジスタの発明で

ノーベル物理学賞を受賞した。

ただ、最初のトランジスタは点接触型であって、その発明にはグループリーダーの

ショックレーは係わってはいない。その後TI社のトランジスタ生産開始の翌年には

ショックレーはショックレー・セミコンダクタ社を設立している。

日本では発明にかかわっていなくても上司が発明者として名を連ねるのが慣例で

あった。一方、アメリカでは誰の発明ということだけが前面に出される。

こういったところにも本質を外した問題を抱えて日本は走ってきたと言える。

しかし、ショックレーはこれに刺激され、より実用化に有利な接合型の理論を

打ち立てた功績は大きかった。またイオン注入の基本的な発明もショックレー

が成し遂げていたことは驚くべきことだった。

そういう客観的な事実はあまり一般には知られていない。

半導体の世界で有名なムーアの法則を見出した、ゴードン・ムーアとともに後

のインテルの創業者になったロバート・ノイスら若い技術者は、しかし、ショッ

レー・セミコンダクタ社のショックレーの人柄による為か、その経営方針と衝突を

繰り返している間に、社長のショックレーがノーベル賞を取ってしまった為に

社長を更迭できず、ゴードン・ムーアとロバート・ノイスは結局自分たちが飛び

出すこととなった。

そして、ゴードン・ムーアは、1957年にフェアチャイルド社を設立した。

1960年には世界初の集積回路の発売を成し遂げられた。IBMが大型電子

計算機を、DECがミニコンを発売した。1968年にはムーアはフェアチャイルド社

の経営陣と意見が合わず、ムーアは再び飛び出し、ムーアはインテルを設立した。

ショックレーもゴードン・ムーアも同じカリフォルニア工科大学の卒業生であった。

萩原良昭は1967年にカリフォルニア工科大学に入学した。まだ何も知らない無知な

学生だったが、後で、自分の大学の先輩の中に、ショックレーやゴードン・ムーア等が

いることを知り、たいへん誇りに感じた。

萩原良昭は1967年にカリフォルニア工科大学に入学してすぐに大学1年生と2年生

の2年間をかけて新しく刊行された Feynman Physics の3冊の赤い古典的な物理

の本を教科書として古典物理、電磁力学、量子力学を学んだ。

2年生の後期には半導体のバンド理論を学び、Bipolar Transistorの構造とその

動作原理を Feynman Physics の3冊目の赤い物理の本の中で学んだ。

大学3年生になると、Andy Grove著の Physics of Semiconductorを教科書にして

Prof. James McCaldin の授業を受けた。

大学4年生になると、Prof.C.A. Mead の指導のもと、卒業研究実験テーマとして、

酸化ガリウム(Ga2O3)の半導体の金蒸着により、GA2O3 ショトキーダイオードを

試作してその特性を測定評価した。

大学院1年生の修士課程では、Intel社とCaltechの産学協同研究プロジェクトに

参画してIntel社のDRAMプロセスを使って、128 bit data stream 高速並列処理

プロセッサーの設計に挑戦した。

MOS Transistorの集積回路設計のCAD Tool 環境学びその技術を習得して独自

のCAD Programを構築しながらのすべて手弁当での大規模集積回路の設計へ

の挑戦だったが見事に一発完全動作を実現した。

博士論文課程では、半導体デバイス物理学者のProf. T.C. McGillが、萩原のPhDの

論文の主管指導官として指導を受け、当時脚光を浴びていた、Buried Channel 型の

Charge Transfer Device (CCD)ので半導体デバイス構造とその動作解析をテーマに

して博士課程の論文を書いた。

1973年の夏には、萩原に日本に夏休みで一時帰国していた。その時に2度に渡り、

萩原のCaltechの先輩研究生からの紹介を受けて、ソニー厚木工場で学生実習生

として指導を受ける機会をいただいた。その時に、ソニーが誇る、Bipolar Transisto

のプロセス技術をその集積回路の信頼性技術について学んだ。

そのことがヒントになり、ソニー入社して間もなく、PNP double 接合のdynamic photo

bipolar transistor 型と、PNPN triple 接合の thyristor Transistor型のPinned Buried

Photodiodeを発明することとなった。非常にラッキーな発明であった。

その発明がソニーのイメージセンサーのビジネスを、KODAK社やFairchild社やNEC

などからの特許攻撃から守った。

今でもソニーに裏照射型 CMOS Image Sensor の受光素子には、1975年萩原良昭発明

の PNP double 接合の dynamic photo bipolar transistor 型のPinned Buried Photodiode

(別名、Sony Hole Accumulation Diode, HAD) が活躍している。

特にFairchild社との特許戦争は1990年から始まり2000年までの10年以上も続いた。

その時にCaltechの大先輩(萩原より12歳年上)で、当時 UC Davis の教授だった、

Prof. Bob Bowerは、ソニー側の弁護士の依頼で、ソニー側の証言者として法廷に立った。

Prof. Bob Bowerは、ソニーのためにソニーのCCDの製法プロセスがFairchild社の特許

侵害にならない事を証言した。

Prof. Bob Bower は、イオン打ち込み技術開発の専門家として、また、ポリシリコン電極

パターンをマスクにして、self-align 整合型のイオン打ち込み手法の発明者として著名な

科学者である。

Prof. Bob Bowerの出願特許 (USP3615934, filed on Oct 17, 1967 and USP3615934,

filed on Oct30, 1967) を使って、Intel社は self-align 整合型の S/D領域を形成しIntel社

はMOS Transistor の実用化に成功し、DRAM LSI chipを生産した。Intel社は大型顧客

である IBMに納入し、当時、Intel は急成長していた。

またそのITIC型のDRAM構造の基本特許の発明者が実は国際社会では無名のNECの

技術者であることも現在あまり知られていない。

********2021年9月21日(火)萩原良昭のつぶやき********

発明は産業の起爆剤であるがその発明には高度の技術レベルの知識を必要とする

場合が多い。なかなか専門外の人間にはその発明の重要性が理解できない。技術

開発の進歩につれて別の人が再発見して自分が初めての考案者だと誤解している

場合も生じている。まわりの人間もそう誤解しつつも、企業の商品開発化の努力が

加速されてゆく。特に戦塵を切る企業は他社の追従を避ける為に発明の内容を素人

に詳しく説明・解説することはしない。無駄な努力と見なされる。発明は専門知識の

ある人間が理解できるレベルの説明で十分である。それで知的財産権が正当に主張

できれば、それで発明として効力を有することになるからである。だれも発明者を認定

する組織はない。特許庁や発明協会は一般世間からは発明に関する専門家集団と

見なされているが、実は特許庁や発明協会の取り扱う発明項目は多種多様でその1つ

1つの発明の専門家が存在するわけではない。しかし、特許の請求範囲を定義する

文書に関しては十分に理解できる程度の専門弁理士をかかえている必要がある。

各特許の審査においてはそれなりに個別に委員会を設定して、その特許が本当に

世界最初の発明特許であるかどうかの判断程度はできる能力があると世間一般は

特許庁や発明協会には期待している。特許庁や発明協会権威ある組織である。今

の最大の問題は日本の知的財産の日本国特許が日本語で記載されているだけで、

英文で記載されておらず英文を公用語とする国際社会にはその存在が全く今迄知ら

れないままになり真の発明は誰か誤解されたままになる危険がいつも存在する。

1975年に出願の萩原の3件の特許もその典型的なケースである。

***** hagiwara-yoshiaki@aiplab.com http://www.aiplab.com ******

++++++++++++++++++++++++++++++++++++++++++++++++

........Bio_of_Yoshiaki_Hagiwara.html...........

++++++++++++++++++++++++++++++++++++++++++++++++

Yoshiaki Hagiwara wrote a book on "the World of Artificial Intelligent Digital Circuits",

which is important and needed to built the intelligent image sensor systems.

++++++++++++++++++++++++++++++++++++++++++++++++++++

If you are interestied in purchasing this book, Please visit

https://www.seizansha.co.jp/ISBN/ISBN978-4-88359-339-2.html

https://www.seizansha.co.jp/

ISBM978-4-88359-339-2 ; Hard Cover, 460 page,\ 9000 Japanese Yen + tax

++++++++++++++++++++++++++++++++++++++++++++++++++++

.jpg)

If you are interestied in purchasing this book, Please visit

https://www.seizansha.co.jp/ISBN/ISBN978-4-88359-339-2.html

https://www.seizansha.co.jp/

++++++++++++++++++++++++++++++++++++++++++++++++++++

..........................................Yoshiaki_Hagiwara_Bio.pdf........................................

++++++++++++++++++++++++++++++++++++++++++++++++++++

(1)April 1973

"The Influence of Interface States on Incomplete Charge Transfer in Overlapping Gate Charge Coupled Devices"

IEEE Journal of Solid State Circuits,

Vol. SC 8, No.2, April 1973

(2)February 1974

"Charge Transfer of Buried Channel Charge Coupled Devices"

Proceeding of International Solid State Circuit Conference

(ISSCC1974),San Francisco, February 1974.

(3)April 1974

"Final Stage of the Charge Transfer Process in Charge Coupled Devices"

IEEE Transactions on Electron Devices,

Vol. ED-21, No.4, April 1974

(4) June 1975

Caltech_1975_PhD_Thesis_by_Yoshiaki_Daimon_Hagihara.pdf

in Electrical Engineering (major) and Physics(minor), June 1975,

California Institute of Technology, Pasadena, California USA.

(5) October 23,1975

Japanese Patent Application JPA1975-127646

on "Back-light Triple Junction Type Pinned Buried Photodiode

with Complete Charge Transfer Capability and Global Shutter Fucntion",

Japanese PAtent Application written in Japanese, filed on Oct 23, 1975

(6) October 23,1975

Japanese Patent Application JPA1975-127647

on "Back-light Double Junction Type Pinned Buried Photodiode

with Complete Charge Transfer Capability and Global Shutter Function",

Japanese Patent Application written in Japanese, filed on Oct 23, 1975

(7) November 10 1975

Japanese Patent Application JPA1975-134985

on "Triple Junction Type Pinned Buried Photodiode

with Complete Charge Transfer Capability and

Vertical Overflow Drain Function",

Japanese Patent Application written in Japanese,

filed on Nov 10, 1975.

(8) September 1976

"128-Bit Multi Comparator"

IEEE Journal of Solid State Circuits,

VOL.SC11, No.4, October 1976.

(9) September 1977

P1977_Narrow_Cahnnel_Transfer_Gate_CCD_SSDM1977_Paper_by_Hagiwara.pdf"

Proceeding of the 9th Conference on Solid State Devices,

Tokyo, September 1977

(10) September 1977

Japanese Patent Application JPA1977-126885

on "Electric Shutter Clocking and Gamma Control Scheme

using Overflow Drain (OFD) controlled

by Strong Punch Thru OFD Voltage Control",

Japanese Patent Application written in Japanese,

filed on Sep 29, 1977

(11) September 1978

Hagiwara_SSDM1978_Paper_on_Pinned_Buried_Photodiode.pdf

Proceeding of the 10th Conference on Solid State Devices,

Tokyo, September 1978.

(12) September 1979

"ADVANCES in CCD Imager " Technical Digest of IEEE

International Conference of CCD Image Sensors (IEEE CCD'79),

Edinburgh, Scotland UK, September 1979.

(13) May 1980

IEEE ECS1980 invited paper on "A CCD color imager with narrow-channel transfer gates"

Proceeding of the 157th Electrochemical Society Meeting,

May 11-16, 1980, St. Luis, USA.

(14) November 1980

Technology Book on "CCD Image Sensor and Applications"

Trickeps Press, November 1980.

(15) October 1989

"A 25-ns 4-Mbit CMOS SRAM with Dynamic Bit-Line Loads"

IEEE Journal of Solid State Circuits, vol.24, no.5, October 1989.

(16) December 1996

IEEE1996_Review_Paper_on_Sony_1980_One_Chip_FT_CCD_Image_Sensor

with_Pinned_Buried_Photodiode

IEEE Transaction on electron Devices,

VOl.43, No.12, Dec 1996.

(17) November 1997

"Sony Semiconductor History"

addressed at the 23th Research Seminar

in Tokyo Communication University, Nov 28, 1997.

(18) November 1998

"DRAM/SRAM Technology and Problem.pdf"

Proceedings of the Institute of Electrostatics Japan,

127 Vol. 22 No. 6, 1998, pp.177-178.

(19) September 2001

"Micro-Electronics for Home Entertainment"

an invited ESSCIRC2001 Plenary Talk,

Technical Digest of IEEE ESSCIRC2001 International Conference (ESSCIRC2001),

Villach, Austria, September, 2001.

(20) December 2004

Turorial Short Cource on Image Sesnors by Yoshiaki Hagiwara.pdf

IEEE IEDM2004 Conference Short Course at IEDM2004 Short Course, December 2004.

(21) September 2008

"SOI Design in Cell Processor and Beyond"

an invited ESSCIRC2008 Plenary Talk,

Technical Digest of IEEE ESSCIRC2008 Conference,

Edinburgh, Scotland UK, September 2008.

(22) September 2008

"SOI Design in Cell Processor and Beyond"

an invited ESSCIRC2008 Plenary Talk,

Technical Digest of IEEE International Conference ESSCIRC2008,

Edinburgh, Scotland UK, September 2008

(23) February 2013

Invited Plenary Panel Talk at ISSCCC2013 on Feb. 2013 on Image Sensors

(24) June 2013

"The p-n-p-n Diode in Future Linear Motor Cars and in Modern Imagers"

IEEE Journal of Solid State Circuits, June issue, 2013.

(25) July 2014

Japanese Patent Application JPA2014_135497

on "Digital Transformation Matrix for Fast Image Recognition System"

Japanese Patent Application written in Japanese,filed on July 1, 2014.

(26) July 2014

"Design of Time to Frequency Domain Discrete Fourier Transfer Hardware Engine and its performance estimation"

Digest of Technical Papers at the Japan Electron Society

sponsored Integrated Circuit Workshop in Izumo, Japan, July 2014.

(27) April 2017

IEEE_CoolChips_2017_Conference_Invited_Panel_Talk_on_Intelligent_Image_Sensor_Systems.pdf

(28) October 2019

"Multichip CMOS Image Sensor Structure for Flash Image Acquisition"

IEEE International 3D Systems Integration Conference 2019 (3DIC2019),

Digest of Technical Papers, Sendai, Japan, Paper4017, October 2019.

(29) March 2020

"Simulation and Device Characterization of the P+PN+P Junction Type Pinned Photodiode and Schottky Barrier Photodiode"

IEEE Electron Device and Manufacturing Technology Conference (EDTM2020),

Digestof Technical Papers, Penang Malaysia, Paper ID 3C4, March 2020.

(30) August 2020

Japanese Patent Application JPA2020-131313

on "Double Junction Pinned Buried Photodiode Type splar Cell"

Japanese Patent Application written in Japanese,

filed on August 1, 2020.

(31) June 2021

"Electrostatic and Dynamic Analysis of P+PNP Double Junction Type

and P+PNPN Triple Junction Type Pinned Photodiodes",

International Journal of Systems Science and Applied Mathematics, June 2,

doi: 10.11648/j.ijssam.20210602.13;

ISSN: 2575-5838 (Print);

ISSN: 2575-5803 (Online)

http://www.sciencepublishinggroup.com/journal/paperinfo?journalid=245&doi=10.11648/j.ijssam.20210602.13

+++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++

Contributions to International Conferences and Organizations

(1) International Standardization Committee (1989-1992)

IEC TC47 Technical Committee Chair (1992)

(2) JEDEC Memory Chips Standardization Committee (2000-2004)

(3) IEEE EDS ICMTS International Program and Executive Committee (1991-2008)

General Chair (2003-2004);http://icmts.if.t.u-tokyo.ac.jp/home

(4) IEEE SSS ISSCC Asian Program Committee (2001-2007)

ISSCC Asian Chair (2006-2007);http://isscc.org/

(5) IEEE SSS ISSCC2008 International Program and Executive Committee (2007-2008)

International Program Chair (2007-2008); http://isscc.org/

(6) IEEE Computer Society Cool Chips Organization Committee (2001-2010)

https://www.coolchips.org/

(7) IEEE Computer Society Cool Chips Advisory Committee (2011-2021)

https://www.coolchips.org/

(8) Visiting Professorship in Electric Engineering Department and

Applied Physics Department at California Institute of Technology,

Pasadena, califor, USA, 1998-1999;https://www.caltech.edu/

(9) Professorship in Electircal Engineering Department at Gunma University,

Kiryu-city, Gunma-ken, Japan, 2001-2008;https://www.gunma-u.ac.jp/

(10) Professorship in Information and Communication Tecnology Department

at Sojo University, Kumamoto-city, Japan, 2009-2017; https://www.sojo-u.ac.jp/

(11) Artificial Intelligent Partner System (AIPS) Consortium,Kanagawa-ken NPO, Japan,

President and CEO (2008-2017); http://www.aiplab.com//

(12) Society of Semiconductore Industry Experts of Japan ; http://www.ssis.or.jp/

currently also serving as the chairman of the SSIS Education Executive Committee.

+++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++

List of PDF files and published papers by Yoshiaki Hagiwara

Please write me freely to hagiwara-yoshiaki@aiplab.com

+++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++

(001) Sony_vs_Loral_Patent_War_1_Reviews.pdf

(002) Sony_vs_Loral_Patent_War_2_Supporting_Opinions.pdf

(003) E-mail_Communication_on_Sony_Loral_Patent_War_1996.pdf

(004) E-mail_communication_with_Albert_san_2018_07_10.pdf

(005) HAD_sensor_NEC_SONY_Patent_War.pdf

(006) JP1980_138026_NEC_Buried_Photodiode_Patent.pdf

(007) JP1978-1971_Toshiba_Yamada_VOD_patent.pdf

(008) Sony_vs_Loral_PAtent_War_13_pages.pdf

(009) Sony_vs_Loral_Patent_War_53_pages.pdf

(010) Image_Sensor_Story_by_Hagiwara.pdf

(011) The_evidence_that_Hagiwara_is_the_inventor_of_Pinned_Photodiode_7_pages.pdf

(012) Future_of_Image_Sensors_and_Solar_Cells.pdf

(013) JP1975-127646_NPNP_triple_junction_Pinned_Photodiode_Patent_32_pages.pdf

(014) The_First_Pinned_Photodiode_was_invented_in_1975_by_Yoshiaki_Hagiwar_at_Sony.pdf

(015) JP1975-127647_NPN_double_junction_Pinned_Photodiode_Patent_22_pages.pdf

(016) JP1975-134985_PNP_double_junction_Pinned_Photodiode_on_Nsub_Patent_7_pages.pdf

(017) JP1977-126885_Elecric_Shutter_Clocking_Scheme_by_OFD_Punch_Thru_Action_13_pages.pdf

(018) JP2014-135497_Digital_Transformation_Circuit_for_Image_Sensors_29_pages.pdf

(019) JP2020_131313_on_Doubel_Junction_Pinned_Photodiode_Solar_Cell_65_Pages.pdf

(020) P1978_Pinned_Photodiode_1978_Paper_by_Hagiwara_7_Pages.pdf

(021) P1996_Pinned_Photodidoe_used_in_Sony_1980_FT_CCD_Image_Sensor_9_Pages.pdf

(022) P2001_ESSCIRC2001_Micro-Electronics_for_Home_Entertainment_11_pages.pdf

(023) P2008_ESSCIRC_2008_SOI_Design_in_Cell_Processor_and_Beyond_7_pages.pdf

(024) P2013_ISSCC2013_Panel_Talk_25_pages.pdf

(025) P2017_CoolChips_Panel_170419_29_pages.pdf

(026) P2019_3DIC2019_Paper_on_3D_Pinned_Photodiode_6_pages.pdf

(027) P2020_EDTM2020_PaperID_3C4_by_Hagiwara_4_pages.pdf

(028) P2021_IJSSA2021_Paper_20210616_on_Electrostatic_and_Dynamic_Analysis_of_Pinned_Photodiodes.pdf

(029) Buried_Photodiode_is_not_always_PPD_Hagiwara_Nov_2020.pdf

(030) Caltech_1975_PhD_Thesis_Yoshiaki_Daimon_Hagihara.pdf

(031) Difference_of_Buried_Photodiode_and_Pinned_Photodiode.pdf

(032) E-mail_Communication_on_Sony_Loral_Patent_War_1996.pdf

(033) E-mail_communication_with_Albert_and_Yoshi.pdf

(034) E-mail_communication_with_Albert_san_2018_07_10.pdf

(035) E-mail_communication_with_Albert_san_2018_07_10A.pdf

(036) E-mail_communication_with_Albert_san_2018_07_10B.pdf

(037) Evidence_that_Hagiwara_is_the_inventor_of_Pinned_Photodiode_2020_10_04a.pdf

(038) Evidence_that_Hagiwara_is_the_inventor_of_Pinned_Photodiode_in_Japanese.pdf

(039) Future_of_Image_Sensors_and_Solar_Cells .pdf

(040) Hagiwara_at_Sony_invented_in_1975_and_developed_Pinned_Photodiode_in_1978.pdf

+++++++++++++++++++++++++++++++++++++++++++++++++++++++++

+++++++++++++++++++++++++++++++++++++++++++++++++++++++++

Return to Top Home Page of Yoshiaki Hagiwara (AIPS)

http://www.aiplab.com

+++++++++++++++++++++++++++++++++++++++++++++++++++++++++