## COOL Chips 20

YokohamaJoho Bunka Center, Yokohama, Japan (Yokohama Media & Communications Center)

April 19-21, 2017

#### Panel Discussion

Topics: "Cool chips for the next decade"

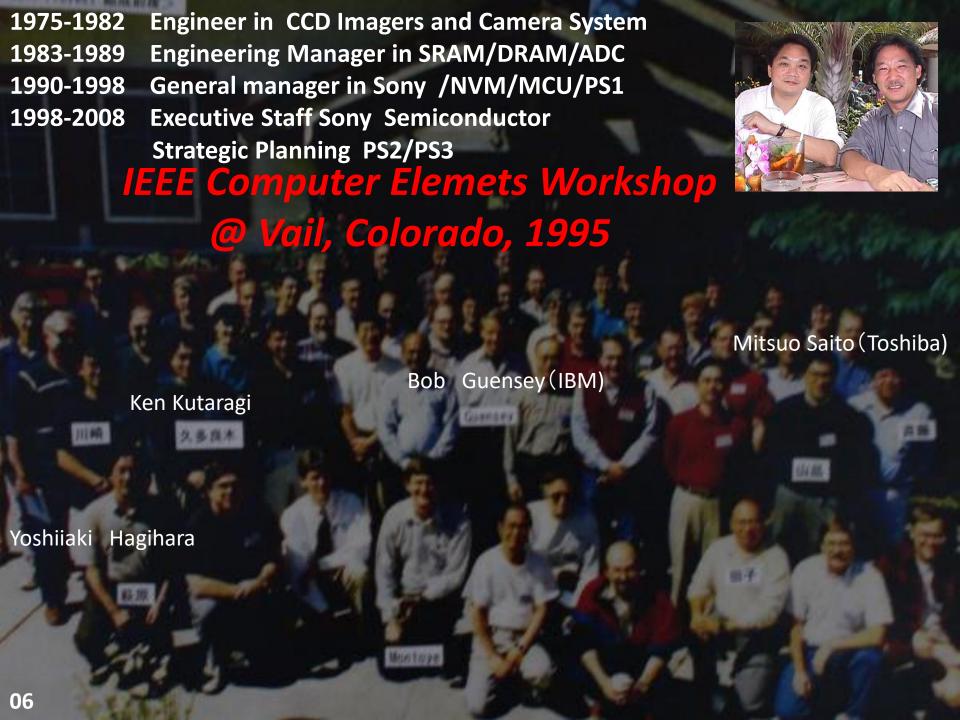

## Yoshiaki Hagiwara

http://www.aiplab.com/ Hagiwara-yoshiaki@aiplab.com

#### **ISSCC® 2013** | February 17-21

## 60 Years of (Em)Powering the Future

#### Plenary Talks (Monday, February 18)

Lisa Su Senior Vice President and General Manager, AMD

Architecting the Future through Heterogeneous Computing

Martin van den Brink

Executive Vice President and Chief

Product & Technology Officer, ASML

Next Generation Lithography: Progress and Outlook

Robert Brodersen Professor Emeritus University of California, Berkeley

Rinaldo Castello *Professor* University of Pavia

Yoshiaki Daimon Hagihara Professor Sojo University

Yoshiyuki Miyabe Managing Director and CTO, Panasonic

Smart Life Solutions from Home to Cities

Carver Mead Professor Emeritus, Cattech

The Evolution of Technology

Thomas Lee

Director

Microsystems Technology

Office, DARPA

Nicky Lu Chairman Etron Technology

Eric Vittoz Independent Consultant

# International Solid-State Circuits Conference February 17–21, 2013 | San Francisco, CA

Welcome to the 2013 IEEE International Solid-State Circuits Conference (ISSCC). This year, we will celebrate the 60th anniversary of ISSCC. ISSCC is the flagship conference of the Solid-State Circuits Society, and is the premier forum for the presentation of advances in solid-state circuits and systems-on-a-chip. The Conference offers a unique opportunity to network with leading experts in the field. For 2013, the Conference theme is "60 Years of (Em)Powering the Future". more

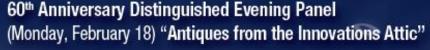

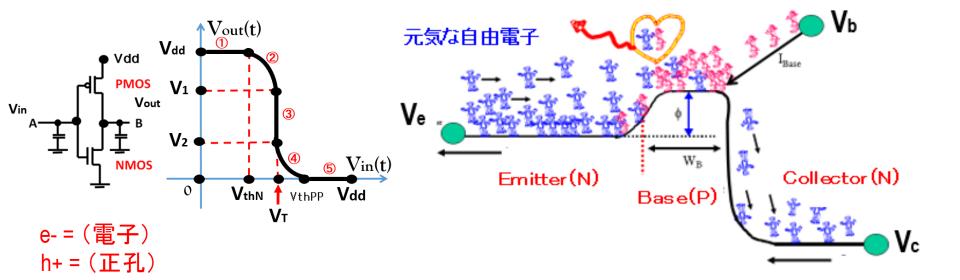

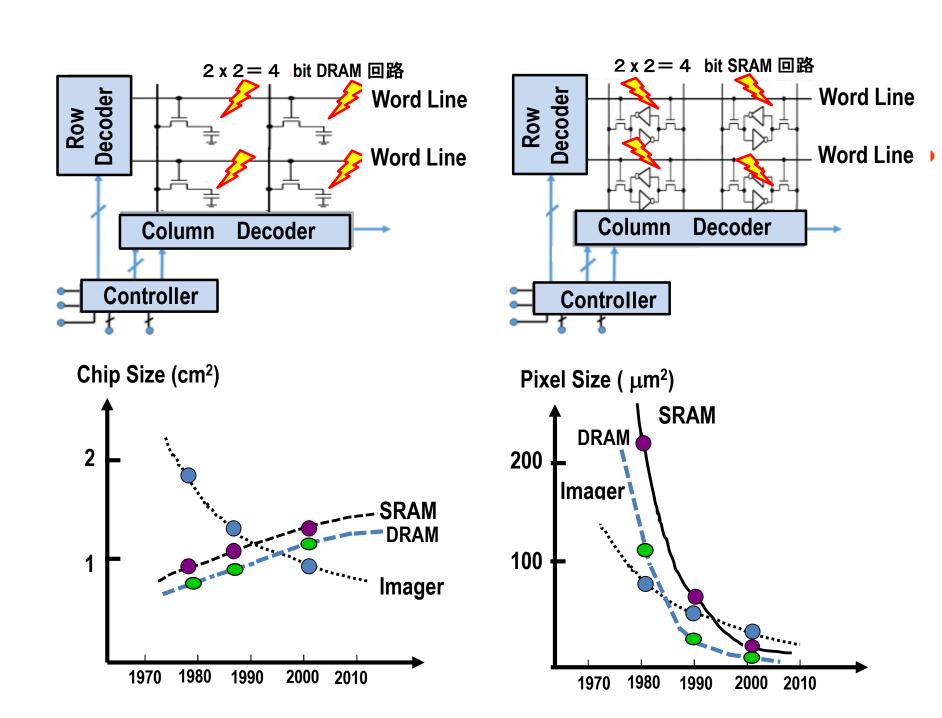

#### Yoshiaki Higihara: The p-n-p-n Diode in Future Linear Motor Cars and in Modern Imagers

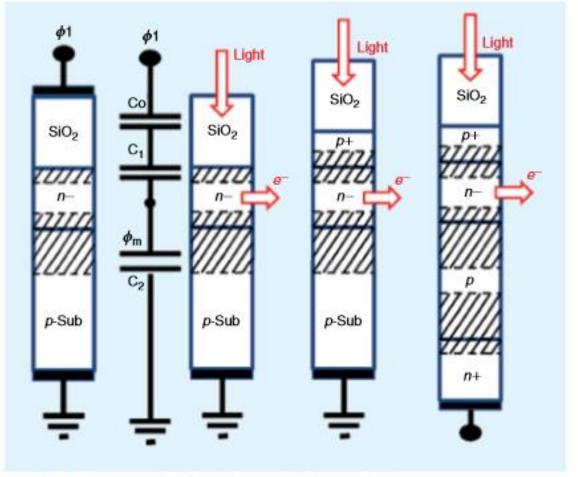

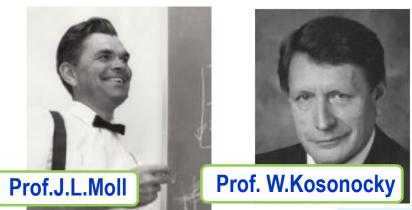

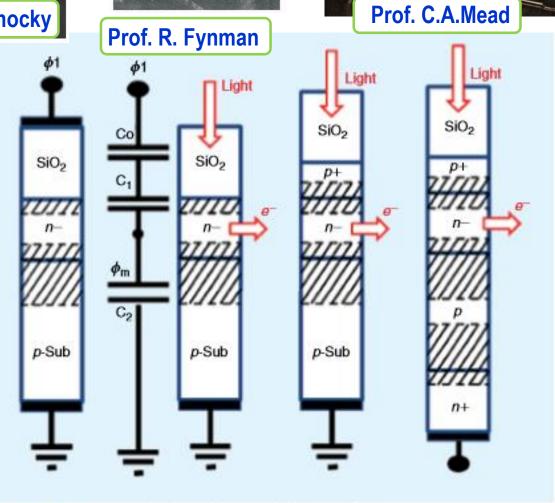

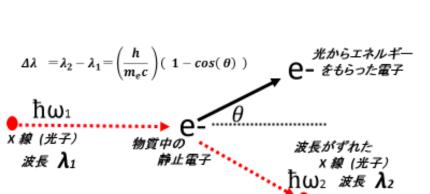

John Louis Moll (1921-2011) was studying a p-n-p-n diode switch in his Ph.D. dissertation work when the first ISSCC was held in 1954. In a normal operation mode, this device works as a thyristor, which can drive a large current and is the key device structure of an IGBT applied for a linear motor car of the future (see Figure 9). In a dynamic operation mode, this device may work as a simple p-n-p-n dynamic capacitance that can detect and store one single electron, which is a key device structure of the modern image sensor (see Figure 10).

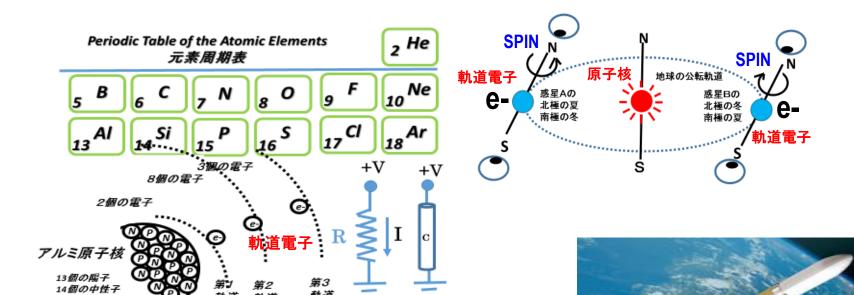

I recall, when I was taking his physics course at Caltech, that Feynman once said that an electron is always free, moving around rapidly in free space, even in solid, and it

FIGURE 9: The p-n-p-n switch diode for a modern linear motor car.

Yoshi Hagihara, Eric Vittoz and Bob Brodersen.

never stops. It is very hard to catch an electron because we do not know exactly where it is. Our civilization today is based on a technology that controls electrons, down to a single one.

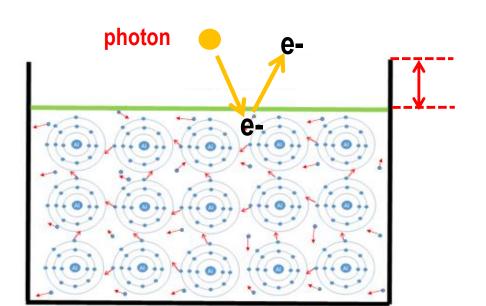

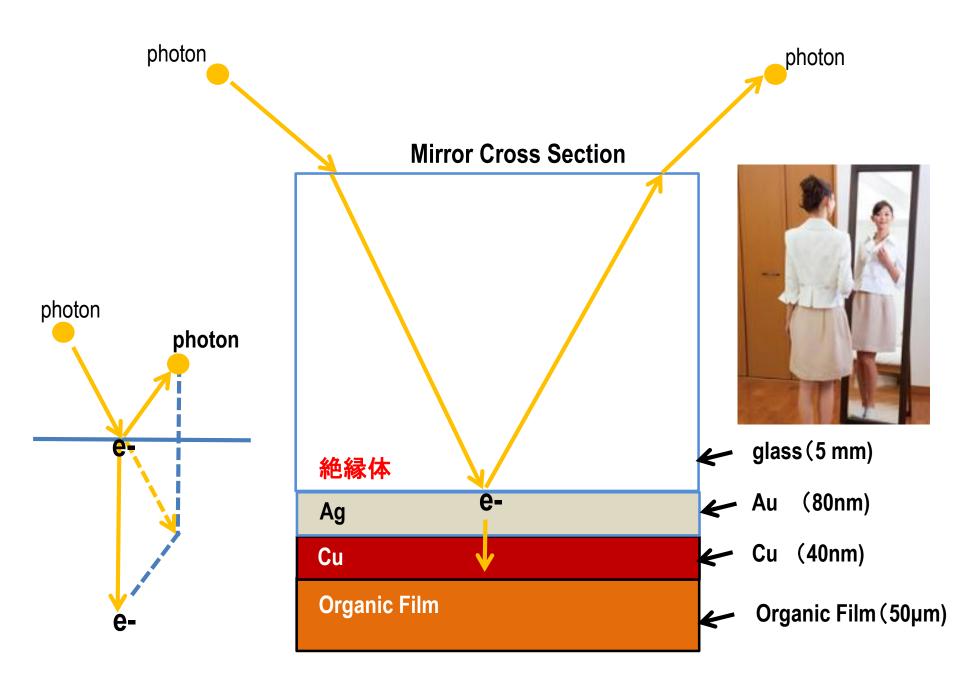

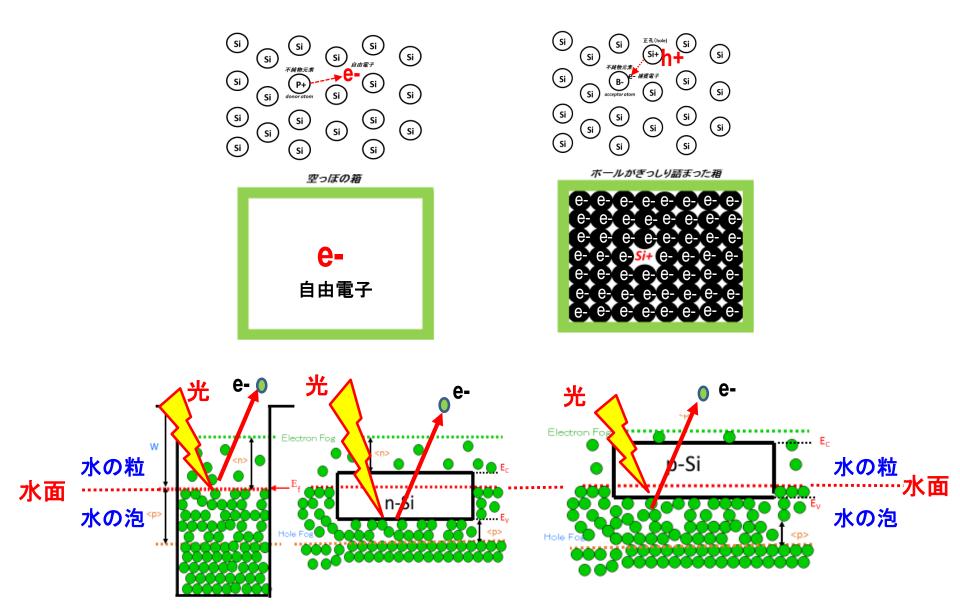

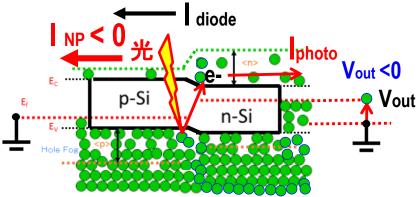

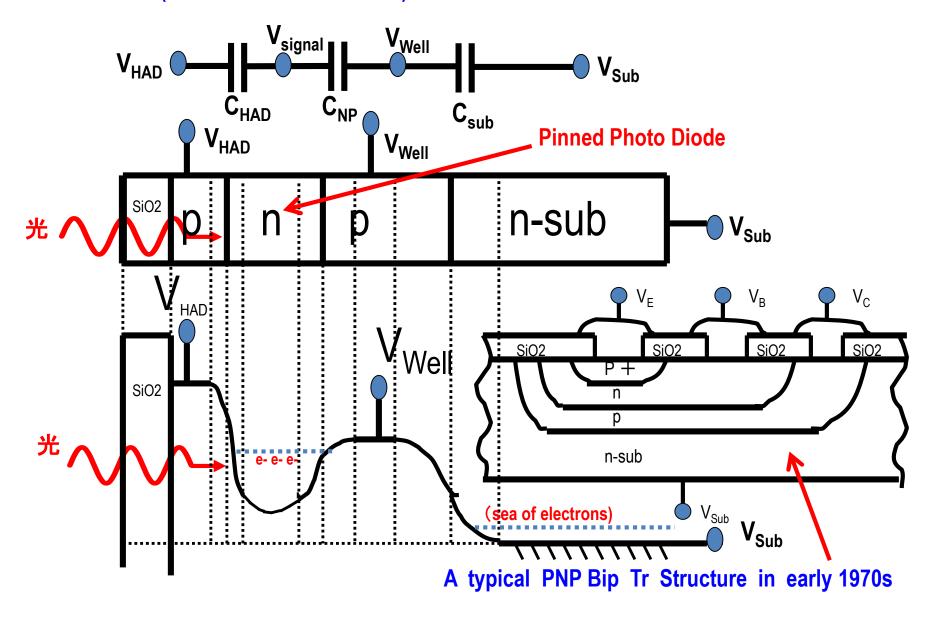

Imagine a photon incident to a bipolar transistor base region. The photon energy creates an electronhole pair. And the photo-electron can be stored in the base region as one single majority carrier. That is, a bipolar transistor can also function as a photon detector and/or a storage container. I thought that a room in a hotel must be empty and clean before the first hotel guest arrives. So must be this transistor base region empty and clean with no guest electrons at the beginning. This transistor in a dynamic p-n-p capacitor mode is useful since it can capture, confine, and control one single electron. But as a Yoshiaki Hagihara shared his memories of Richard Feynman, his mentor and educator at Caltech, and how he learned from him that control of electrons is at the heart of all electronic devices. As an example from his attic, he pointed to the old p-n-p-n junctions that are now incorporated in modern-day image sensors.

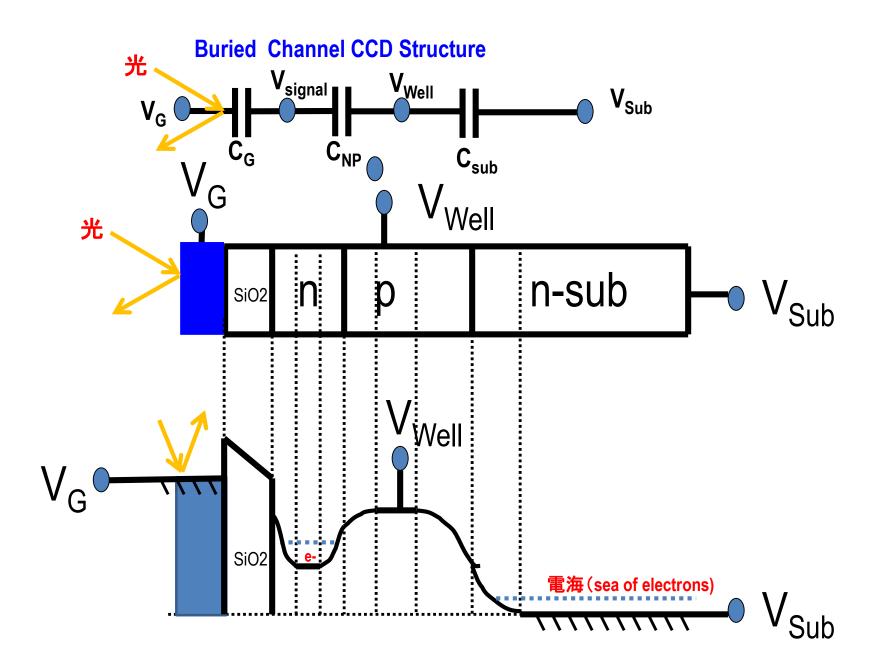

FIGURE 10: From CCD to the dynamic p-n-p-n diode capacitors.

student, I did not know yet how to move that single photoelectron sitting in the base region to the outside world so that we can make use of it as a signal. I had no way yet to know whether the hotel guest has arrived and is resting in the hotel room or not. We had no way yet to ask the hotel guest to come up to the hotel lobby to meet me. I had to wait a few more years (until 1970 in my senior year in college) to find the answer. We all know now it is the CCD structure that can store and transfer one single electron. With a precharge reset set gate and a source-follower circuit, a scheme invented by Walter Kosonocky. We could finally meet our hotel guest at the hotel lobby.

FIGURE 10: From CCD to the dynamic p-n-p-n diode capacitors.

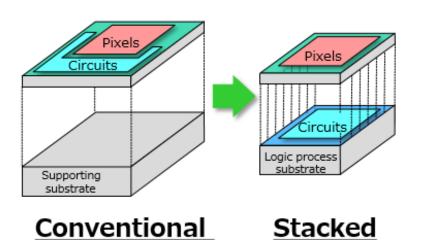

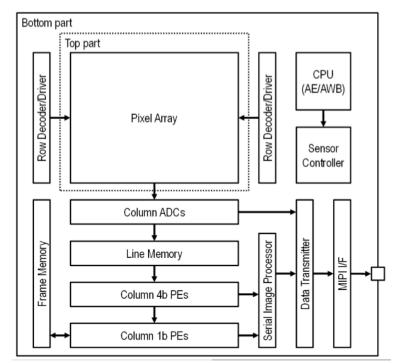

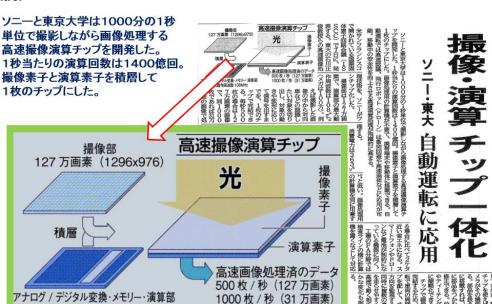

#### ISSCC 2017 / SESSION 4 / IMAGERS / 4.9

#### 4.9 A 1ms High-Speed Vision Chip with 3D-Stacked 140GOPS Column-Parallel PEs for Spatio-Temporal Image Processing

Tomohiro Yamazaki¹, Hironobu Katayama¹, Shuji Uehara¹, Atsushi Nose¹, Masatsugu Kobayashi¹, Sayaka Shida¹, Masaki Odahara², Kenichi Takamiya², Yasuaki Hisamatsu², Shizunori Matsumoto², Leo Miyashita³, Yoshihiro Watanabe³, Takashi Izawa¹, Yoshinori Muramatsu¹, Masatoshi Ishikawa³

<sup>1</sup>Sony Semiconductor Solutions, Atsugi, Japan

<sup>2</sup>Sony LSI Design, Atsugi, Japan

<sup>3</sup>University of Tokyo, Bunkyo, Japan

High-speed vision systems that combine high-frame-rate imaging and highly parallel signal processing enable instantaneous visual feedback to rapidly control machines over human-visual-recognition speeds.

最大動作周波数 108MHz

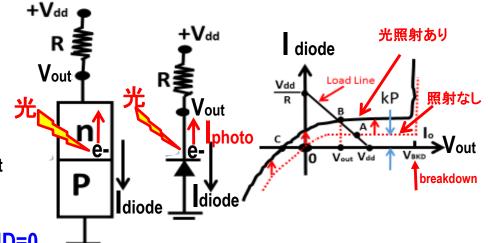

#### 2枚のchipを張り合わせる (信号処理専用) CMOS 回路用 substrate **Top Chip** SiO2 張り合わせ Metal Contact SiO2 P+ P+ P+ P+ 動作 mode ③ Vin **Bottom Chip** h+ (受光素子専用) Vdd GND Vout SiO2 N (sat) (sat)

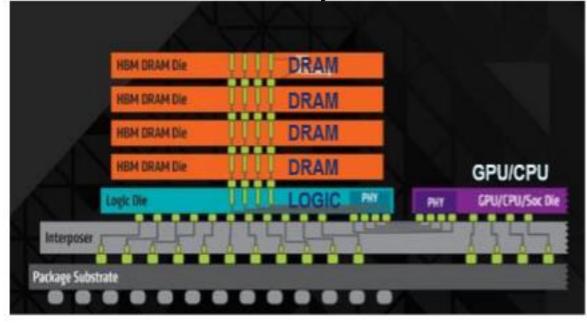

### **Next Generation Memory**

|       | FeRAM             | MRAM             | STT-MRAM         | PRAM                             | ReRAM           |

|-------|-------------------|------------------|------------------|----------------------------------|-----------------|

| 信号比   | 10                | 1                | 6                | 100                              | 10,000          |

| 微細化   | ×⇒○               | ×                | 0                | 0                                | 0               |

| 読み出し  | 破壊                | 非破壊              | 非破壊              | 非破壊                              | 非破壊             |

| 書換寿命  | 10 <sup>12</sup>  | 10 <sup>16</sup> | 10 <sup>16</sup> | 10 <sup>12</sup>                 | >106            |

| 書込時間  | 50n∼100ns         | 10ns             | <10ns            | >30ns                            | <10ns           |

| セルサイズ | ~15F <sup>2</sup> | ~8F <sup>2</sup> | ~8F <sup>2</sup> | 4F <sup>2</sup> ~6F <sup>2</sup> | 4F <sup>2</sup> |

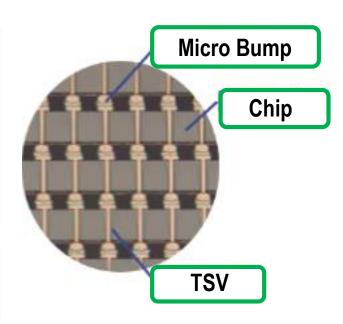

3D memory stack

**TSV=through Silicon Via**

第2 軌道

第3 軌道

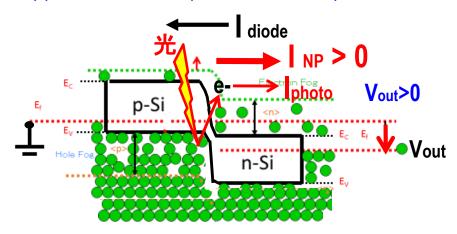

### (1)電源電圧 Vdd<0 (順バイアス mode) の場合

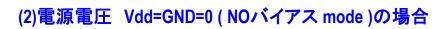

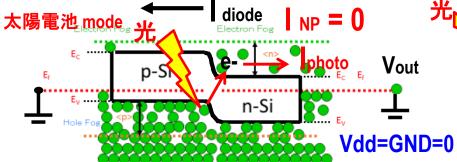

#### (3)電源電圧 Vdd>0 (逆バイアス mode )の場合

光を照射すると電流が流れる!

1971 Intel 1101 256bit RAM

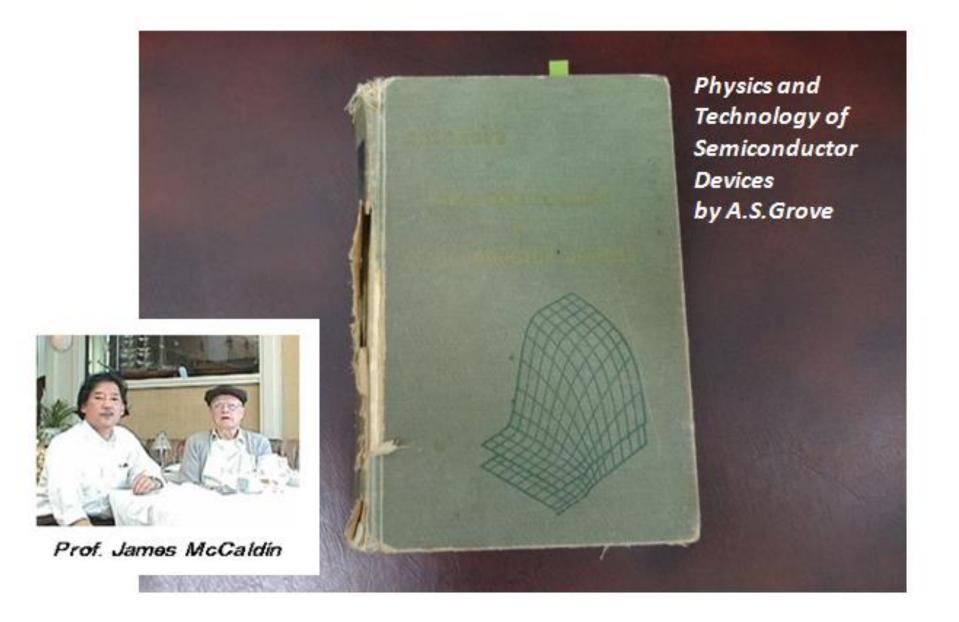

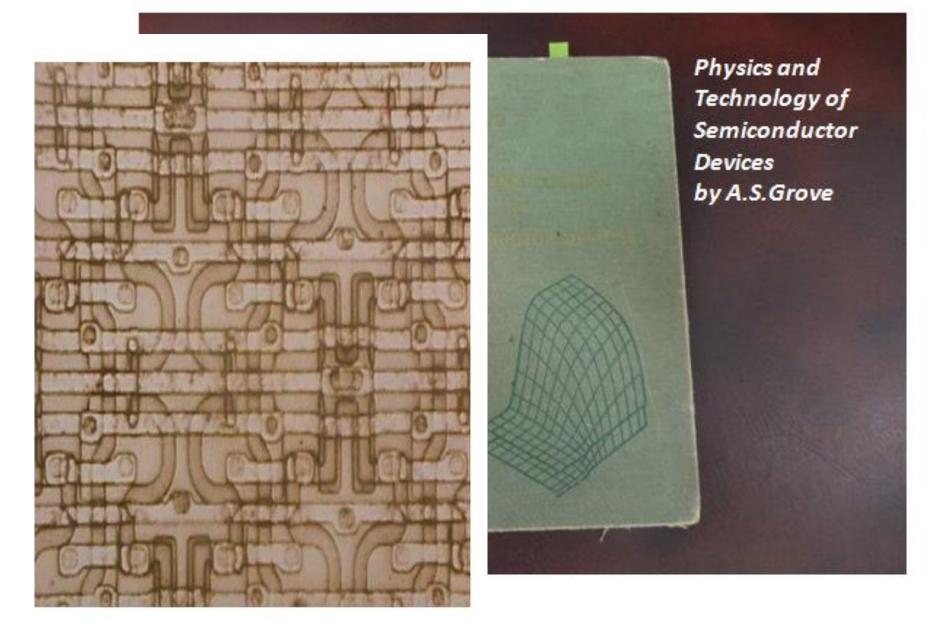

Physics and Technology of Semiconductor Devices by A.S. Grove

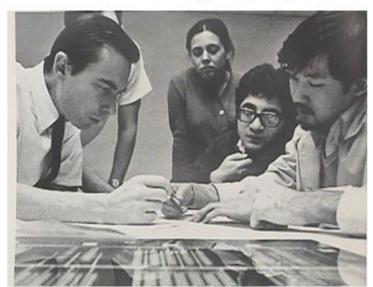

Prof.CA Mead and myself, Sept 1972

1971 Intel 1101 256bit RAM

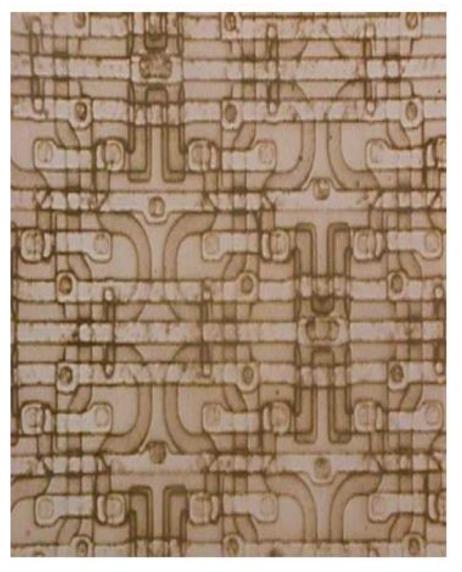

#### 128 bit data comparator chip designed by CalTech and fabricated in Intel, 1972.

#### 128-Bit Multicomparator

CARVER A. MEAD, RICHARD D. PASHLEY, MEMBER, IEEE, LEE D. BRITTON, YOSHIAKI T. DAIMON, AND STEWART F. SANDO, JR., MEMBER, IEEE

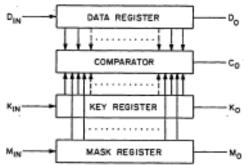

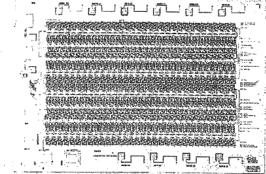

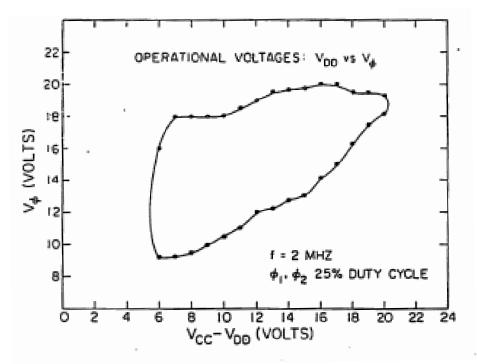

Abstract—A 128-bit multicomparator was designed to perform the search-sort function on arbitrary length data strings. Devices can be cascaded for longer block lengths or paralleled for bit-parallel, word-serial applications. The circuit utilizes a 3-phase static-dynamic shift register cell for data handling and a unique gated exclusive-non circuit to accomplish the compare function. The compare operation is performed bit parallel between a "data" register and a "key" register with a third "mask" register containing pon't care bits that disable the comparator. The multicomparator was fabricated using p-channel silicongate metal-oxide-semiconductor (MOS) technology on a 107 × 150 mil chip containing 3350 devices. With transistor-transistor logic (TTL) input, data rates in excess of 2 MHz have been attained. The average power dissipation was 250 mW in the dynamic mode and 300 mW in the static mode.

Fig. 1. Block diagram of multicomparator.

#### Prof.CA Mead and myself, Sept 1972

Prof. T. C. McGill

### Charge-Coupled Devices and Applications

Chairman

Lewis M. Terman

Testimonial to the importance of the charge-transfer phenomenon is attested to by the Morris N. Liebmann and the David A. Sarnoff awards this year to the originators of the charge-coupled and bucket-brigade devices, respectively. The papers in this session concentrate on the former.

### ISSCC1974 PhD Student Paper on buried channel CCD

#### HAD (hole accumulated diode) sensor

mannan Jana

## <ICX008> 2/3 Inch 120K Pixcel IT CCD Imager designed

PlayStation-3

PS3 の Cell Processor の 微細化によるハード ウエアーのコスト低減効果 と初期投資の回収:

この電子部品の中身 Hardwareを調査研究: Computer の構造とその アーキテクチャーを学習。

比較対象: 2005年モデルPS3

問題点と改良点についてまとめる。

Cell B.E. 90nm, 65nm, 45nm

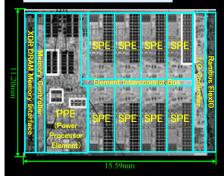

90nm Cell B.E.

90nm Area 235.48mm2 100% W 19.17mm H 12.29mm SPE 14.76mm2 PPE 26.86mm2

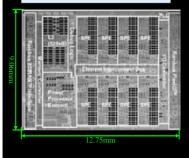

65nm Cell B.E.

65nm Area 174.61mm2 74.2% W 15.59mm H 11.20mm SPE 11.08mm2

PPE 19.60mm2

45nm Cell B.E.

45nm Area 115.46mm2 49%

W 12.75mm H 9.06mm SPE 6.47mm2 PPE 11.32mm2

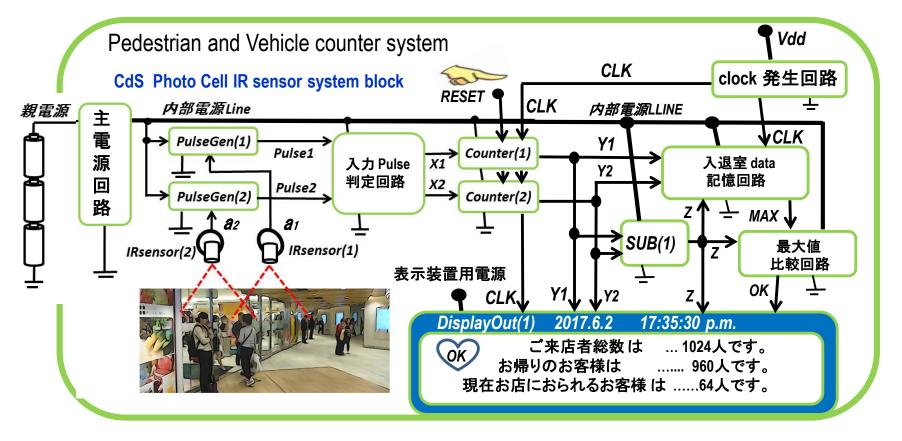

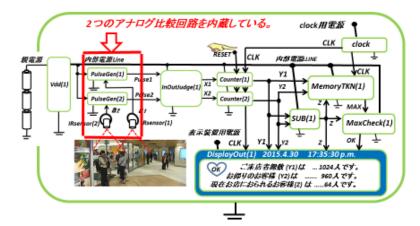

街中での通行人の映像

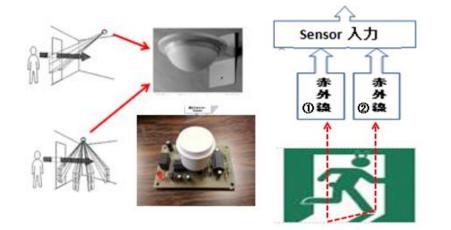

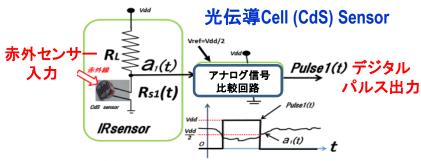

#### 光伝導Cell (CdS) Sensor System 例

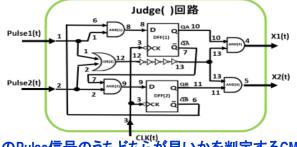

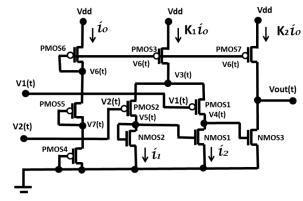

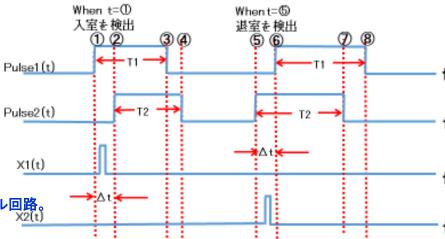

#### 相対Pulse遅延判定回路

2つのPulse信号のうちどちらが早いかを判定するCMOSデジタル回路。 X2(t)

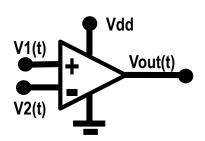

#### アナログ信号比較回路 (単純な1bit の A/D変換器)

#### CMOS回路で構成されたアナログ信号比較回路

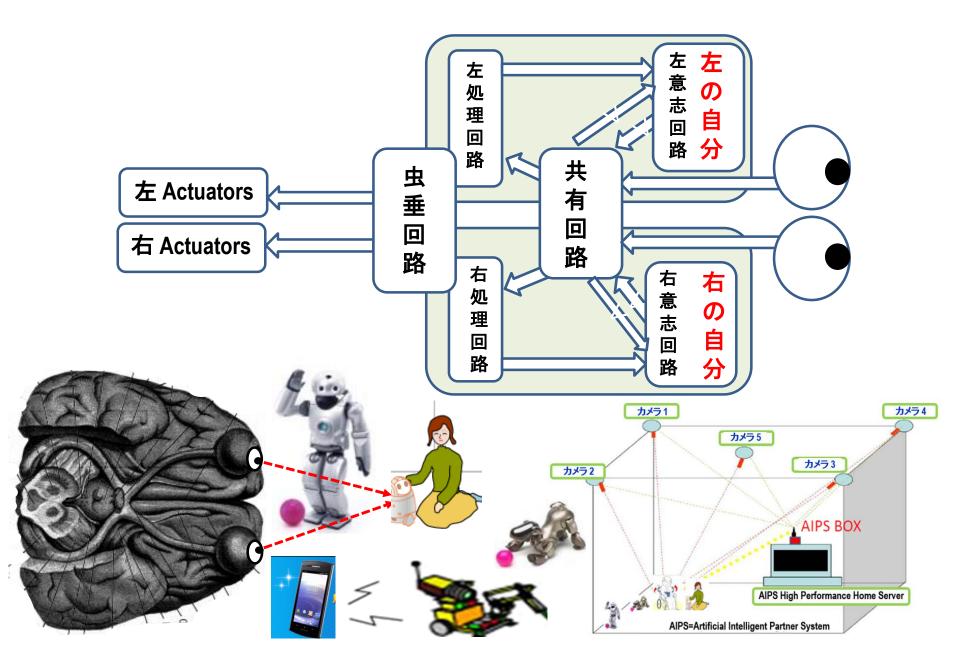

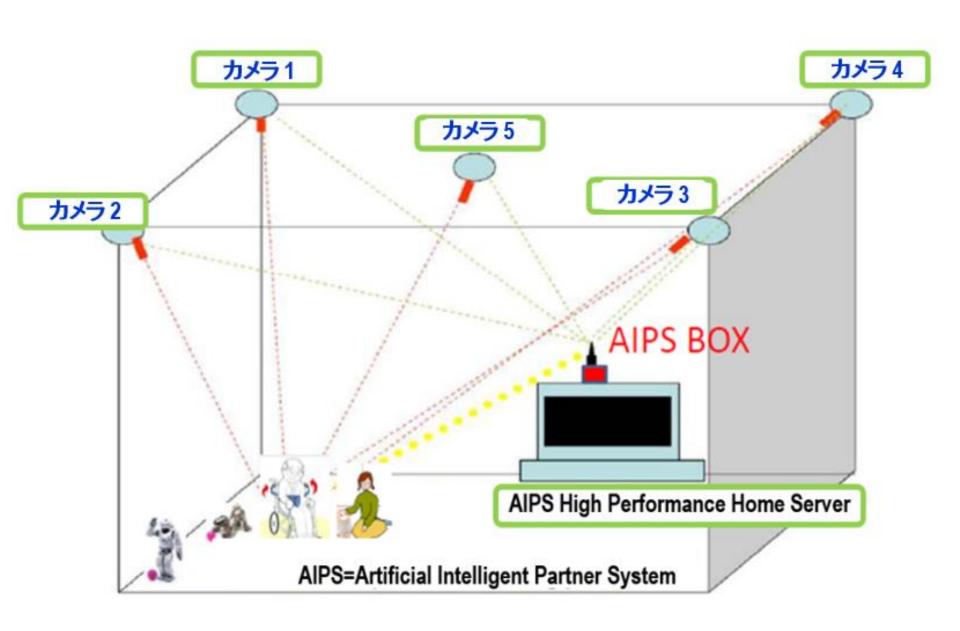

see http://www.aiplab.com /

#### 2013年3月25日 午後4時 フジテレビ全国NETで放送