Charge Transfer in Charge Coupled Devices

## Thesis by Yoshiaki Daimon-Hagihara

In Partial Fulfillment of the Requirement

for the Degree of

Doctor of Philosophy

California Institute of Technology

Pasadena California 91125

# To Tomié and Akinori

### iii

### ACKNOWLEDGEMENTS

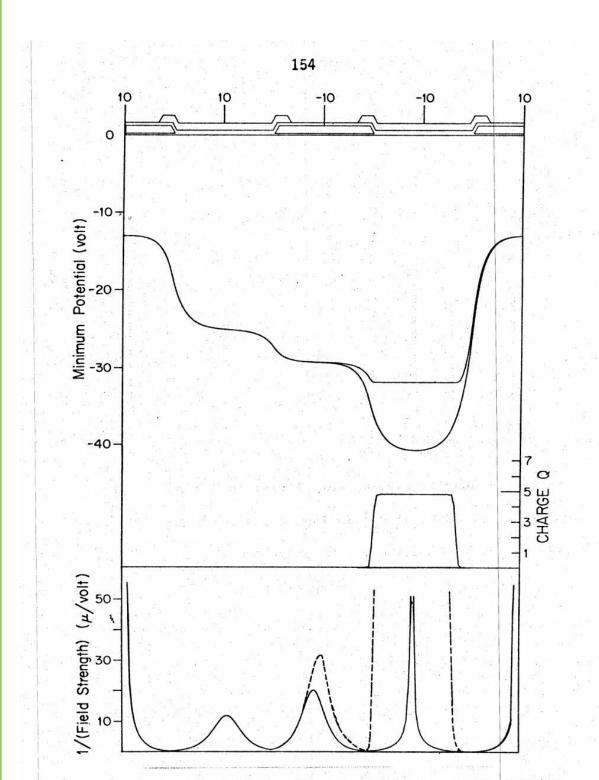

The author expresses his deepest gratitude to Dr. T. C. McGill for his guidance with enduring patience. Special appreciations go to Dr. C. A. Mead for exciting discussions and valuable insight, Dr. F. B. Humphrey for critical reviews and valuable suggestions which have greatly improved the readability of this thesis, and Dr. A. M. Mohsen for discussions during the initiation of this work. Grateful thanks are due to Mrs. Kathy Ellison for typing and preparing manuscripts for publication.

The work reported here was supported in part by the Office of Naval Research and the Naval Research Laboratory. The financial assistance at the California Institute of Technology in the form of several research and teaching assistanships and tuition scholarships is gratefully acknowledged.

## iv

### ABSTRACT

Theoretical analysis of the dynamics of charge transfer in charge coupled devices is central to the intelligent design and proper estimation of the usefulness of this new device concept. In this report, a detailed study of the electrostatics and dynamics of buried channel charge coupled devices (BCCDs) is presented. Both theoretical and experimental study of BCCD has been very difficult due to the additional complexity in the BCCD structure in contrast to the original simpler structure of surface charge coupled devices (SCCDs). And up to present, no comprehensive study of BCCD which includes the complete electrostatic and dynamic analysis of BCCD operations has been reported. It is the purpose of this thesis to assist physicists, device engineers, and applications engineers interested in BCCD by presenting all essential information on the buried channel CCDs in one place and in a comprehensive form so that the background layed on BCCD can be applied immediately to the case of the SCCD studies achieved in the past and also to the investigation of a future CCD structure.

The work reported in this thesis consists of three major contributions to the rapidly progressing CCD research and is described in the main text, Chapter 1, 4, and 5 of this thesis.

In Chapter 1 the relations between the electrostatic potential and the charge distribution in one dimensional structure for BCCD are analyzed in detail. An expression for the channel potential in terms of salient physical parameters is obtained by depletion approximation. And its implications on doping levels, and profiles; charge storage capa-

V

## **ABSTRACT**

city; geometrical structure and gate voltages are discussed in detail to provide a useful reference and guide-work in design and analysis of buried channel CCDs. The results obtained numerically for the case of Gaussian doping profile are also presented and correlated with the uniform doping model. In Chapter 4 a detailed two dimensional electrostatic analysis of buried channel CCDs is presented. By a simple capacitance network model the two dimensional Poisson equation appropriate for the structure is reduce into a second order differential equation in a single spatial dimension. The resulting equation relates the signal charge and the minimum channel potential under all the relevant electrodes and interelectrode regions. A diffusion equation describing the charge transfer is coupled to this equation in order to incorporate the static model in dynamic charge transfer description. The results of a detailed numerical simulation of the charge transfer process in the resulting realistic model of a high density buried channel CCD to be studied in Chapter 5. It is shown that the limitations remain on the device performance due to incomplete free charge transfer are reduced considerably by powerful field-aided charge transfer. The procedure to estimate the significance of this reduction in terms of the charge remaining as a function of time is formulated analytically.

## TABLE OF CONTENTS

|                |                                                     | Page    |

|----------------|-----------------------------------------------------|---------|

| ACKNOWLEDGEMEN |                                                     | iii     |

| ABSTRACT       |                                                     | iv      |

| Chapter 1      | ELECTROSTATIC ANALYSIS OF BASIC ONE DIMENSIONAL     |         |

| Onepte: -      | MOS STRUCTURE FOR BURIED CHANNEL CCDs               |         |

|                | 1.0 Introduction to Charge Coupled Devices          | 1       |

|                | 1.1 Introduction                                    | 9       |

|                | 1.2 Electrostatic Potential and Charge Distribution | 11      |

|                | 1.3 Depletion Approximation                         | 17      |

|                | 1.4 Interpretation and Results of Depletion         | * * *** |

|                | Approximation                                       | 26      |

|                | 1.5 Constraints on Gate Voltage and Signal Charge   | 37      |

|                | 1.6 Device Capacitance                              | 43      |

|                | 1.7 Gaussian Doping Profile                         | 52      |

|                | 1.8 Conclusion                                      | 64      |

| Chapter 2      | APPENDIX I : Final Stage of the Charge Transfer     |         |

|                | Process in Charge Coupled Devices                   | 68      |

| Chapter 3      | APPENDIX II : Influence of Interface States on      |         |

| Ollapso        | Incomplete Charge Trasfer in Overlapping Gate CCDs  | 76      |

| Chapter 4      | TWO DIMENSIONAL ELECTROSTATIC ANALYSIS OF           |         |

|                | BURIED CHANNEL CHARGE COUPLED DEVICES               |         |

|                | 4.1 Introduction                                    | 91      |

|                | 4.2 Basic One Dimensional MOS Structure             | 93      |

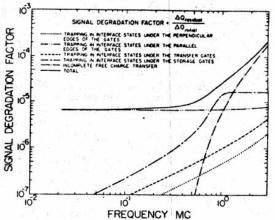

|                | 4.3 Surface FET with Metalurgical Channel           | 97      |

# TABLE OF CONTENTS

|           |      |                                                  | Page |

|-----------|------|--------------------------------------------------|------|

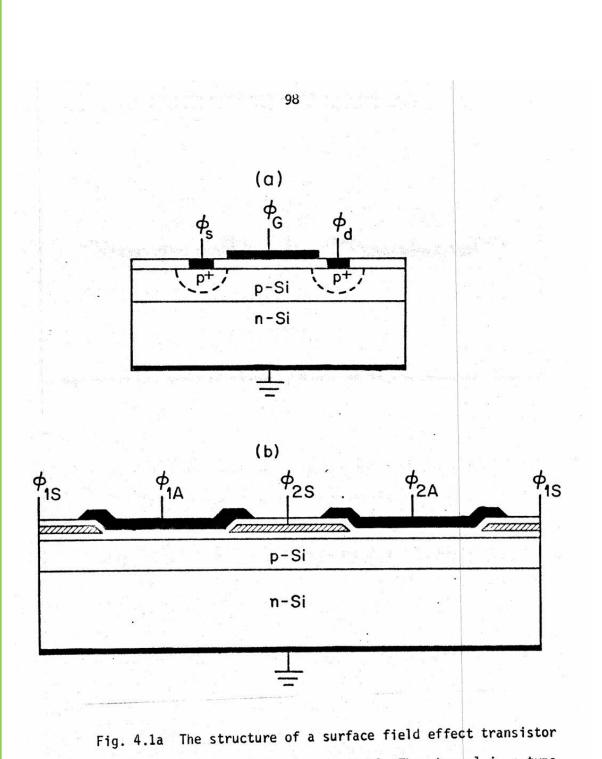

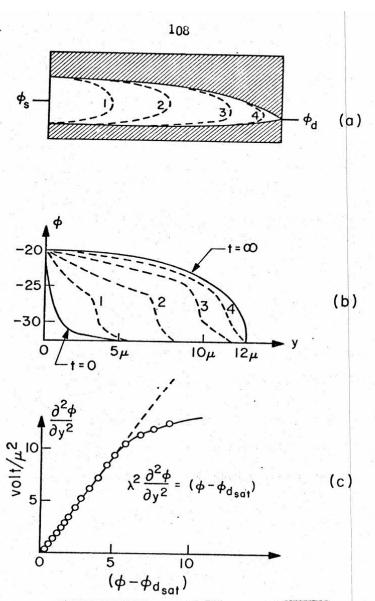

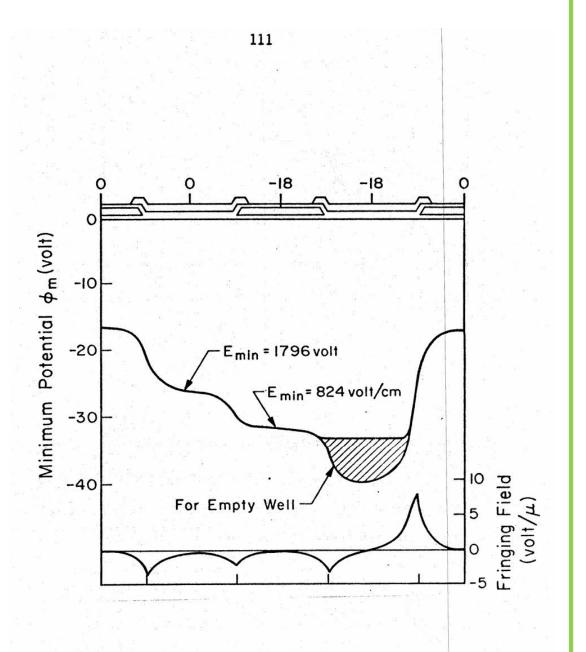

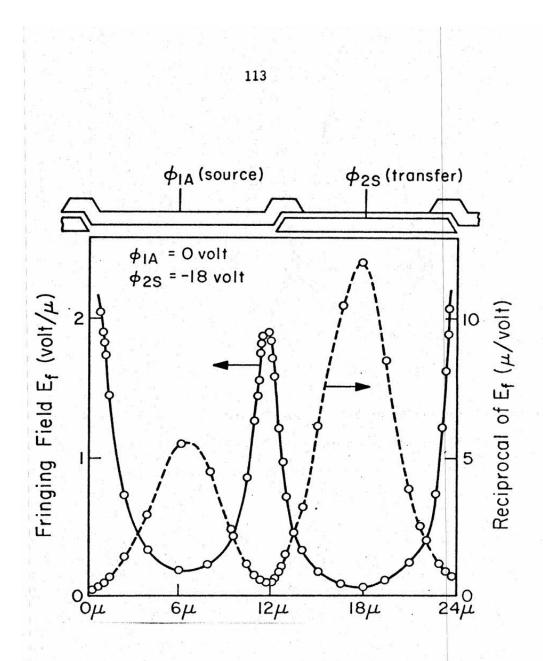

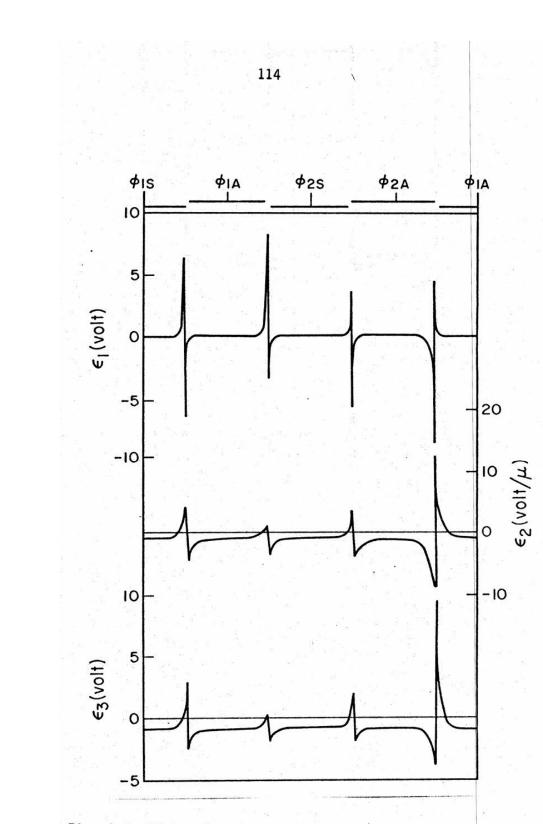

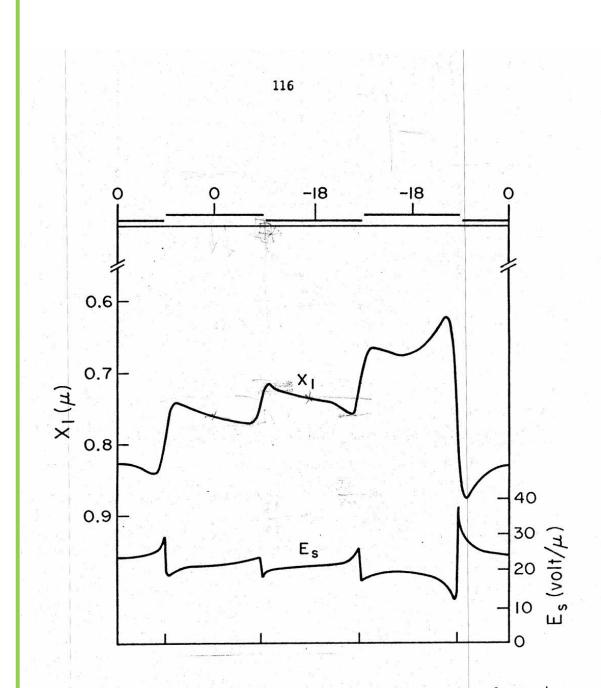

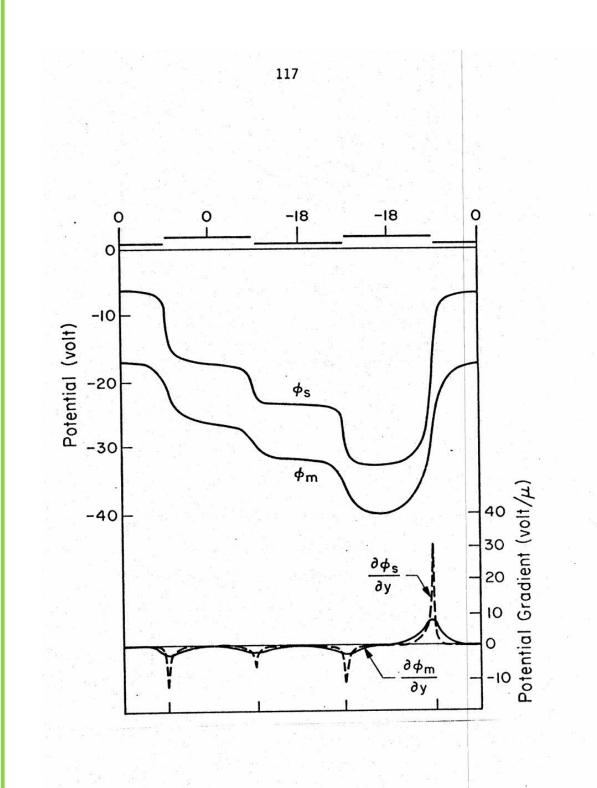

|           | 4.4  | Minimum Potential Profile in Buried Channel CCD  | 109  |

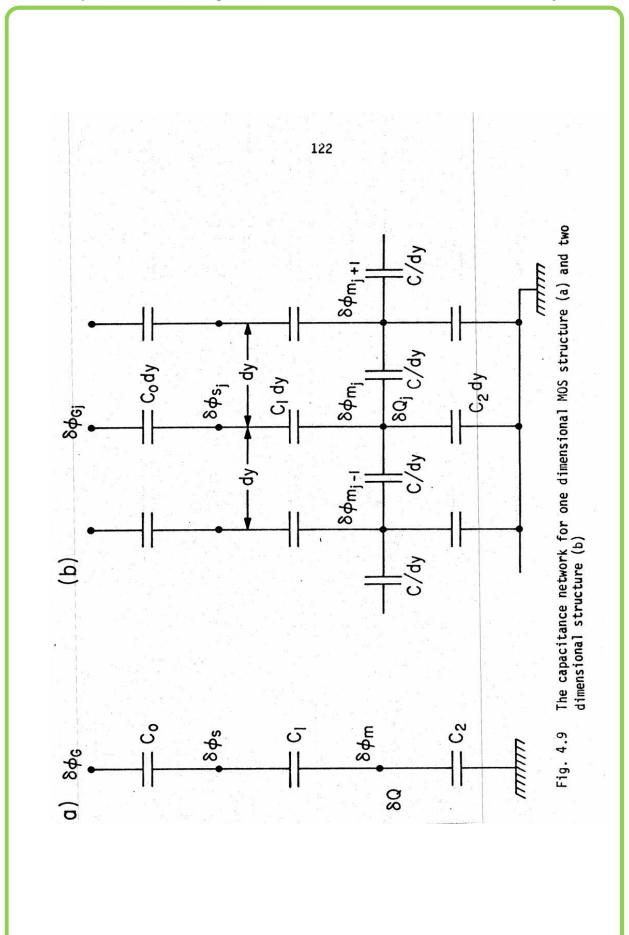

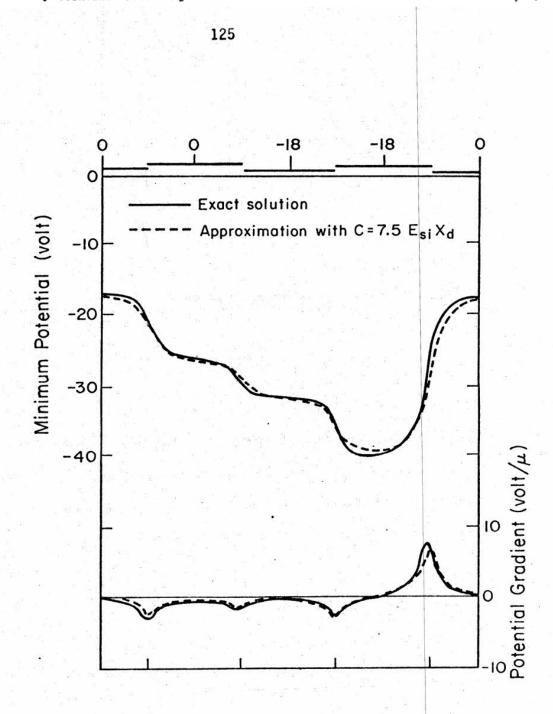

|           | 4.5  | Capacitance Network Model for BCCD               | 121  |

|           | 4.6  | Dynamic Charge Transfer Model                    | 131  |

|           | 4.7  | Conclusion                                       | 133  |

| Chapter 5 | FREE | CHARGE TRANSFER IN BURIED CHANNEL CHARGE         |      |

|           | COUP | LED DEVICES                                      |      |

|           | 5.1  | Introduction                                     | 134  |

|           | 5.2  | Transport Equation                               | 139  |

|           | 5.3  | Self-Induced Drift Effect in the First Stage     | 141  |

|           | 5.4  | Buried Channel IGFET in the Begining of          |      |

|           |      | the Second Stage                                 | 147  |

|           | 5.5  | Lumped Circuit Model in the Second Stage         | 149  |

|           | 5.6  | The Exponential Decay Characteristics in         |      |

|           |      | the Final Stage                                  | 162  |

|           | 5.7  | Numerical Results                                | 167  |

|           | 5.8  | Conclusion                                       | 170  |

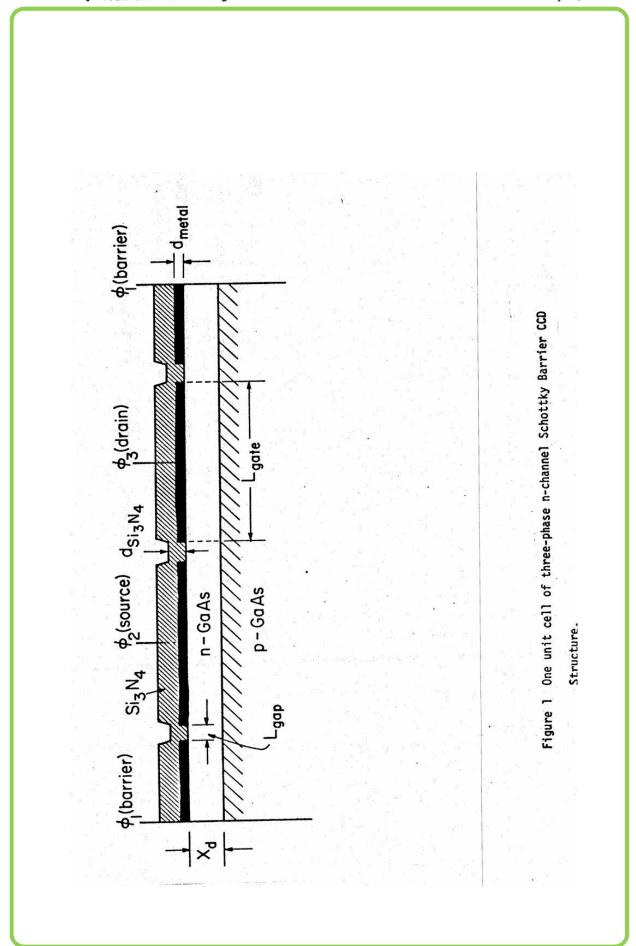

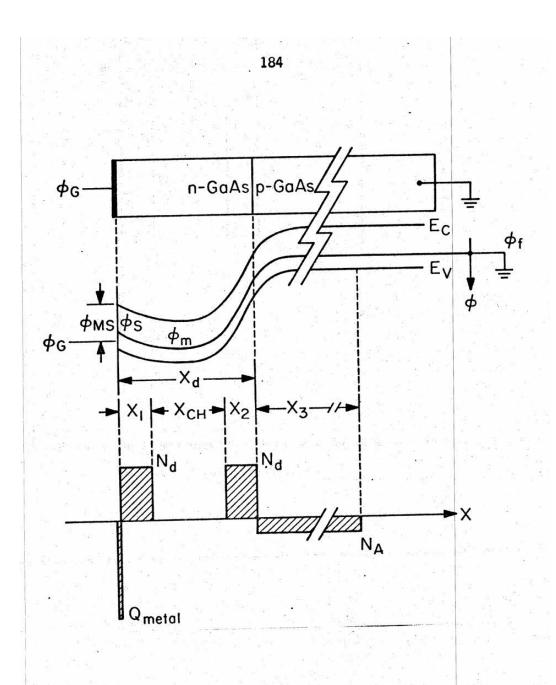

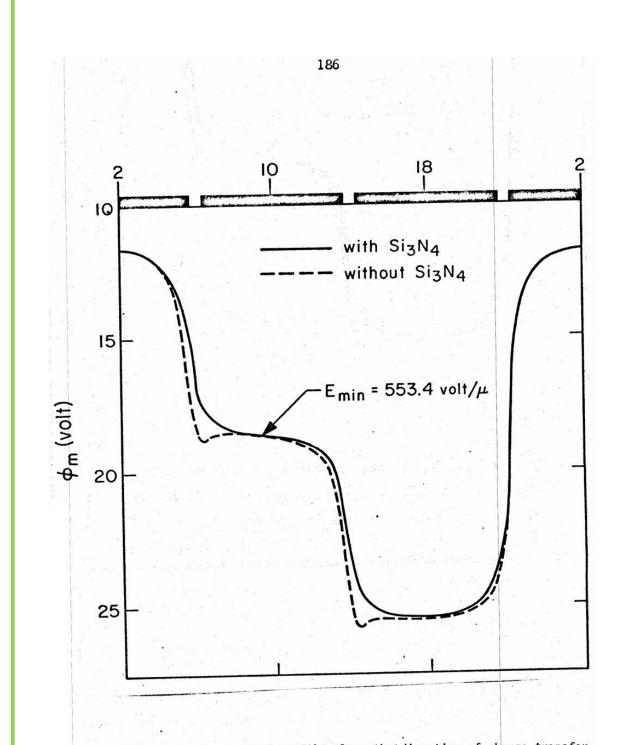

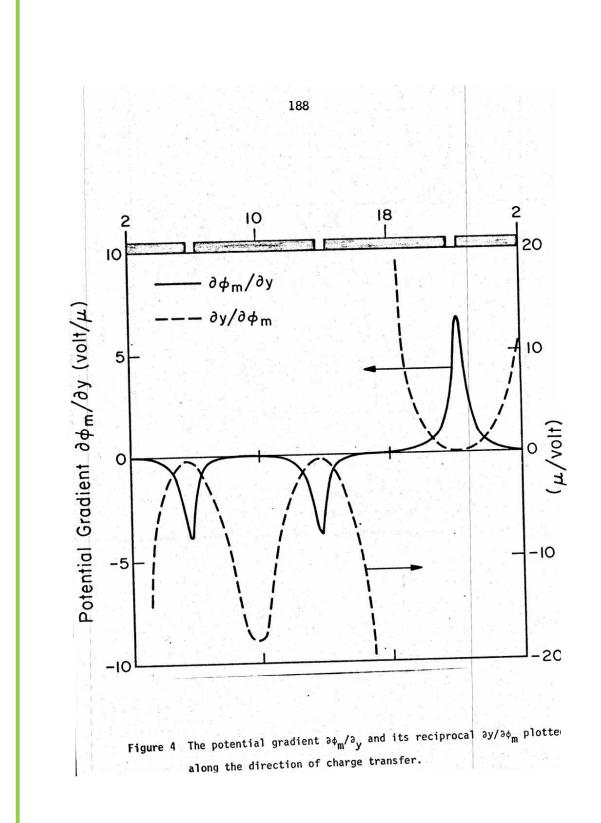

| Chapter 6 | APPE | NDIX III : Electrostatic Analysis of GaAs Buried |      |

|           | Char | mel Charge Coupled Devices with Schottky Barrier | 180  |

#### Chapter 1

## ELECTROSTATIC ANALYSIS OF BASIC ONE DIMENSIONAL MOS STRUCTURE FOR BURIED CHANNEL CCDs

### 1.0 Introduction to Charge Coupled Devices

In 1970, Boyle and Smith in Bell Labs showed that a signal charge packet in a metal-oxide-semiconductor (MOS) structure could be stored in a potential well under a depletion-biased metal electrode and moved from under one electrode to the next by appropriate pulsing of the electrode potentials. For the structure to be used as a signal processing device, the electrodes must be placed close enough to make the potential wells couple and the signal charge packets move smoothly from one well to the next. The resulting structure is commonly known as the charge coupled device (CCD).

In the past few years there have been tremendous advances in the fabrication of this new class of semiconductor devices. These advances, occuring in an already sophiscated technology, were made possible by earlier parallel developments in the parent field of large scale integrated circuits.

Analog-signal-processing developments in CCDs have been very significant, for the first time bringing the full impact of monolithic integrated-circuit technology to bear on sophisticated analog communi-

<sup>\*</sup> Boyle, W. S., and Smith, G. E. "Charge Coupled Semiconductor Devices," B.S.T.J., 49, No.4 (April 1970), pp.587-593

cation systems. CCD delay-line, multiplexing and filtering components are by now operating in developmental systems, where they provide such complex and vital signal-processing operations as matched filtering in spread-spectrum communication, bandpass and low- pass filtering, Hilbert and Fourier transforms for single-side band modulation and complex coding for military communications. However, most significant of all their commercial implications are CCD memory systems. Here progress has been slow, mostly due to the already high level of bipolar and MOS memory technology and the fact that CCD memories, owing to their charge-transfer process, are basically serial. Nevertheless, CCD memories have been gaining momentum. The first to arrive is 16,000- to 32,000-bit serial CCD memory element capable of operating at respectable 1- to 5-megahertz kilobits on a chip in the next two years, at last ushering in the age of mass-memory chip technology.

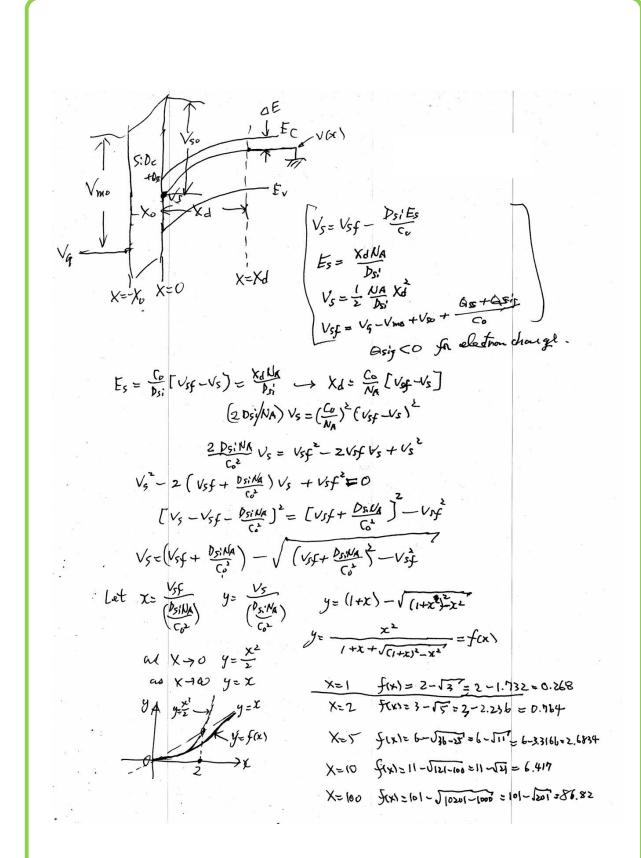

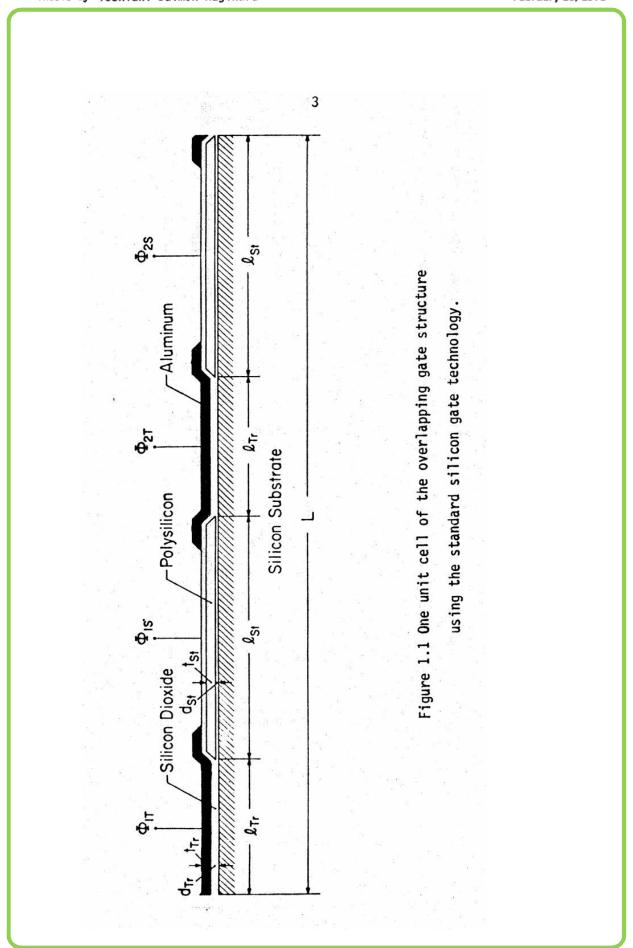

A typical two dimensional CCD structure is illustrated in Fig.1.1 as one unit cell of the overlapping gate structure using the standard silicon technology. The device is a series of simple metal-oxide-semiconductor (MOS) capacitors coupled in such a way that the signal charge on the capacitors can move from under one storage to the next. The storage site is actually a potential well created under the electrodes at the semiconductor insulator interface. In Fig. 1.2a and Fig. 1.2b the band diagram of a metal-insulator-n semiconductor is shown to illustrate the creation of potential wells at the interface when a voltage pulse is applied to the metal electrode. Minority carriers, injected in response to a digital or analog signal or generated by

photons, are stored as charge packets in these potential wells resulting in a decrease in depth of the potential well.

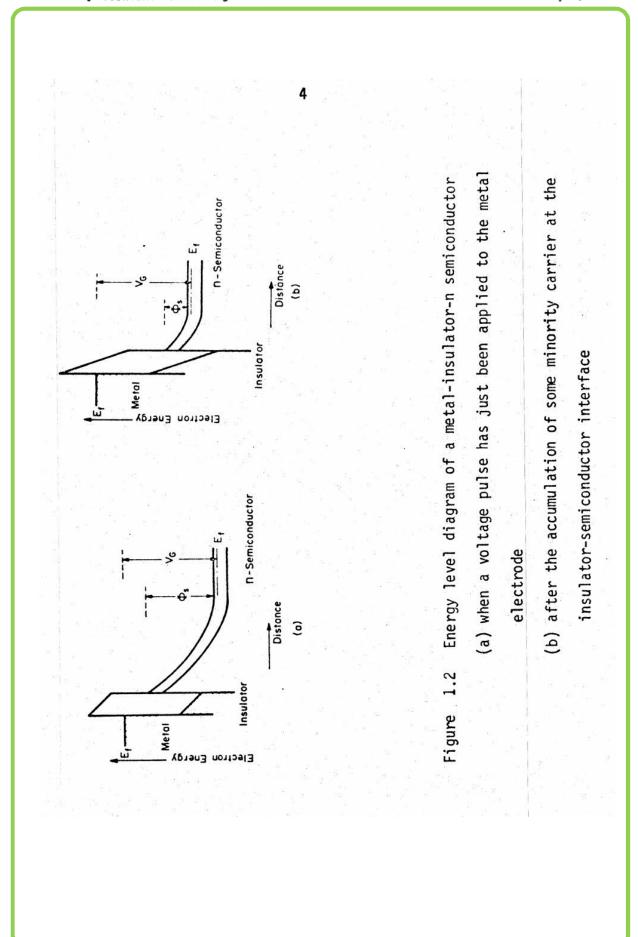

The storage and transfer of the charge packets are controlled by the clocking pulses driving the closely spaced electrodes as shown in Fig. 1.3 where a three phase clocking scheme is used. In the three phase operation three electrodes are needed to store one bit of information and obtain a directionality in the signal flow. The figures illusrate how the 4-bits information in a 1-0-1-0 pattern is transferred to the right.

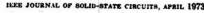

The original charge coupled device, as introduced in 1970, operates by moving minority carriers along the surface of a semiconductor with voltage pulses applied to metal electrodes which are separated from the semiconductor by an insulating layer (SiO<sub>2</sub>). Today, this type of charge coupled devices is referred as surface charge coupled devices (SCCD). The anlysis of charge-transfer characteristics of SCCD in terms of freecharge losses, (see Appendix I) and losses due to the trapping by fast interface states (see Appendix II) has been central to the intelligent design and proper estimation of the usefulness of this new device concept. In these detailed study in Appendix I and II it is shown that the transit characteristics of SCCD from one electrode to the next is determined by the minority carrier transport under the influence of thermal diffusion and electric fields due to the external electrode voltages and the selfinduced carrier repulsions. It is now known that the transport limitations are largely determined by device geometry; for long electrodes, thermal diffusion is predominantly responsible for transfering the last

small amount of charge forward and limits efficient operation to clock frequencies below 10 MHz. Surface state trapping is much less dispersive, and even at low frequencies  $10^{11}$  states/cm<sup>2</sup>-eV can impose the requirement for regeneration after as few as 100 transfers.

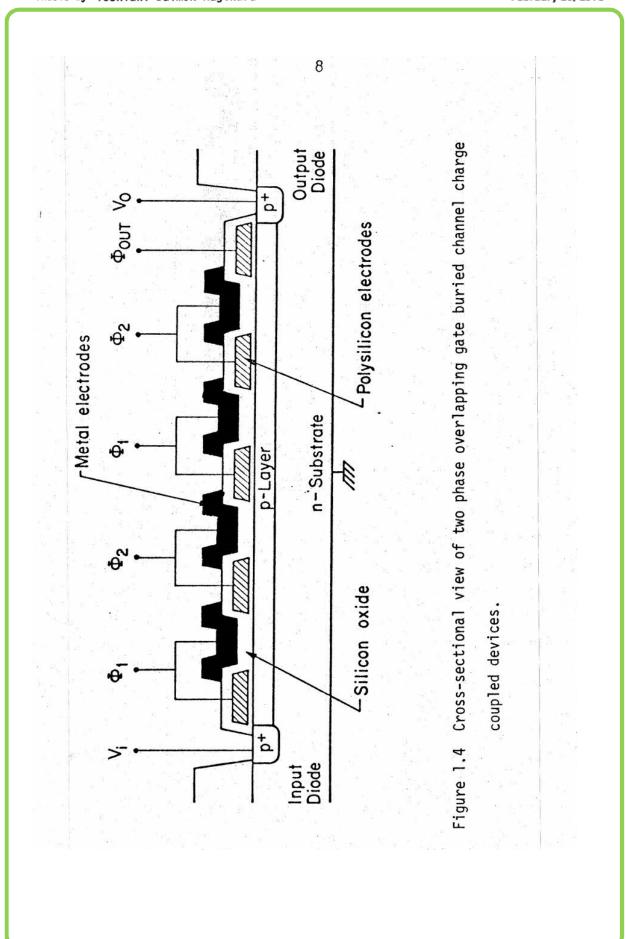

To overcome these problems in 1972, a modified CCD structure was introduced by a group of scientists\*in Bell Labs. However, due to the additional complexity in structure, the first-fabricated devices did not work at all. And further detailed experimental and theoretical investigations remained to be carried out. This new type of CCD is today referred as buried channel charge coupled devices (BCCDs) in contrast to the original surface charge coupled devices (SCCDs). The new buried channel CCD is the subject of investigation in this thesis. The crosssectional view of this BCCD is illustrated in Fig. 1.4. In this modified BCCD structure, the charge does not flow at the semiconductor surface; instead it is confined to a channel in the p-layer which lies beneath the surface. The buried channel device has the potential of eliminating surface trapping because the signal charge packets now move away from the interface. And it is also expected that this modification in structure will give rise to increased fringing fields under the electrodes and that the diffusion will be replaced by the more powerful field-aided

<sup>\*</sup> Walden, R.H., Krambeck, R.H., Strain, R.J., McKenna, J., Schryer, N.L., and Smith, G.E. "The Buried Channel Charge Coupled Devices" B.S.T.J. BRIEF, 51, No.7 (September 1972), pp.1635-1640

transfer as an important factor in the final charge transfer process.

This should lead to fast, efficient transport even when little charge remains to be transfered.

However, both the theoretical and the experimental study of BCCD devices has been very difficult due to the additional complexity in structure. Up to present, no comprehensive study of BCCD which includes the complete electrostatic and dynamic analysis of BCCD operations has been reported. It is the purpose of this thesis to assist physicists, device engineers, and applications engineers interested in BCCD. By presenting all essential information on the buried channel CCDs in one place and in a comprehensive form they can immediately apply this analysis of BCCD to the case of the SCCD studies in the past (see Appendix I and II) and also to the investigation of a future CCD structure discussed in Appendix III. With these motivations, a detailed study of the electrostatics and dynamics of this new BCCD is presented in the main text, Chapter 1, 4, and 5 of this thesis.

#### 1.1 Introduction

Electrostatics play an important role in the design of a functioning buried channel device. The connection between geometrical structure; doping levels, and profiles; charge storage capacity; gate voltages are all determined by simple electrostatic analysis. This analysis must be carried out before any consideration of the actual charge transfer process is made. In principle the electrostatic analysis could be made by solving the Poisson equation with all the relevant charge distributions and applied potentials for the correct three dimensional geometry. However, in general this would require numerical solutions which would be

both expensive to generate and difficult to use in considering the impact of varying some of the physical parameters on the performace of the device. Hence, it is desirable to idealize the actual device structure so that one can obtain an accurate but approximate analytic solution to the electrostatic problem which will indicate how all the device parameters interact.

In this chapter I take just such an approach. The charge distributions and potential under a CCD gate are assumed to be one dimensional. As we will see this approximation makes it possible to obtain interesting and very useful results for the electrostatics of the buried channel device. While these results are very useful, they are not accurate enough for our considerations of the charge transfer and we will present a numerical solution of the electrostatic problem in two dimensions in the **chapter** 4.

To be specific we will consider only a p-channel device. However, n-channel could be done in exactly the same way.

This chapter is organized according to the following format. In 1.2 the problem is set up with the definition of charge densities and relevant geometrical parameters assuming a uniform doping profile. The solution to this problem in terms of charge stored Q, gate voltage  $\phi_{\boldsymbol{G}}$ , and the potential of the buried channel  $\phi_{\boldsymbol{m}}$  are presented in 1.3 within the depletion approximation. The implication of these results in the design of buried channel CCD's is given in the following three sections 1.4, 1.5, and 1.6. The changes in these parameters brought about changing the doping profile from uniform to Gaussian in the

region near the oxide is discussed in section 1.7. Section 1.8 contains the conclusion.

### 1.2 Electrostatic Potential and Charge Distribution

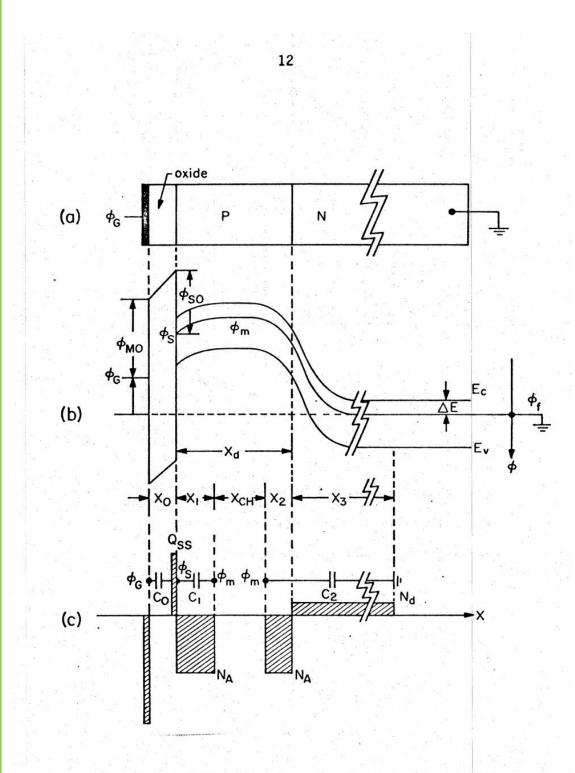

The one dimensional geometric structure for a buried p-channel charge coupled device is illustrated in Fig. 1.5a. The structure consists of a metal gate followed by a layer of silicon dioxide which rests on silicon that has been doped p-type near the surface on a n-type substrate. The potential energy versus position is shown in Fig. 1.5b. Throughout this discussion we will reference all potentials to the Fermi level in the n-type substrate. Since we will be dealing with holes throughout this problem, we will take the electrostatic potential to be positive in the standard sense, that is, the potential will increase downward on the figure. As a consequence of this definition, the position of the conduction edge ix eV is given by ΔE such that

$$\Delta E = \phi - E_{C} > 0$$

$E_V$  and  $E_C$  are the respective values of the band edges referenced to the potential zero,  $\phi$  = 0, far into the substrate. We note that  $E_C$  =  $-\Delta E$  deep in the substrate since  $\phi$  = 0. The electrostatic problem is further specified by giving various contributions to the charge density. The free carrier densities for electrons and holes are given by

$$n = N_{c} \exp \left[ \frac{E_{c} - \phi_{n}}{kT} \right] \qquad , \quad (1-1a)$$

and

Fig. 1.5 (a) MOS Structure for buried channel CCD,

(b) the band and electrostatic potential profiles, and (c) the charge distribution.

$$p = N_{V} \exp \left[ \frac{\phi_{p} - E_{V}}{kT} \right] \qquad , \qquad (1-1b)$$

where N<sub>C</sub> and N<sub>V</sub> are the effective densities of states in the conduction and valence bands, respectively; and  $\phi_n$  and  $\phi_p$  are the quasi-Fermi levels within the semiconductor.

Further we need to specify the position of the zero of potential (the Fermi level) with respect to the band edges. Using the standard results for a semiconductor doped to a level  $N_{\rm D}$ , we have of the conduction band edge  $\Delta E$ .

To accomplish this, we note that  $E_{\rm C}=-\Delta E$  deep in the substrate, and we define the intrinsic electron or hole density  $n_{\rm i}$  deep in the substrate by

$$n_i^2 = np = N_c N_v \exp\left(\frac{E_c - E_v}{kT}\right)$$

(1-2a)

Then, after a little algebra, using the relation  $N_d$  = p-n, with Eqs. (1-la) and (1-lb) we obtain the difference  $\Delta E$  in term of the substrate doping  $N_d$  as seen by

$$\Delta E = \phi_0 + kT \ln \left( \frac{N_c}{n_i} \right) \qquad (1-3a)$$

where  $\phi_0$  is defined by

$$\phi_0 = kT \ln \left[ \frac{N_d}{2n_i} + \sqrt{1 + \left(\frac{N_d}{2n_i}\right)^2} \right]$$

(1-3b)

### The derivation is as following:

We observe in Fig. 1.5b that the curves for the conduction band,  $E_c$ , and the electrostatic potential,  $\phi$ , run parallel to each other, and that

the displacement,  $\Delta E$ , is a constant quantity everywhere in the semiconductor. We calculate the value of  $\Delta E$  deep in the substrate therefore, where we observe that  $\phi_{\rm n}=\phi_{\rm p}=\phi=0$ . Hence, using the relation Nd = p-n, with Eqs. (1-la) and (1-lb) we obtain an equation which relates the conduction band  $E_{\rm C}$  and valence band  $E_{\rm V}$  deep in the substrate as seen by

$N_d = p - n = N_v \exp \left(\frac{-E_v}{kT}\right) - N_c \exp \left(\frac{E_c}{kT}\right)$

Eliminating  $E_{\rm V}$  from this equation by Eq. (1-2a), we obtain an equation for  $E_{\rm C}$  as seen by

$$\frac{N_c N_d}{n_i^2} = \exp\left(\frac{-E_c}{kT}\right) - \left(\frac{N_c}{n_i}\right)^2 \exp\left(\frac{E_c}{kT}\right)$$

Then, noting that deep in the substrate  $\Delta E = -E_C$ , this equation gives  $\Delta E$  in terms of the substrate doping  $N_d$  and the intrinsic semiconductor parameters  $N_C$  and  $n_i$  as seen in Eq. (1-3a) with  $\phi_O$  defined by Eq. (1-3b). END OF DERIVATION

This quantity  $\phi_0$  can be used to write the electron and hole densities in a symmetric form and we obtain, after some manipulation, by using Eqs. (1-1) and (1-2),

$$n = n_i \exp \left[ \frac{(\phi - \phi_0) - \phi_n}{kT} \right]$$

(1-4a)

and

$$p = n_{i} \exp \left[ \frac{\phi_{p} - (\phi - \phi_{o})}{kT} \right] \qquad (1-4b)$$

#### The derivation is as following:

From Eq. (1-3a) with  $\Delta E = \phi - E_C$  we obtain

$$kT \ln \left( \frac{N_C}{n_i} \right) = \phi - E_C - \phi_0$$

That is,

$$N_c \exp(E_c/kT) = n_i \exp\left(\frac{\phi - \phi_o}{kT}\right)$$

Including  $\phi_n$  in the both sides we obtain Eq. (1-4a) from Eq. (1-1a). If we apply Eq. (1-2a) to the above equation we obtain

$$\left(\frac{n_i^2}{N_V}\right) \exp(E_V/kT) = n_i \exp\left(\frac{\phi - \phi_o}{kT}\right)$$

This gives

$$N_{V} \exp(-E_{V}/kT) = n_{i} \exp\left(\frac{\phi_{o}-\phi}{kT}\right)$$

Including  $\phi_{\rm p}$  in the both sides we obtain Eq. (1-4b) from Eq. (1-1b). END OF DERIVATION

With these equations (1-4a) and (1-4b) for the electron and hole densities we can write the one dimensional Poisson equation as

$$\frac{d^2\phi}{dx^2} = -\frac{1}{\varepsilon_{Si}} \left[ p(\phi, \phi_p) - n(\phi, \phi_n) + d(x) \right] \qquad , \qquad (1-5)$$

where we denote the impurity doping concentration in the semiconductor by d(x), and the dependence of the hole and electron densities upon

the potential  $\phi$  and the quasi-fermi levels  $\phi_p$  and  $\phi_n$ , is indicated explicitly by means of Eq. (1-4), and we note that the impurity doping concentration d(x) is a positive quantity in the n-type substrate and negative in the p-diffusion region. Specifically, d(x) = N<sub>d</sub> deep in the substrate, but we consider the doping to be not necessarily uniform in the vicinity of the p-diffusion layer. It can be a Gaussian in particular.

When the minority carriers are neglected, the Poisson equation in the n-type substrate can be approximated by

$$\frac{d^2\phi}{dx^2} = -\frac{1}{\varepsilon_{Si}} \left[ d(x) - n(\phi, \phi_n) \right] \qquad (1-6a)$$

Correspondingly, when the electron concentration is neglected in the p-diffusion layer, we obtain

$$\frac{d^2\phi}{dx^2} = -\frac{1}{\varepsilon_{Si}} \left[ d(x) + p(\phi, \phi_p) \right] \qquad (1-6b)$$

where  $\epsilon_{\mbox{Si}}$  is the semiconductor dielectric constant.

We have now set up the problem with the definition of charge densities and relevant geometrical parameters. One more point, however, remains to be made clear before considering the implications of this problem. It is about the relation between the built-in voltage  $\phi_B$  of the p-n juntion and the minimum potential  $\phi_m$  of the potential well.

For the uniformly doped abrupt p-n junction shown in Fig. 3.1c, at the thermal equilibrium, the minimum potential  $\phi_m$  in the p-diffusion layer is equal to the built-in voltage of the p-n junction which is given by depletion approximation as

$$\phi_{B} = kT \ln \left( \frac{N_{A}N_{d}}{n_{i}^{2}} \right) \qquad (1-7)$$

However, the presence of the signal charge Q and the gate voltage  $\phi_G$  control the actual value of the minimum potential  $\phi_m$ . We will study this effect by applying depletion approximation to the one dimensional MOS structure for the uniformly doped abrupt p-n junction doping profile. That is,  $d(x)=N_{\mbox{\scriptsize d}}$  in the substrate and  $d(x)=-N_{\mbox{\scriptsize A}}$  in the p-diffusion layer. The expression for  $\phi_m$  will be obtained accordingly.

### 1.3 Depletion Approximation

We define x-coordinate along the depth of the semiconductor as indicated in Fig. 1.5c by the horizontal line. The origin of x-coordinate is taken to be at the oxide-semiconductor interface. That is, the p-diffusion region is defined as 0 < X <  $X_d$ . The problem is to obtain an expression for the minimum potential  $\phi_m$  in terms of the gate voltage  $\phi_G$  and the signal charge Q which is defined as

$$Q = N_A X_{CH} = N_A (X_d - X_1 - X_2)$$

(1-8a)

where  $N_A$  is the p-channel doping density,  $X_{CH}$  is the width of the channel,  $X_d$  the p-layer depth.  $X_l$  and  $X_l$  are the surface field and metalurgical junction depletion widths respectively. These parameters are seen in Fig. 1.5c.

Corresponding to  $X_1$  and  $X_2$ , we define the respective depletion capacitance as  $C_1 = \epsilon_{Si}/X_1$  and  $C_2 = \epsilon_{Si}/X_2$  where  $\epsilon_{Si}$  is the silicon dielectric constant.

The gate voltage  $\phi_G$  controls the surface electric field  $E_S$  at the oxide-semiconductor interface, which is related to the oxide electric field by Gauss's law. The oxide electric field is given by the potential drop across the oxide divided by the oxide thickness  $X_O$ . And the potential drop is given by the difference of the gate voltage  $\phi_G$  and the surface potential  $\phi_S$  adjusted by the metal-oxide work function  $\phi_{MO}$  and the oxide-semiconductor barrier height  $\phi_{SO}$  as illustrated in Fig. 1.5b. These simple facts lead to a relation between  $E_S$  and  $\phi_S$ .

Assuming the presence of positive interface charge  $\mathbf{Q}_{\mathbf{SS}}$ , we obtain

$$\phi_{S} = \phi_{SF} - \frac{\varepsilon_{Si}^{E}s}{C_{O}} \qquad (1-8b)$$

where  $C_{0}^{}$  is the oxide capacitance per unit area,  $\phi_{S}^{}$  the surface potential.  $\phi_{SF}^{}$  is defined by

$$\phi_{SF} = \phi_{G} - \phi_{MO} + \phi_{SO} + \frac{Q_{SS}}{C_{O}}$$

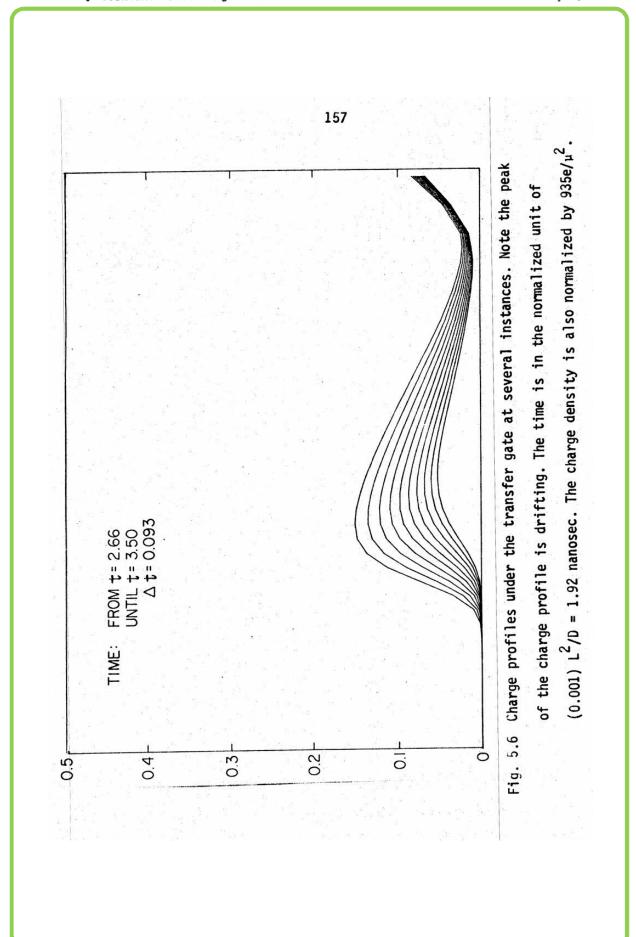

(1-8c)

We note  $\phi_{SF}$  is the surface potential when the band is flat at the interface, that is when  $E_S=0$ . Equation (1-8b) gives one boundary condition for the Poisson equation (1-6b) in the p-diffusion layer.

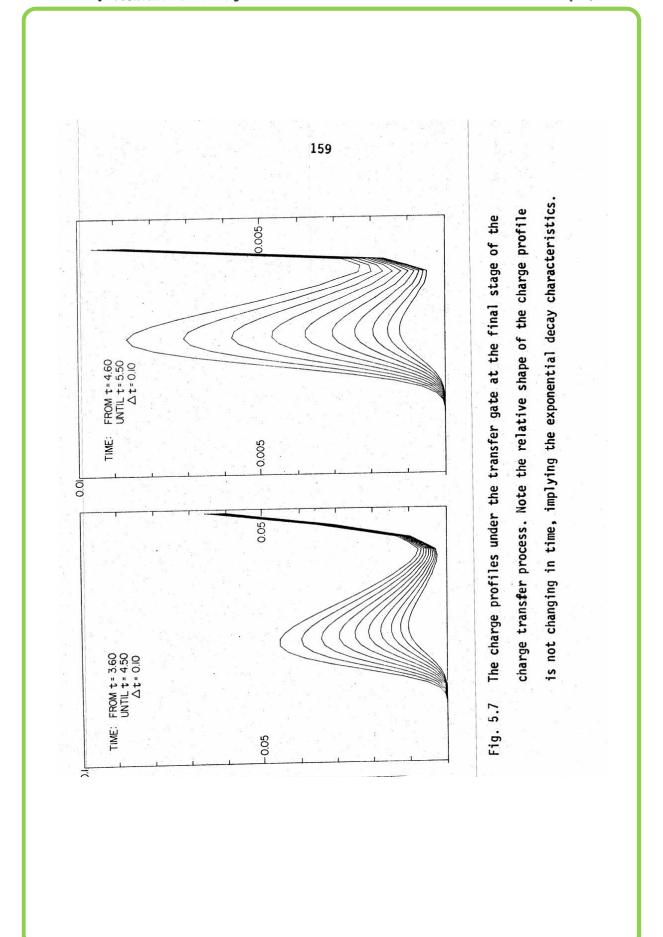

Integrating Poisson equation from X = 0 to  $X = X_1$ , that is, in the surface field induced depletion region, we obtain

$$E_{s} = \left(\frac{N_{A}}{\varepsilon_{si}}\right) X_{1}$$

(1-8d)

and

$$\phi_{\rm m} = \phi_{\rm S} - \left(\frac{\varepsilon_{\rm Si}}{2N_{\rm A}}\right) E_{\rm S}^2$$

(1-8e)

where  $X_1$  is the surface field induced depletion width. The p-side and n-side junction depletion width must be connected by the relation  $X_2N_A = X_3N_d \text{ because of charge neutrality deep in the substrate.}$  The p-side junction depletion width  $X_2$  can be written in terms of the minimum potential  $\phi_m$  as seen by

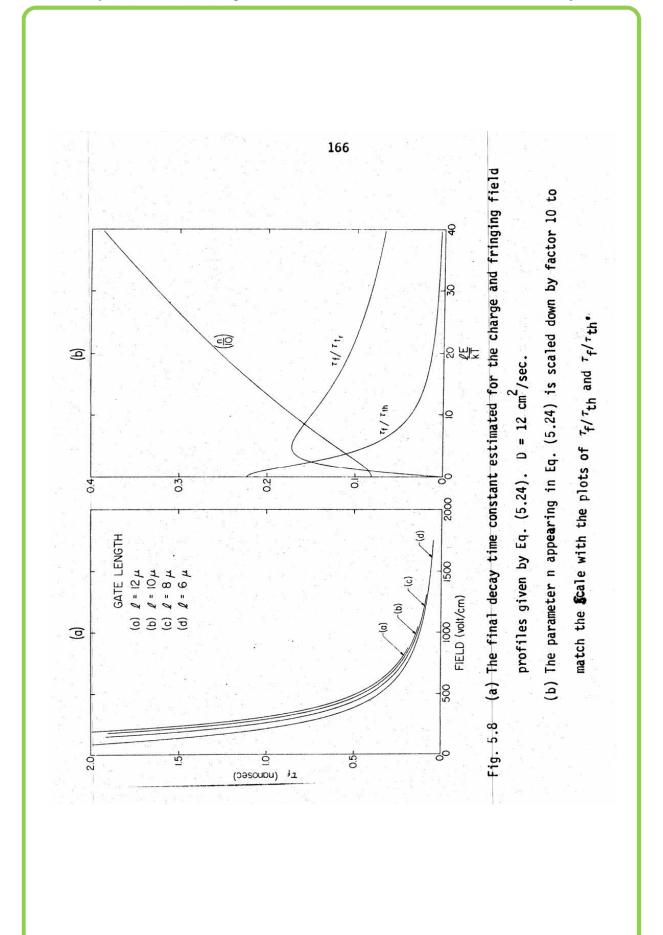

$$\frac{X_2}{X_d} = \sqrt{\frac{-\phi_m}{\phi_q}} \qquad (1-8f)$$

where

$$\phi_{\mathbf{q}} = \frac{N_{\mathbf{A}} X_{\mathbf{d}}^{2}}{2 \varepsilon_{\mathbf{S} \mathbf{i}}} \left[ 1 + \frac{N_{\mathbf{A}}}{N_{\mathbf{d}}} \right] \tag{1-8g}$$

If the value of the minimum potential  $\phi_m$  is known, we first obtain the p-n junction depletion width  $(X_2+X_3)$  from Eq. (1-8f) and then Eq. (1-8g). If the amount of the signal charge Q is prescribed, Eq. (1-8a) gives the surface field induced depletion width  $X_1$ . Then the surface electric field  $E_s$ , and then the surface potential  $\phi_s$ , can be calculated from Eq. (1-8d) and (1-8e) respectively. The corresponding gate voltage  $\phi_G$  can be evaluated from Eq. (1-8b) knowing the relation between the gate voltage  $\phi_G$  and  $\phi_{sF}$  as seen in Eq. (1-8c).

In those equations there are four fixed parameters,  $X_0$ ,  $X_d$ ,  $N_A$ , and  $N_d$  that can be controlled in the fabrication of device, and three more variables, Q,  $\phi_m$ , and  $\phi_{SF}$  among which there is only one constraint during the device operations. The associated constraint among the three varibles can be written as an expression of the minimum potential  $\phi_m$  in terms of the gate voltage  $\phi_{SF}$  and the signal charge Q. In the following, the procedure to calculate the expression is described.

To write the analytic expression for the minimum potential as simple as possible, we introduce three parameters,  $\phi_{\rm t}$ ,  $\phi_{\rm d}$  and R defined by

$$\phi_{t} = \frac{N_{A} \epsilon_{Si}}{2 c_{0}^{2}} \qquad , \qquad (1-9a)$$

$$\frac{\phi_{\mathbf{d}}}{\phi_{\mathbf{t}}} = \frac{C_{\mathbf{0}}}{C_{\mathbf{d}}} \left( 1 - \frac{Q}{Q_{\mathbf{d}}} \right) \left[ 2 + \frac{C_{\mathbf{0}}}{C_{\mathbf{d}}} \left( 1 - \frac{Q}{Q_{\mathbf{d}}} \right) \right] \qquad , \qquad (1-9b)$$

and

$$R = \frac{N_A}{2N_d} \frac{\phi_d - \phi_s F}{\phi_d + \phi_t} \qquad (1-9c)$$

with  $Q_d \equiv N_A X_d$  and  $C_d = \epsilon_{Si}/X_d$ .  $\phi_t$  is just a geometrical constant (in volt) determined by the p-channel doping density  $N_A$  and the oxide capacitance  $C_o$ .  $\phi_d$  is proportional to  $\phi_t$  and the proportionality constant given in Eq. (1-9b) is actually a quadratic function of the single charge Q. The dimensionless constant R is of the order of 10 to 20 in normal device configurations because  $N_A$  is 10 to 20 times larger than the substrate doping  $N_d$ . The physical significance of these parameters,  $\phi_t$ ,  $\phi_d$  and R are explained more in detail as we go further in interpretation and results of depletion approximation in next section.

In terms of these parameters, the minimum potential  $\boldsymbol{\varphi}_{m}$  can be expressed as

$$\phi_{m}(Q,\phi_{SF}) = -\left(1 + \frac{N_{d}}{N_{A}}\right) \left[\phi_{d} - \phi_{SF}\right] f(R) \qquad , \qquad (1-10a)$$

where f(R) is a slowly varying function of R and defined by

$$f(R) = \frac{R}{1 + R + \sqrt{1 + 2R}}$$

(1-10b)

### The derivation is as following:

Eq. (1-8a) with  $Q_d = N_A X_d$  gives

$$\frac{Q}{Q_d} = 1 - \left(\frac{x_1}{x_d}\right) - \left(\frac{x_2}{x_d}\right)$$

With Eq. (1-8f) for  $X_2/X_d$  we obtain

$$-\frac{\phi_{\rm m}}{\phi_{\rm q}} = \left[ \left(1 - \frac{Q}{Q_{\rm d}}\right) - \left(\frac{\chi_1}{\chi_{\rm d}}\right)^2 \right]^2 \tag{*}$$

Also form Eq. (1-8e) substituting  $\phi_S$  by Eq. (1-8b) and  $X_1$  by Eq. (1-8d) we obtain

$$\phi_{\rm m} = \phi_{\rm SF} - (\frac{N_{\rm A}X_{\rm d}}{C_{\rm o}})(\frac{X_{\rm 1}}{X_{\rm d}}) - \frac{N_{\rm A}X_{\rm d}^2}{2 \epsilon_{\rm Si}} (\frac{X_{\rm 1}}{X_{\rm d}})^2$$

Using Eq. (1-9a) for  $\phi_t$  and  $C_d = \epsilon_{si}/X_d$  we obtain

$$\phi_{m} = \phi_{sF} - 2\phi_{t}(\frac{c_{o}}{c_{d}})(\frac{x_{1}}{x_{d}}) - \phi_{t}(\frac{c_{o}}{c_{d}})^{2}(\frac{x_{1}}{x_{d}})^{2}$$

This equation and Eq. (\*) above give

$$\frac{(\frac{x_1}{x_d})^2}{(\frac{x_1}{x_d})^2} = \frac{\phi_m}{\phi_q} + 2(1 - \frac{Q}{Q_d})(\frac{x_1}{x_d}) - (1 - \frac{Q}{Q_d})^2$$

$$= (\frac{C_d}{C_o})^2 \left[ \frac{\phi_s F - \phi_m}{\phi_t} \right] - 2(\frac{C_d}{C_o})(\frac{x_1}{x_d})$$

Solving for  $X_1/X_d$  we obtain

$$2\left[\left(1-\frac{Q}{Q_{d}}\right)+\frac{C_{d}}{C_{Q}}\right]\left(\frac{X_{1}}{X_{d}}\right)=\left(1-\frac{Q}{Q_{d}}\right)^{2}+\left(\frac{C_{d}}{C_{Q}}\right)^{2}\left[\frac{\phi sF^{-\phi}m}{\phi t}\right]+\left(\frac{\phi m}{\phi Q}\right)$$

Substituting  $X_1/X_d$  of theabove equation to Eq. (\*) we obtain

$$-\frac{\phi_{m}}{\phi_{q}} = \left\{ (1 - \frac{Q}{Q_{d}}) - \frac{(1 - \frac{Q}{Q_{d}})^{2} + (\frac{C_{d}}{C_{o}})^{2} \left[\frac{\phi s F^{-\phi} m}{\phi_{t}}\right] + \left(\frac{\phi_{m}}{\phi_{q}}\right)}{2 \left[(1 - \frac{Q}{Q_{d}}) + \frac{C_{d}}{C_{o}}\right]} \right\}^{2}$$

This equation can be rearranged to give

$$-4\left[\left(1-\frac{Q}{Q_{d}}\right)+\frac{c_{d}}{c_{o}}\right]^{2}_{\phi_{d}}$$

$$=\left\{\left(1-\frac{Q}{Q_{d}}\right)\left[\left(1-\frac{Q}{Q_{d}}\right)+\frac{2c_{d}}{c_{o}}\right]-\left(\frac{c_{d}}{c_{o}}\right)^{2}\left[\frac{\phi_{sF}-\phi_{m}}{\phi_{t}}\right]-\left(\frac{\phi_{m}}{\phi_{q}}\right\}\right\}.(**)$$

Knowing from Eq. (1-9b) that

$$\left(1 + \frac{\phi_d}{\phi_t}\right) = \left[1 + \frac{c_o}{c_d} \left(1 - \frac{Q}{Q_d}\right)\right]$$

the LHS of the above equation (\*\*) becomes

$$-4 \left(\frac{C_d}{C_0}\right)^2 \left(1 + \frac{\phi_d}{\phi_t}\right) \left(\frac{\phi_m}{\phi_q}\right)$$

Also substituting  $\phi_d$  of Eq. (1-9b) into the RHS of Eq. (\*\*) above, we can write the RHS of Eq. (\*\*) as seen by

$$\left\{ \left( \frac{c_d}{c_0} \right)^2 \frac{\phi_d}{\phi_t} - \left( \frac{c_d}{c_0} \right)^2 \left( \frac{\phi_{sF} - \phi_m}{\phi_t} \right) - \left( \frac{\phi_m}{\phi_q} \right) \right\}^2$$

Consequently the Eq. (\*\*) above becomes

$$-4\left(1+\frac{\phi_{d}}{\phi_{t}}\right)\left(\frac{\phi_{m}}{\phi_{q}}\right)$$

$$=\left\{\left(\frac{C_{d}}{C_{o}}\right)\left(\frac{\phi_{d}-\phi_{sF}}{\phi_{t}}\right)+\left\{\frac{C_{d}}{C_{o}\phi_{t}}-\frac{C_{o}}{C_{d}\phi_{q}}\right\}\right.\phi_{m}\right\}^{2} (***)$$

Furthermore noting by Eq. (1-8g) and Eq. (1-9a) that

$$\left(\frac{c_d}{c_{o\phi_t}}\right) - \left(\frac{c_o}{c_{d\phi_q}}\right) = \left(\frac{c_d}{c_{o\phi_t}}\right) \frac{1}{\left(1 + \frac{N_d/N_A}{c_{o\phi_t}}\right)}$$

the RHS of this equation (\*\*\*) becomes

$$\left(\frac{\phi_{d} - \phi_{SF}}{\phi_{t}}\right)^{2} \left(\frac{C_{d}}{C_{o}}\right)^{2} \left[1 + \frac{\phi_{m}}{\left(1 + N_{d}/N_{A}\right)\left(\phi_{d} - \phi_{SF}\right)}\right]^{2}$$

Knowing from Eq. (1-8g) and (1-9a) that

$$\left(\frac{\phi_{t}}{\phi_{q}}\right)\left(\frac{C_{o}}{C_{d}}\right) = \left(\frac{N_{d}}{N_{A}}\right)\frac{1}{\left(1 + N_{d}/N_{A}\right)}$$

and defining the parameter f by the equation as seen by

$$f = \frac{-\phi_{II}}{(1 + Nd/N_A)(\phi_d - \phi_{SE})}$$

(\*\*\*\*)

the above equation (\*\*\*) can be written as

$$\frac{2 f}{R} = (1 - f)^2$$

(\*\*\*\*\*)

where R is given by Eq. (1-9c).

Solving this equation for f(R) in terms of R we obtain the Eq. (1-10b). Since f(R) is originally defined by the Eq. (\*\*\*\*) above, we immediately obtain the analytic expression for the minimum potential  $\phi_m$  as seen by Eq. (1-10a). In the above derivations, the four equations (\*), (\*\*), (\*\*\*) and (\*\*\*\*\*) are all the same relation expressed in terms of different physical parameters, and the parameters R and f(R) seem to play very important roles in studing the mutual interactions among the important device parameters such as the oxide thickness  $X_0$ , the p-layer diffusion depth  $X_d$ , the p-layer doping  $N_A$ , and the substrate doping  $N_d$ ; and the three more variables, Q,  $\phi_{SF}$ , and  $\phi_m$ .

END OF DERIVATION

For large values of R, f(R) approaches unity very slowly. If we want to know a rough value of the minimum potential without going through the calculation procedure defined by Eqs. (1-9) and (1-10), we can estimate the value by computing  $\phi_d$  from Eq. (1-9b) and setting  $\phi_m \approx -\left(\phi_d - \phi_S F\right)$ , where we note the gate voltage  $\phi_G$  is related to  $\phi_{SF}$  by Eq. (1-8c).

The general characteristics of the physical parameters implied in the analytic expression for the minimum potential can be seen by the relationships implied in the above equations. It is clear from Eq. (1-10a) that the dependence of the minimum potential  $\phi_{m}$  upon the gate voltage is quite linear. On the other hand because  $\phi_d$  defined by Eq. (1-9b) depends quadratically upon the signal charge, we expect that the minimum potential will also show a quadratic dependence on the signal charge. We also note that a thicker oxide produces a deeper minimum potential. This effect can be calculated quantitatively by Eq. (1-9a) in which we see the value of  $\phi_{t}$  is proportional to the square of the oxide thickness. For a given gate voltage, the minimum potential is different for different oxide thicknesses, because the value of  $\phi_{\mbox{\scriptsize d}}$ will be different. But  $\phi_d$  does not depend on  $\phi_{SF}$  or on the gate voltage. Hence we observe, when two MOS structures with different oxide thickness are given, the difference of the minimum potentials will not depend appreciably upon the gate voltage applied on both structures. These observations are important in designing a working buried channel CCD and clocking schemes, and so we will discuss these points more clearly in detail in the next section.

### 1.4 Interpretation and Results of Depletion Approximation

We first describe qualitatively how the parameters  $^{\phi}_{t}$  and  $^{\phi}_{d}$  depend on the oxide thickness X $_{0}$  and the signal charge Q. This consideration is important to describe qualitatively how the minimum potential  $^{\phi}_{m}$  depends on the salient physical parameters.

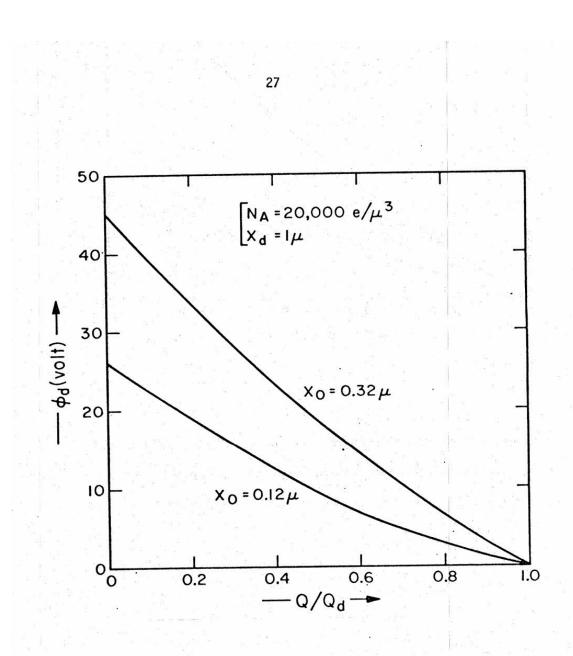

$\phi_d$  for two different values of oxide thickness is plotted in Fig. 1.6 as a function of the signal charge nomralized by the maximum depletion charge  $Q_d = N_A X_d$ . In this case study, the p-channel depth  $X_d$  is taken to be  $1\mu$  and the p-channel doping density to be 20,000 e/ $\mu^3$  which is equal to 2 x  $10^{16}$  e/cm $^3$ . The silicon dielectric constant  $\epsilon_{Si}$  is taken to be 11.7  $\epsilon_0$  which is equal to 648 e/volt· $\mu$  and the silicon oxide dielectric constant  $\epsilon_{Si0}$  to be 3.9  $\epsilon_0$  or 216 e/volt· $\mu$

Observe in Fig. 1.6 that the nonlinear dependence of  $\phi_{\mbox{d}}$  prevails when more signal charge Q is present in the channel.

Knowing the value of  $\phi_d$ , the difference  $(\phi_{SF}^{-}\phi_d)$  can be calculated for a given value of  $\phi_{SF}$ . This difference is of the order of the minimum potential  $\phi_m$ . Hence  $\phi_d$ , gives a rough estimate of the voltage drop of the minimum potential  $\phi_m$  relative to the gate voltage  $(\phi_{SF})$ . Specifically, Fig. 1.6 shows for zero gate voltage  $(\phi_{SF} = 0)$  and the zero signal charge (Q = 0), the channel potential is rough -45 volt for  $X_O = 0.32\mu$  and -25 volt for  $X_O = 0.12\mu$ . Hence the thicker the oxide, the channel is at the lower potential for the charge carriers.

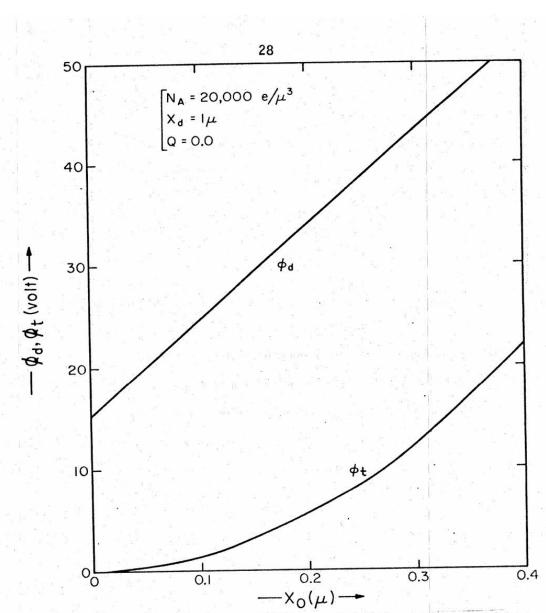

In Fig. 1.7,  $\phi_t$  and  $\phi_d$  are plotted against the oxide thickness for zero-signal charge. As seen in the figure, and as one can easily see from Eq. (1-9b) when  $\phi_d$  is expressed in terms of  $X_0$ ,  $\phi_d$  is a linear

Fig. 1.6  $\phi_d$  defined by Eq. (1-9b) plotted against the signal charge Q normalized by the sheet doing density  $Q_d$  in the p-layer for the oxide thickness  $X_0$  of  $0.12\mu$  and  $0.32\mu$ .

Fig. 1.7 The dependence of the parameters  $\phi_{\bf d}$  and  $\phi_{\bf t}$  defined by Eq. (1-9a) and Eq. (1-9b) upon the oxide thickness  $X_{\bf 0}$  is illustrated in the figure.

function of the oxide thickness when no signal charge is present. As a matter of clarity, for Q = 0 from Eq. (1-9b), we obtain

$$\frac{\Phi_{d}}{\Phi_{d}} = \frac{1}{C_{0}} + \frac{1}{2C_{d}}$$

(1-10c)

The linear dependence of  $\phi_d$  upon the oxide thickness  $X_O$  also implies qualitatively the linear dependence of the minimum potential  $\phi_m$ , upon  $X_O$ . The quadratic dependence of  $\phi_t$  upon the oxide thickness  $X_O$  is clear from Fig. 1.7 and also from Eq. (1-9a).

We have shown how the parameters  $\phi_t$  and  $\phi_d$  depend quantitatively on the oxide thickness and the signal charge, and also described qualitatively how the minimum potential  $\phi_m$  depends on these parameters. As for Eq. (1-10a) we have considered only for the factor  $(\phi_{sF}^{-}\phi_d)$  and if we wish to have a more accurate value, we can calculate the value of R from Eq. (1-9c) to obtain the correction factor f(R) for the minimum potential. But this correction is only about 10  $\sim$  20% of the first rough estimate. This point can be made clear as we consider the actual values of R and f(R) as following.

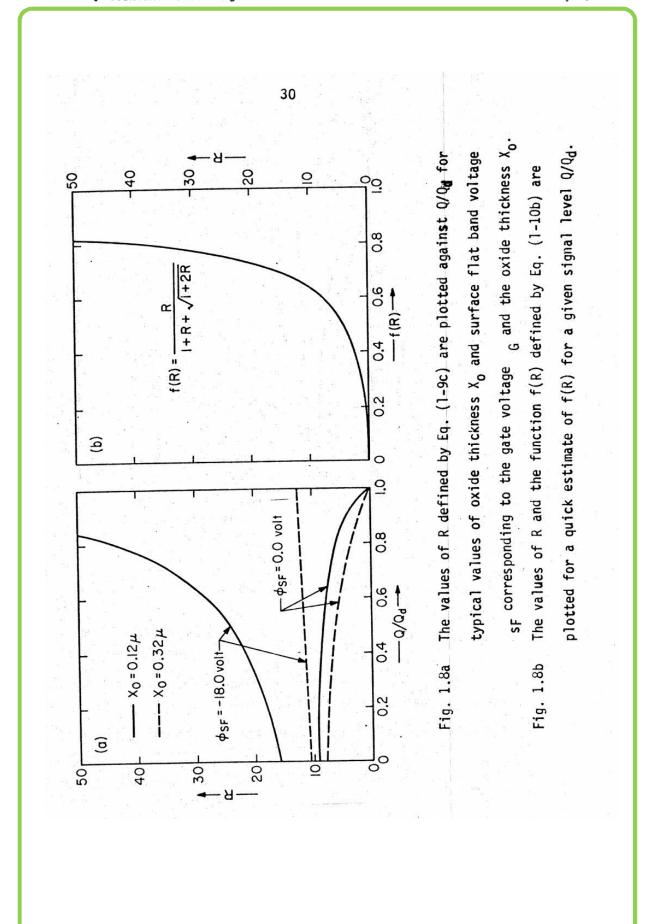

For the range of interest, the values of R will be between 5.0 and 50.0 as shown in Fig. 1.8a. In this figure, R is plotted against the normalized signal charge  $Q/Q_d$  for a pair of typical values of oxide thickness  $X_0$  and of  $\phi_{SF}$ . Observe that the values of R may vary in a wide range but the corresponding factor f(R) will be fairly constant as clearly seen in Fig. 1.8b when one compares Figs. 1.8a and 1.8b.

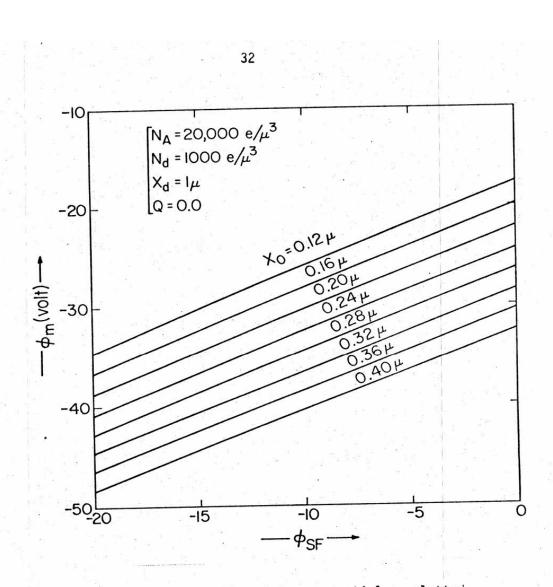

For a special case of interest with no signal charge present, the minimum potential is plotted against  $\phi_{\mbox{SF}}$  for different oxide thickness

in Fig. 1.9. As we claimed earlier, note that the dependence of the minimum potential upon  $\phi_{SF}$  (hence, upon the gate voltage) is quite linear. We also observe the lines are for practical purposes parallel. That is, the difference of the minimum potentials will not depend on the gate voltage applied on a pair of MOS structures with different oxide thickness.

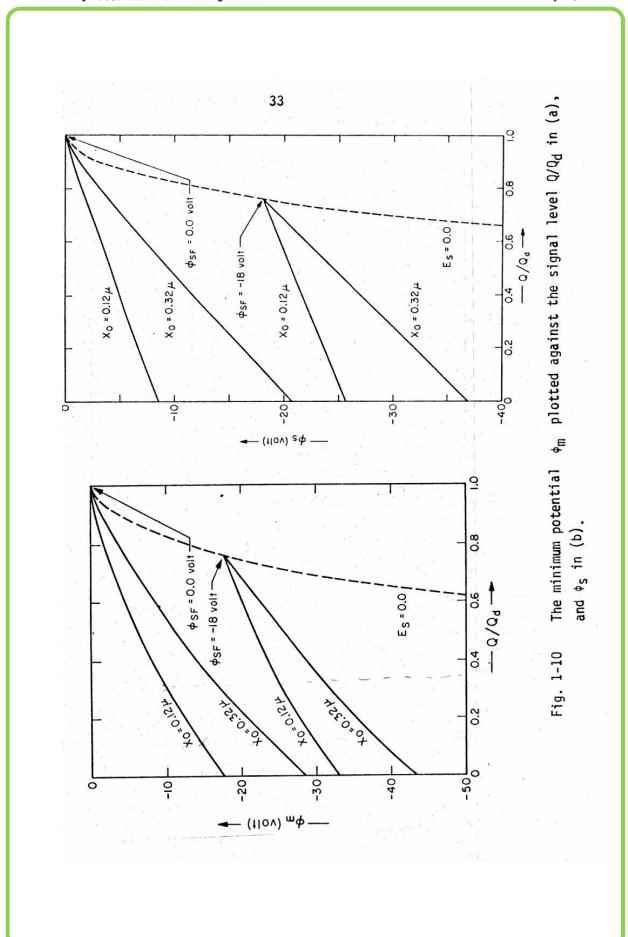

In Fig. 1.10a, the dependence of the minimum potential upon the signal charge is illustrated for typical values of oxide thickness and gate voltages (actually  $\phi_{SF}$ ). The top two solid curves are for  $\phi_{SF}=0.0$  volt, and the bottom two for  $\phi_{SF}=-18.0$  volt. These four curves define the minimum potential levels, that is, the four points at Q = 0 in the figure, which may be applied for two phase buried channel CCD operations. This point is discussed further in the next section and the full treatment of two phase buried channel CCD operations is given in the next chapter.

We are now in the position to discuss one of the most important aspects in the metal oxide semiconductor system for our one dimensional buried channel CCD structure, that is, the condition for zero surface electric field, or flat band.

The dashed curve in Fig. 10.a was obtained by calculating the values of the minimum potential as a function of the signal charge with the constraint that the surface electric field  $E_s$  is zero. That is, for the case of zero-depletion width  $X_1$  by Eq. (3-8d), we obtain from Eqs. (1-8a) and (1-8f) after some manipulation for  $E_s=0$ , that is, for  $X_1=0$ ,

Fig. 1.9 The minimum potential  $\phi_{m}$  plotted against  $\phi_{SF}$  for various oxide thickness  $X_{O}$ .

$$\phi_{SF} = \phi_{m} \Big|_{E_{S}=0} = -\left(1 - \frac{Q}{Q_{d}}\right)^{2} \phi_{q}$$

(1-11a)

Recall that the parameter  $\phi_{\bf q}$  was originally introduced in Eq. (1-8f) to relate the p-side depletion width X to the minimum potential  $\phi_{\bf m}$ . Here, we also note the band is flat at the semiconductor-oxide interface. Hence, we have  $\phi_{\bf m} = \phi_{\bf sF}$ . When the signal charge increases beyond the dashed curve, the signal charge will "touch" the oxide-semiconductor interface.

The surface electric field is zero and the band is flat when, for given gate voltage  $(\phi_{SF})$ , the amount of the signal charge becomes, from the Eq. (1-11a) above,

$$Q \Big|_{E_s=0} = Q_d \left[ 1 - \sqrt{-\frac{\phi_s F}{\phi_q}} \right] \qquad (1-11b)$$

When no signal charge is present (Q = 0), then from Eq. (3-11a) we note that the magnitude of the gate voltage  $\phi_{SF}$  must be set equal to  $\phi_{Q}$  given by Eq. (1-11b). For the values used in the case study, this gives  $\phi_{SF} = -\phi_{Q} = -324$  volt for  $E_{S} = 0$  and Q = 0. For this value of  $\phi_{SF}$ , Eq. (1-11a) gives Q = 0. The dashed curve in Fig.1.10a is given by Eq. (1-11a) and the values of the signal charge Q for  $E_{S} = 0$  (calculated by Eq. (1-11b) for  $\phi_{SF} = 0.0$  volt and -18 volt) give the two points that are arrowed in Fig. 1.10a.

The surface potential  $\phi_S$  is plotted against signal level in Fig.1.10b. Note the dependence of the surface potential upon the signal charge is quite linear as compared to the minimum potential. The slope is proportional to the oxide thickness  $X_O$  and given by the

reciprocal of the oxide capacitance  $C_0$ . Note the pairs of lines for  $X_0 = 0.12$  and  $X_0 = 0.32$  are parallel to each other respectively. As we observe in the relation given by Eq. (1-8b), the surface potential depends on the surface electric field in a linear fashion. Hence we observe that the surface electric field is also a linear function of the signal charge Q in a good accuracy.

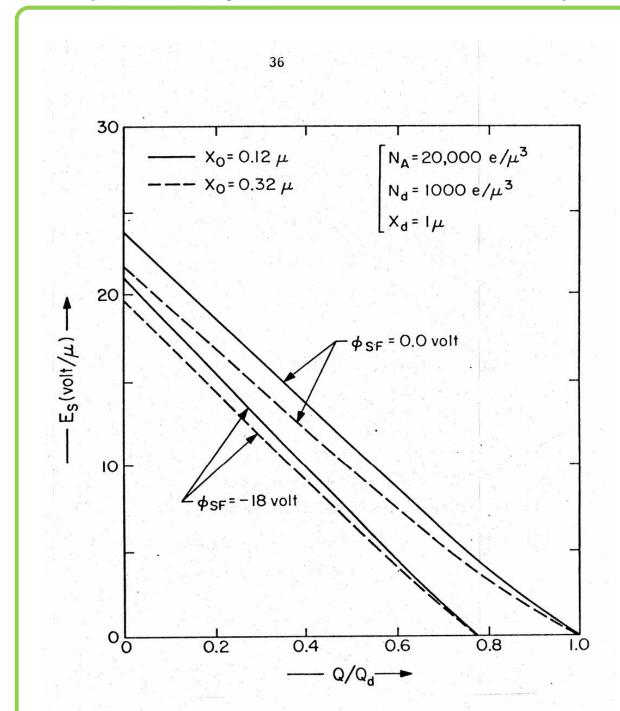

The surface electric field  $E_s$  is plotted in Fig.1.11. The slope is roughly the reciprocal of the silicon dielectric constant  $\varepsilon_{Si}$ . The analytic expression for the surface electric field is as messy as the one for the minimum potential  $\phi_m$ . To complete the discussion, we present the expression anyway.

Define two parameters A(Q) and B(Q) as seen by

$$A(Q) = \left(1 + \frac{N_d}{N_A}\right) \left(1 - \frac{Q}{\Omega_d}\right) + \frac{N_d}{N_A} \frac{C_d}{C_Q} \qquad (1-11c)$$

and

$$B(Q) = \left(1 + \frac{N_d}{N_A}\right) \left[ \left(1 - \frac{Q}{Q_d}\right)^2 + \frac{\phi_{sF}}{\phi_{q}} \right] \qquad (1-11d)$$

Both A(Q) and B(Q) are functions of the signal charge Q. Then the surface electric field  $E_S$  can be calculated from the expression

$$E_{s} = \frac{AQ_{d}}{\varepsilon_{Si}} \left[ 1 - \sqrt{1 - B/A^{2}} \right] \qquad (1-11e)$$

The condition for zero surface electric field is B(0) = 0. Then from Eq. (1-11d) we have the relation as seen in Eq. (1-11c). For the range of interest, the right factor in RHS of (1-11e) is fairly constant with values between 0.6 and 0.8 and the surface electric field is proportional to A, which is a linear function of the signal charge Q.

Fig. 1.11 The strength of the surface electric field  $E_S$  is plotted against the signal level  $Q/Q_d$  for typical values of the oxide thickness  $X_O$  and the flat band voltage  $\phi_{SF}$  corresponding to the gate voltage  $\phi_G$  as related by Eq. (1-8c).

## 1.5 Constraints on Gate Voltage and Signal Charge

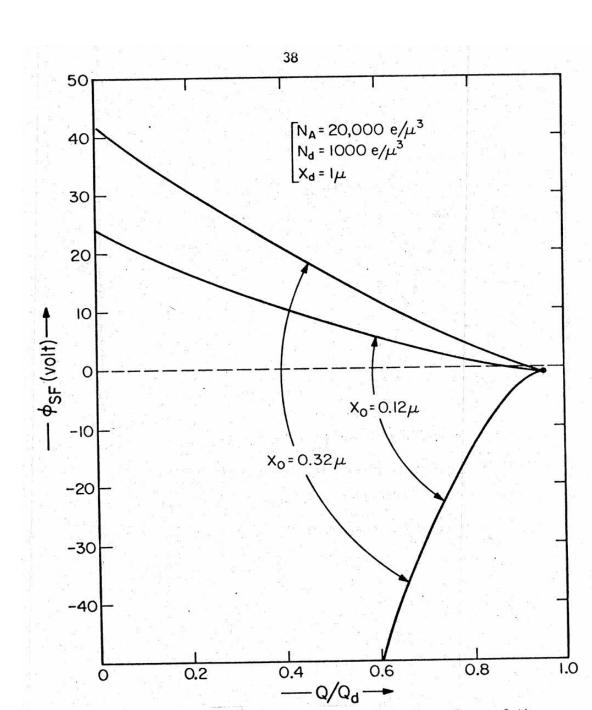

We are now in the position to describe the upper and lower bounds imposed on the minimum potential for normal device operations. Without this consideration, the device operation is practically impossible and the important results are summarized as a graphic illustration in Fig. 1.12.

We will first give the physical background for the upper and lower bounds and then derive the equations which represent the constraints between the gate voltage ( $\phi_{SF}$ ) and the signal charge Q for normal device operations. The conditions outside the normal device operations, that is, the accumulation and inversion conditions will then be discussed.

Returning to Fig.1.10a for  $\phi_{sF}=0.0$  volt, we observe the minimum potential approaches to zero as the amount of signal charge approaches the maximum possible capacity  $0_d$ . However, we note the minimum potential must be always lower than the ground reference at least by the amount of the p-n junction built-in voltage  $\phi_B$  given by Eq. (1-7). For our case study,  $N_A=20{,}000~e/\mu^3$  and  $N_d=1000~e/\mu^3$  and  $\phi_B$  is about 0.63 volt. If the minimum potential is raised beyond this point by the excess signal charge, the p-n junction will be forward-biased momentarily and the signal charge will be dumped to the substrate as a current through the p-n junction.

To prevent the p-n junction from becoming forward-biased, the gate voltage and the signal charge must be controlled so that the minimum potential  $\varphi_m$  is always lower than the ground reference potential at least by  $\varphi_B$ . That is,

Fig. 1.12 The range of the permissible values of the gate voltage  $\phi_G$  is implied by the flat band voltage  $\phi_{SF}$  plotted against the signal level Q/Qd for typical oxide thickness of 0.12 $\mu$  and 0.32 $\mu$ .

$$\phi_{m}(\phi_{sF}, Q) \leq -\phi_{B}$$

(1-12a)

On the other hand, when the surface electric field  $\rm E_{\rm S}$  becomes zero, the signal charge starts accumulating at the interface. Then, the trapping in interface states at the semiconductor oxide interface imposes limitations on the performance of CCD operations. To prevent the signal charge from "touching" the interface, we must have, referring to Eq. (1-11a) or Fig.1.10a and Fig.1.10b

$$\phi_{\mathsf{m}}(\phi_{\mathsf{sF}},Q) \geq -\left(1-\frac{Q}{Q_{\mathsf{d}}}\right)^2 \phi_{\mathsf{q}}$$

(1-12b)

From the above two equations, it is clear that we cannot have the signal charge Q equal to  $\mathbf{Q}_{\mathbf{d}}$  in any circumstances during CCD transfer operations.

Combining the constraints (1-12a) and (1-12b) we obtain

$$-\left(1-\frac{Q}{Q_d}\right)^2 \phi_q \le \phi_m \le -\phi_B \qquad (1-12c)$$

This inequality imposes a smaller upper bound than the previous one (Q\_d) upon the signal charge Q. That is, we must always have Q  $\leq$  Q\_MAX where Q\_MAX is defined as

$$Q_{MAX} \equiv Q_d \left[ 1 - \sqrt{\frac{\phi_B}{\phi_Q}} \right]$$

(1-12d)

This condition, Q  $\leq$  Q<sub>MAX</sub>, must be satisfied regardless of the gate voltage  $\phi_{SF}$ . The signal charge must be always smaller than this value at least. (The gate voltage actually restricts the value of Q further into a narrow range.) For the case study in this presentation, Q<sub>MAX</sub> is smaller than Q<sub>d</sub> by 4.5% for  $\phi_{q}$  = 308 volt and  $\phi_{B}$  = 0.63 volt.

The problem is to rewrite Eqs. (1-12a) and (1-12b) in terms of the gate voltage  $\phi_{sF}$  and the signal charge Q explicitly. When  $\phi_m$  =  $-\phi_B$ , we have a functional dependence between the signal charge Q and the gate voltage  $\phi_{sF}$ . This functional relation gives the boundary for the range of Q and  $\phi_{sF}$  constrained by Eq. (1-12a). The calculation is tedious but the result can be obtained by solving Eq. (1-8) for  $\phi_m$  =  $-\phi_B$ . And we obtain the constraint corresponding to Eq. (1-12a) as seen by

$$\phi_{SF} \leq \left[ \frac{Q_{MAX} - Q}{C_{Q}} \right] \left[ 1 + \left( \frac{C_{Q}}{2C_{Q}} \right) \frac{Q_{MAX} - Q}{Q_{Q}} \right] - \phi_{B} \qquad (1-13a)$$

This is the constraint to keep the signal charge from being washed away to the substrate. Note for the maximum signal charge Q =  $Q_{MAX}$ .  $\phi_{sF} \leq -\phi_{B}$ .

The other constraint (1-12b) can be written simply as

$$\phi_{\mathsf{sF}} \geq -\left(1 - \frac{\mathsf{Q}}{\mathsf{Q}_{\mathsf{d}}}\right)^2 \phi_{\mathsf{q}} \qquad (1-13b)$$

because  $\phi_{sF} = \phi_{m}$  for  $E_{s} = 0$  as seen in Eq. (1-11a).

These formulations are very important when one is involved in designing a working buried channel CCD structure. Figure 1.12 shows the range of the permissible values of  $\phi_{SF}$  and Q. The boundary lines can be obtained from Eqs. (1-13a) and (1-13b). Observe the oxide capacitance  $C_0$  appears in the epxression (1-13a) but the lower bound for  $\phi_{SF}$  which is given by Eq. (1-13b) does not depend on the oxide thickness. These characteristics are clearly observed in Fig. 1.12.

The conditions under normal device operations are clear from the

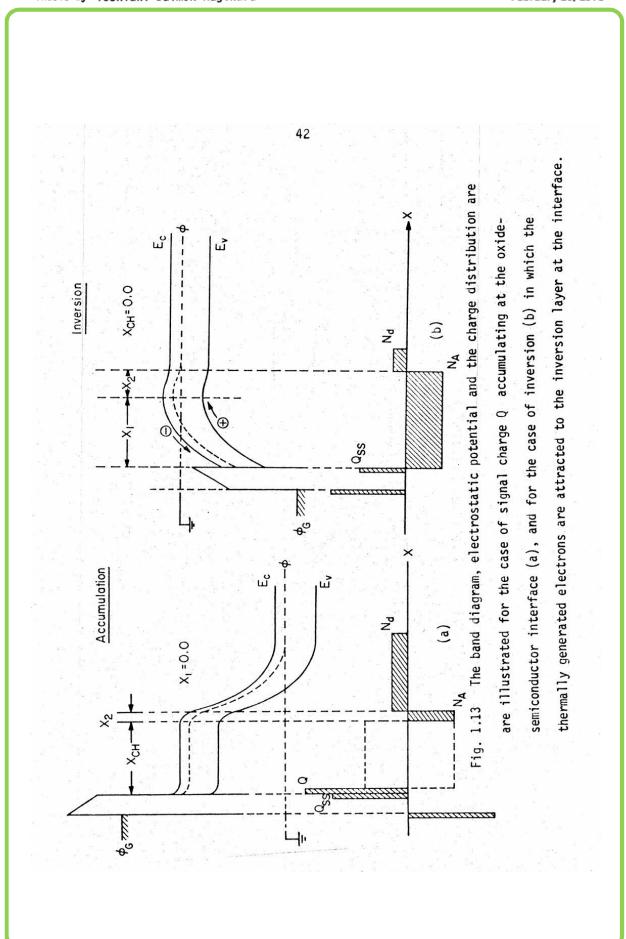

above discussion. The conditions outside the normal device operations, that is, the accumulation and inversion conditions can be described more intuitively with the aid of Fig.1.13a and 1.13b. We now first consider the condition depicted in Fig.1.13a, that is, the accumulation.

Suppose a certain amount of signal charge is present in the p-diffusion layer and we would like to consider how the gate voltage influence the band structure. When a large negative voltage is applied to the gate, the resulting interface electric field becomes attractive to the signal charge. That is,  $E_{\rm S} < 0$  and the constraint given by Eq. (1-13b) and shown in Fig.1.12 will not be satisfied. In this case, as depicted in Fig.1.13a, an accumulation layer will be formed at the interface whose thickness is small compared to the insulator thickness  $X_{\rm O}$ . Consequently, under accumulation the capacitance measured will be essentially that of the insulator  $C_{\rm O}$ . The mobile charge and fixed charge distributions are illustrated in the lower figure.

Now suppose we raise the gate voltage suddenly to a very large positive value. Then, the constraint defined by Eq. (1-13a) suddenly becomes not satisfied and all of the signal charge will be washed away into the substrate suddenly. If the gate voltage is in a reasonable range, some of the signal charge can be "saved" in the p-diffusion region. As we increase the gate voltage, the signal charge will be repelled from the surface, then also from the p-diffusion region, partially by the positive surface state charge  $\mathbb{Q}_{\text{SS}}$  and the positive image charge at the gate, resulting in the growth of a depletion layer which extends deeper into the p-diffusion layer. A

further increase of the voltage causes the p-layer near the interface to collect thermally generated minority carriers (electrons) forming an inversion layer. The situation is illustrated in Fig. 1.13b. The time required for this process is called the storage time. For a good device, the storage time is of the order of one second. Since the storage time is much greater than the typical operation time of CCD, the effect of the formation of an inversion layer is not so serious and indeed in this way we can refresh the CCD, that is, we can delete all the signal charges.

## 1.6 Device Capacitance

The gate capacitance  $C_g$  is the most important parameter when one is concerned with the clock load and the actual speed of the device operation. In this section we first consider the gate capacitance and describe how it changes under the condition of inversion. Then the relevant relations among the gate capacitance and other capacitance, such as oxide capacitance and depletion capacitance, are presented in terms of the physical parameters discussed in the previous sections.

The gate capacitance  $C_g$  may be defined as the change of the image charge on the metal gate with respect to the gate voltage. The charge on the metal gate is by definition the image charge of the total charge at the interface and inside the semiconductor. We now describe how it changes under the condition of inversion depicted in Fig. 1.13b

When the device is static, the large positive gate voltage causes, thermally generated minority carriers to shield effectively the depletion region from any increase in field so that the capacitance

becomes dominated by the inversion layer and approaches that of the insulator  $C_0$ . However, during dynamic operations of the device the positive voltage results in the growth of a depletion layer which extends deeper into the p-diffusion layer, and the increasing distance between it and the charge on the metal causes the capacitance to fall further with increasing gate voltage.

We now approach the problem more quantitatively to obtain the relevant expressions among the gate, oxide and depletion capacitances and other physical parameters.

In normal device operations, using the relations given by Eqs. (1-8) it can be shown that the gate capacitance is proportional to the change of the surface electric field with respect to the gate voltage  $\phi_G$  (or  $\phi_{SF}$ ). Specifically, we have

$$C_g = \epsilon_{Si} \frac{\partial E_s}{\partial \phi_{SF}}$$

, (1-14a)

and this can be also rewritten as

$$\frac{1}{C_{q}} = \frac{1}{C_{0}} + \frac{1}{C_{1}} + \frac{1}{C_{2}}$$

(1-14b)

where  $C_1 = \varepsilon_{Si}/X_1$  is the surface depletion capacitance and  $C_2 = \varepsilon_{Si}/(1 + \frac{d}{N_A})X_2$  is the p-n junction capacitance.

In principle, it is possible to obtain the change  $\Delta \phi_m$  of the minimum potential in terms of the changes,  $\Delta \phi_{SF}$  and  $\Delta Q$ , of the surface flatband voltage and the signal charge. After a diligent work of symbol manipulations, one would find

$$\Delta \phi_{\rm m} = \frac{\left(\frac{1}{C_{\rm o}} + \frac{1}{C_{\rm 1}}\right) \Delta Q + \Delta \phi_{\rm sF}}{1 + C_{\rm 2} \left[\frac{1}{C_{\rm o}} + \frac{1}{C_{\rm 1}}\right]}, \qquad (1-15a)$$

This expression can be easily obtained by considering the differential capacitor network shown in Fig.  $^{1.5}$  c. The change of the minimum potential with respect to the surface flatband voltage  $\phi_{sF}$  is fairly constant. As we observe from Fig. 1.9 its value is about 0.8. The influence of the gate voltage upon the minimum potential is attenuated by the presence of the capacitors, that is, from Eq. (1-15a) we have

$$\frac{\partial \phi_{m}}{\partial \phi_{sF}} = \frac{1}{1 + c_{2} \left[ \frac{1}{c_{0}} + \frac{1}{c_{1}} \right]} < 1 \qquad (1-15b)$$

With the introduction of the p-n junction capacitance  $\mathbf{C}_2$ , we can express the gate capacitance  $\mathbf{C}_q$  in a neat form as seen by

$$C_{g} = C_{2} \frac{\partial \phi_{m}}{\partial \phi_{sF}} \qquad (1-15c)$$

The change of the minimum potential upon the charge in the signal charges can be expressed as

$$\frac{\partial \phi_{\mathsf{m}}}{\partial \mathsf{Q}} = \left[\frac{1}{\mathsf{C}_{\mathsf{O}}} + \frac{1}{\mathsf{C}_{\mathsf{T}}}\right] \frac{\partial \phi_{\mathsf{m}}}{\partial \phi_{\mathsf{SF}}} \tag{1-15d}$$

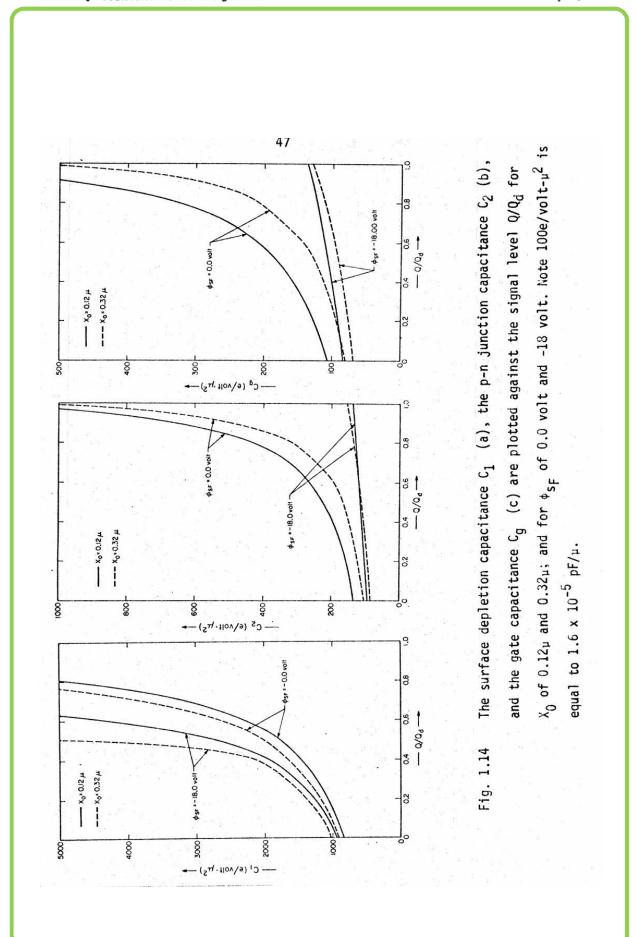

We have given all the important analytic formula for the gate capacitance and other important physical parameters. And from these equations above, we can obtain quantitatively how the capacitances  $C_1$ ,  $C_2$  and  $C_g$  depend on the salient physical parameters. The relevant calculations have been performed and the surface depletion capacitance  $C_1$ , the p-n junction capacitance  $C_2$ , and the gate capacitance  $C_g$  are plotted in Fig. 1.14a, 1.14b, and 1.14c respectively.

In practice during the operations of CCD, the amount of the signal charge Q would not be more than 50% of  $Q_d$ . Hence as seen in Eq. (1-15b) the change of the minimum potential upon the gate voltage is fairly constant, and its value is always around 0.8. This is because of the small p-n junction and capacitance  $C_2$  compared to the oxide and surface depletion capacitance,  $C_0$  and  $C_1$ . Figure 1.14c is useful when one wishes to estimate the load upon the clock-drive. For small signal level, we note the gate capacitance  $C_g$  is always about 100 e/volt· $\mu^2$ . If one drives the clock with 1 MHz with the voltage swing of 20 volts, the current to be supplied to the gate is 2 x  $10^9$  e/sec· $\mu^2$ . If the gate dimension is  $10\mu$  by  $100\mu$ , the current is 2 x  $10^{12}$  e/sec or about 0.32  $\mu$ A per gate. If one unit cell of the device consists of four gates, we must supply 1.28  $\mu$ A per bit. For a thousand bit shift-register, the current would be 1.28 mA.

It should be noted at this stage that the gate capacitance  $C_g$  so defined above is actually a function of the gate voltage  $\phi_{sF}$  and the signal charge Q. In a specific device operation, one more constraint

among the gate voltage  $\phi_{\text{SF}}$  , the signal charge 0 and the minimum potential  $\phi_{\text{m}}$  must be specified.

For example, in actual CCD operations, the signal charge Q is to move relatively slowly with respect to the gate voltage swing and the gate capacitance corresponds to the value with fixed signal charge while the gate voltage is changing. On the other hand, in the case of surface field-effect transistors with metallurgical p-diffusion channel, the signal (channel) charge Q can be supplied or extracted readily through the source and drain metallurgical contacts. The charge Q responds quickly to the gate voltage but the channel potential is fixed by the source and drain voltages while the gate voltage is changing rapidly.

An analytic expression for the gate capacitance  $C_q$  in terms of the gate potential  $\phi_{SF}$  and the signal charge Q can be obtained by tedious symbolic manipulations from Eq. (1-8). But the result can be expressed quite compactly by using the two parameters A and B defined by Eqs. (1-11c) and (1-11d). The gate capacitance is found to be as seen by

$$C_g = C_g (\phi_{SF}, Q) = \frac{N_d C_d}{N_A \sqrt{A^2 - B}}$$

(1-15e)

The gate capacitance is a very useful measure in estimating the clock load and the operation frequency. But when the dynamic charge transfer process in CCD is under consideration, the information regarding the channel potential  $\phi_{m}$  and the amount of the signal charge 0 is essential

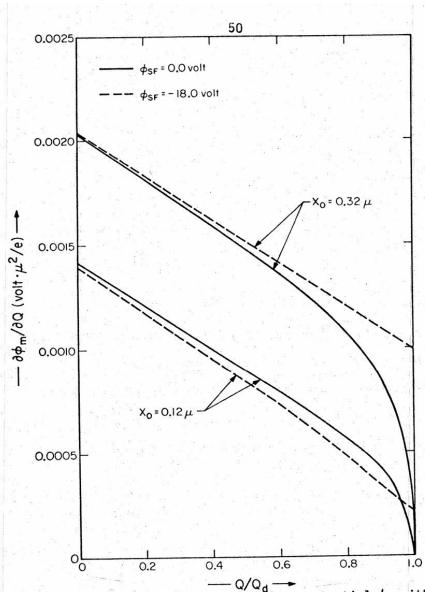

in the calculation of charge transfer efficiency. Specifically we must know how the channel potential  $\varphi_m$  depends on the signal charge Q. In Fig. 1.15 we have plotted the gradient of the minimum potential against the signal charge. Observe the dependence is quite linear upon the signal charge. That is, the actual dependence of the minimum potential upon the signal charge is quadratic as we have claimed earlier referring to Fig. 1.10a. The slope of the curves we see in Fig. 315 will be steeper for lighter p-diffusion doping level  $N_A$ . This point can be understood clearly from the relation given by Eq. (1-15d) if one notes that the p-n junction capacitance  $C_2$  is small compared to the oxide and surface depletion capacitance. In this case, we find, taking  $\partial \varphi_m/\partial \varphi_{SF} \approx 1.0$ ,

$$\frac{\partial^2 \phi_{\text{m}}}{\partial \Omega^2} \approx \frac{\partial}{\partial \Omega} \left[ \frac{1}{C_0} + \frac{1}{C_1} \right] = \frac{\partial}{\partial \Omega} \left[ \frac{1}{C_1} \right] \approx -\frac{1}{\varepsilon_{\text{Si}} N_{\text{A}}} \qquad (1-16a)$$

Or differentiating Eq. (1-10a) twice with respect to the signal charge Q, we obtain in a better approximation

$$\frac{\partial^2 \phi_{\text{m}}}{\partial O^2} \approx -\frac{1}{\varepsilon_{\text{Si}} N_{\text{A}}} \left[ 1 + \frac{N_{\text{d}}}{N_{\text{A}}} \right] f(R) \qquad , \qquad (1-16b)$$

where the factor f(R) is taken to be a constant with respect to the signal charge Q. The values of f(R) for Q = 0.0 is seen from Fig. 1.10 and are around 0.7. For  $\phi_{SF}$  = 0.0, Fig.1.15 shows  $\partial\phi_{m}/\partial Q$  = 0.0. This fact can be explained using Eq. (I-11b). For  $\phi_{SF}$  = 0.0, Q = Q<sub>d</sub> at E<sub>S</sub> = 0.0. E<sub>S</sub> = 0.0 gives X<sub>1</sub> = 0.0. Also Q = Q<sub>d</sub>

Fig. 1.15 The change of the minimum potential  $\phi_{\rm m}$  with respect to the change in the signal Q is plotted against the signal level. The fact that the slope is practically constant for small values of  ${\rm Q/Q_d}$  allows us to approximate  $\phi_{\rm m}$  by a quadratic function of the signal charge Q as seen in Eq. (1-17)

gives  $X_1 + X_2 = 0$ . Hence  $X_2$  is also zero. That is,  $C_1$  and  $C_2$  in Eqs. (1-15d) and (1-15b) must be infinite, resulting in  $\partial \phi_m/\partial Q = 0.0$ . Of course, this condition is outside of the normal device operations, and never realized in practice.

The fact that the slope is fairly constant for low signal level in Fig. 1.15 suggests a quadratic approximation of the minimum potential with respect to the signal charge 0. That is, we expand  $\phi_{\rm m}$  about 0 = 0.0 as a second order polynomial of 0 as seen by

$$\phi_{\rm m}(\phi_{\rm SF}, Q) \approx \phi_{\rm m}(\phi_{\rm SF}, 0) + \frac{\partial \phi_{\rm m}}{\partial Q} \left| Q + \frac{1}{2} \frac{\partial^2 \phi_{\rm m}}{\partial Q^2} \right| Q^2$$

(1-17)

The values of  $\phi_{\rm m}(\phi_{\rm SF},0)$  have been plotted in Fig. 1.9. The values of the coefficients of the second and third terms have been calculated exactly. And the values of the potential calculated by Eq. (1-17) agree with the exact values by Eq. (1-10) within the errors of 0.1% for the range of interest. If we had plotted these values on the Fig. 1.10a the corresponding points fall on the lines, and there is no way to see the differences in the figure.

When one analyzes the dynamic charge transfer process in CCD, it is very important to express the minimum potential in the form given by Eq. (1-17). In the analysis, one is interested in the signal charge Q and the minimum potential  $\phi_m$ . The simpler the relation between these two quantities  $\phi_m$  and Q is expressed, the better for the charge transfer analysis in multi-gate structures.

## 1.7 Gaussian Doping Profile

For uniformly doped abrupt p-n junction, the depletion approximation gives excellent agreements with the exact solution which is solved numerically using Eq. (1-6). For much realistic devices the doping in the p-diffusion layer is typically introduced by ion-implantation followed by drive in diffusion. The resulting fixed charge distribution is a Gaussian doping profile characterized by the two parameters, the surface charge density  $N_{\rm S}$  and the p-n junction depth  $X_{\rm g}$ . To apply the results of the previous sections we first describe the procedure to obtain the effective p-diffusion density  $N_{\rm A}$  and the effective diffusion depth  $X_{\rm d}$  from  $N_{\rm S}$  and  $X_{\rm g}$ . This correlation allows us to estimate the general dependence of the minimum potential  $\phi_{\rm m}$  and the gate capacitance  $C_{\rm g}$  on other salient physical parameters.

In this case, the fixed charge distribution d(x) can be given quite accurately by a Gaussian profile as seen by

$$d(x) - N_d - (N_s + N_d) \exp \left[-\alpha^2 (\frac{X}{X_g})^2\right]$$

, (1-18a)

and

$$\alpha^2 = \ln \left( 1 + \frac{N_s}{N_d} \right) \qquad , \qquad (1-18b)$$

where N is the surface density of the p-diffusion layer and X is the position of the p-n junction of the semiconductor. The total sheet charge density  $Q_d$  in the p-diffusion layer is then given by

$$Q_{d} = -\int_{0}^{X_{g}} d(x)dx > 0$$

(1-19a)

This quantity may be thought of as the product of the effective average doping density  $N_{\mbox{A}}$  and the effective depth  $X_{\mbox{d}}$  of the p-diffusion layer. That is, as before

$$Q_{d} = N_{A}X_{d} \qquad (1-19b)$$

If we take the effective depth of the p-diffusion layer to be equal to the p-n junction depth, that is,  $X_d = X_g$ , then the relation (1-19b) determines the value of the effective doping  $N_A$ . However, the exact numerical calculation of the electrostatic potential gives a better agreement to the solution of the depletion approximation if we choose the effective depth to be at the reflection point of the Gaussian doping profile. By differentiating Eq. (1-18a) twice with respect to x and setting it to be zero, we obtain

$$X_{d} = \frac{X_{g}}{\alpha} \qquad (1-20)$$

That is, for a Gaussian doping profile, the effective depth is actually shallower and the position of the minimum potential is closer to the oxide-semiconductor interface. Consequently, the signal charge will be transferred along the potential valley closer to the interface.

The effective p-diffusion density  $N_A$  can be obtained by Eq. (1-19b) if the actual value of  $Q_d$  is computed from Eq. (1-19a) for the doping profile d(x) given by Eq. (1-18a). The result is given as seen by

$$Q_{d} = -N_{d}X_{q} \left[ 1 - \frac{\sqrt{\pi} \exp(\alpha^{2})}{2\alpha} \operatorname{erf}(\alpha) \right] \qquad (1-20b)$$

This quantity  $Q_d$  is by definition equal to  $N_A X_d$  by Eq. (1-19b). Hence from Eq. (1-20a)  $X_d/X_g=1/\alpha$ . Hence we have

$$N_{A} = \frac{Q_{d}}{X_{d}} = N_{d} \left[ \frac{1}{\alpha} - \frac{\sqrt{\pi} \exp(\alpha^{2})}{2\alpha^{2}} \operatorname{erf}(\alpha) \right] \qquad (1-20c)$$

Therefore, we observe  $X_d/X_g$ ,  $N_A/N_d$  and  $Q_d/N_dX_g$  are all functions of  $\alpha$ , hence,  $N_s/N_d$  only.

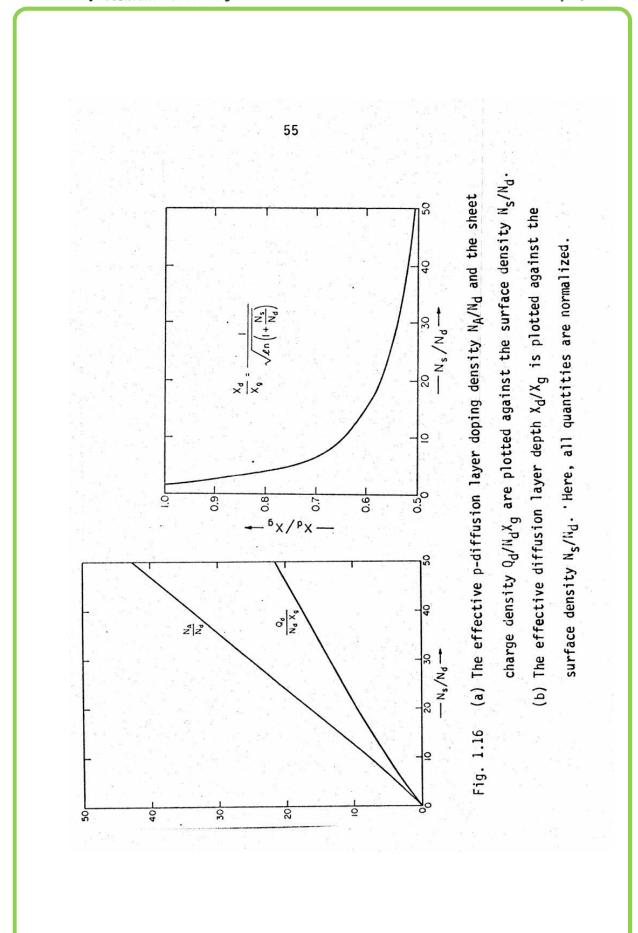

In Fig. 1.16a the effective average doping  $N_A$  and the sheet charge density  $Q_d$  are plotted against the surface doping  $N_s$ . The units are normalized by the substrate doping  $N_d$  for  $N_A$  and  $N_s$ , and  $N_d X_g$  for  $Q_d$ . In Fig. 1.16b the effective diffusion layer depth  $X_d$  is plotted also against  $N_s/N_d$ .

We have now established a procedure to correlate the results of the uniform doping case to that of the Gaussian doping case. And the general characteristics of the potential profile and charge distribution can be easily compared for both cases.

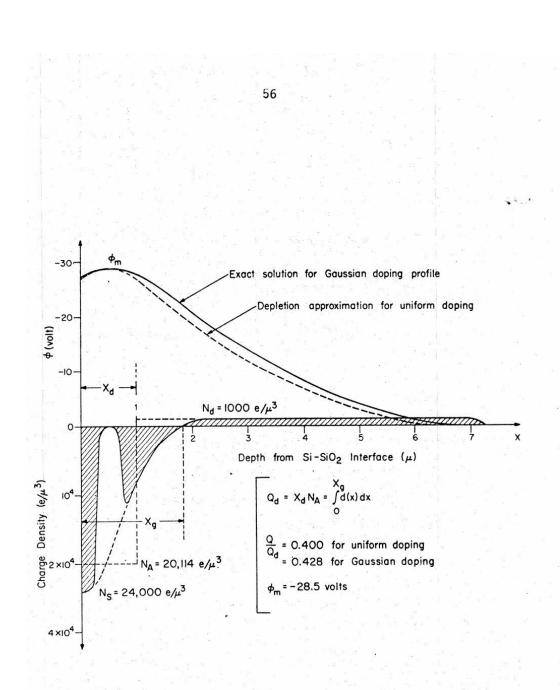

In Fig. 1.17 the approximate potential profile is compared with the exact numerical solution. Observe that in the p-diffusion layer, the charge distribution is such that the entire signal charge packet is a neutral zone. The signal charge packet arranges itself according to the doping concentration so that the electrostatic potential is at its minimum value in the entire neutral signal charge packet.

Fig. 1.17 The potential profiles  $\phi$  by the depletion approximation and the exact numerical solution of the Gaussian doping profile are compared. X  $_d$ =1.0  $_\mu$  and the p-layer doping N  $_A$  of 20,000e/ $\mu^3$ .

The oxide thickness  $X_0$  is taken 0.32 and the gate voltage  $\phi_{sF}$  equal to -18.0 volt. Since the gate voltage is fixed, the minimum potential  $\phi_{m}^{-}$  and the signal charge Q are not independent to each other. Demanding the minimum voltage  $\phi_{m}$  to be -28.5 volts, the corresponding signal charge  $\mathrm{Q/Q}_\mathrm{d}$  is 0.400 for uniform doping and 0.428 for Gaussian doping. In principle, it is possible to fix the signal charge  $Q/Q_d$  to be 0.400 and obtain the corresponding minimum potential  $\boldsymbol{\varphi}_{\boldsymbol{M}}$  for the uniform doping (which is -28.5 volt as before) and for the Gaussian theory case (which will be slightly lower than -28.5 volt) respectively. But the actual numerical computation for the Gaussian Profile case turns out easier if the minimum potential  $\phi_{\text{m}}$  is fixed at the start rather than Q. This fact can be understood easily if one recalls the form of the Poisson's equation (1 - 6b) in the p-channel region, which includes the minimum potential  $\boldsymbol{\varphi}_m$  in the expression. Then after computing the potential  $\phi(x)$  as a function of the spatial coordinate X, we obtain the amount of the signal change from the relation given by

$$Q = -\int_{0}^{X_{g}} d(x) \exp\left(\frac{\phi_{m} - \phi}{kT}\right) dx = Q_{d} - \varepsilon_{S_{i}} \frac{\partial \phi}{\partial x} \Big|_{x=0} + \varepsilon_{S_{i}} \frac{\partial \phi}{\partial x} \Big|_{x=0}$$

$$(1-20d)$$

which gives the total signal charge from the minimum potential  $\varphi_{m}$  and the electrostatic potential profile  $\varphi.$

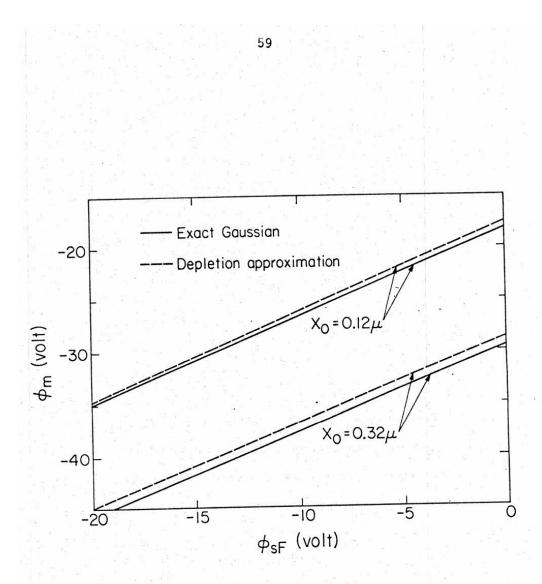

We are now in the position to describe the general dependence of the minimum potential  $\phi_m$  and the gate capactiance  $C_g$  for the case of the Gaussian doping profile and compare with the approximation made by the depletion approximation.

For our case study, the surface doping density N<sub>S</sub> is taken to be 24,000 e/ $\mu^3$  and the effective p-diffusion layer depth X<sub>d</sub> to be 1 . Then, from Fig. 1.12a or Eq. 1-20c, the effective p-layer density N<sub>A</sub> is found to be 20,114 e/ $\mu^3$ . The corresponding actual p-n junction depth X<sub>g</sub> for the Gaussian doping profile is found from Fig. 1.16b or Eq. (1-20a) to be 1.82  $\mu$ . The substrate doping is fixed and taken to be 1000 e/ $\mu^3$ . The dependence of the minimum potential  $\phi_m$  upon the gate voltage ( $\phi_{SF}$ ) for zero signal charge Q = 0.0 is illustrated in Fig. 1.18 for comparison with the results of the depletion approximation.

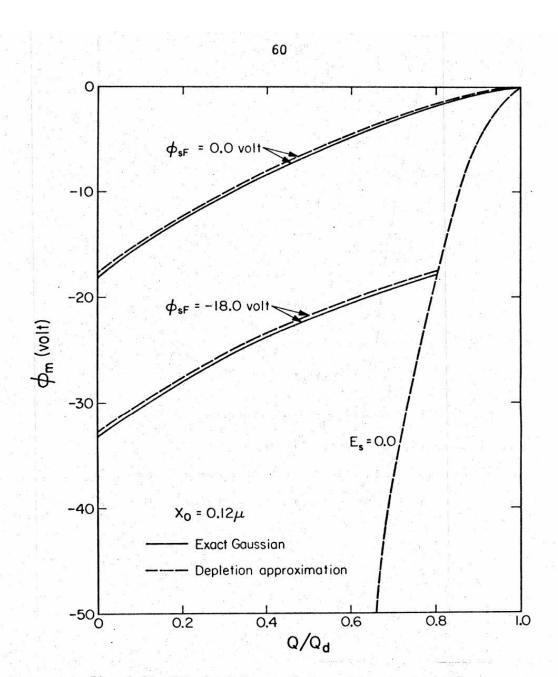

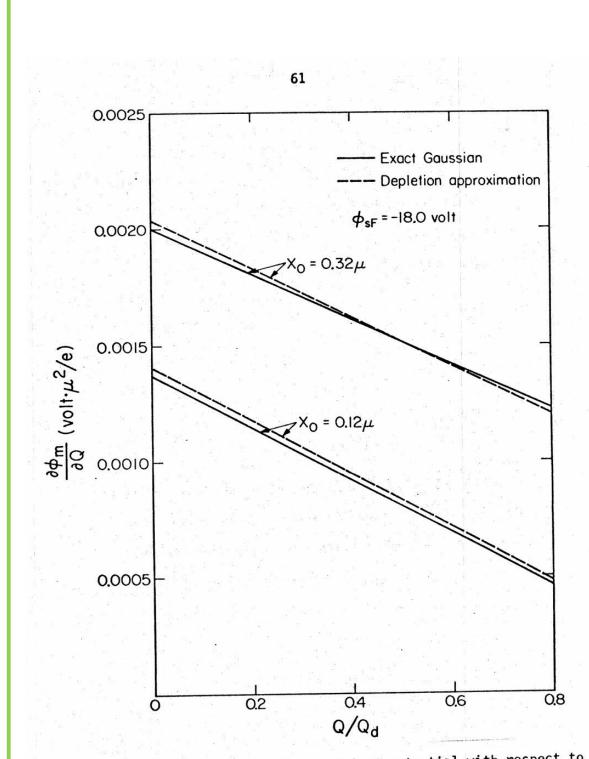

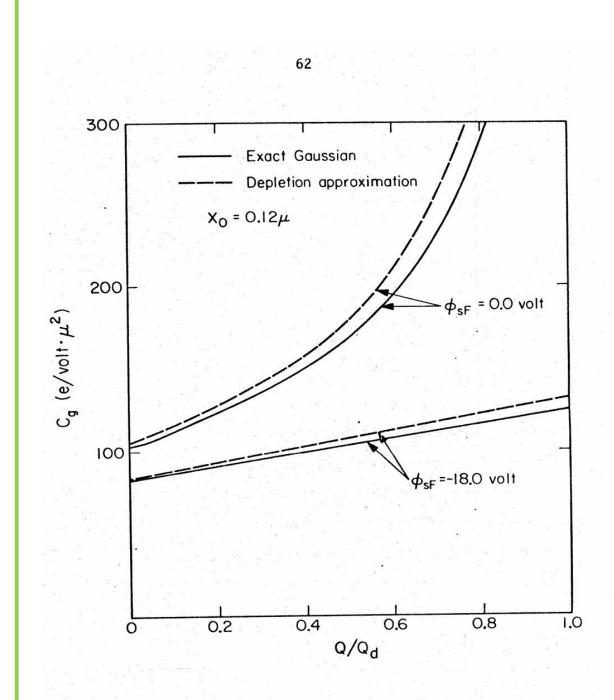

Figure 1.19 shows the dependence of the minimum potential  $\phi_m$  upon the signal charge. The illustration format is similar to Fig. 1.10a The slope of the minimum potential shown in Fig. 1.19 is plotted in Fig. 1.20. The gate capacitance  $C_g$  for the Gaussian doping case is also plotted in Fig. 1.21. The solutions of the exact numerical calculation for the Gaussian profile follows the general characteristics of the solutions obtained by the depletion approximation with surprising accuracy.

There may be several ways to compute the minimum potential and other salient physical parameters in the exact numerical calculations. We outline below one possible procedure to obtain the gate capacitance  $\mathbf{C}_{\mathbf{G}}$  and other relevant physical parameters.

By numerical calculations, we can obtain the electrostatic potential everywhere inside the semiconductor. The equation to be solved numerically is given by Eq. (1-6) and identified to be the form of a nonlinear differential equation seen by

Fig. 1.18 The dependence of the minimum potential upon the flat band surface potential  $\phi_{SF}$  defined by Eq. (1-7c) is illustrated for different oxide thickness  $X_0$  for the Gaussian doping profile .

Fig. 1.19 The dependence of the minimum potential upon the signal charge is **il**lustrated for the case of the Gaussian doping profile. Observe the similar characteristics between Fig. 1.10a and this figure.

Fig. 1.20 The change of the minimum potential with respect to the change in the signal charge is illustrated for a Gaussian doping profile. Observe for the range of interest, the slope is fairly constant.

Fig. 1.21 The format is similar to Fig. 1.14c. The gate capacitance  ${\rm C_g}$  for the Gaussian doping case is plotted against the signal charge Q. Observe the similar characteristics between Fig. 14c and this figure. The values are computed by Eq. (-14a) numerically.

$$\frac{\partial^2 \phi}{\partial x^2} = f(\phi, x) \qquad \text{for} \qquad 0 < X < \infty \qquad . \qquad (1-20a)$$

The boundary condition at the  $Si-Si0_2$  interface is given by Eq. (1-8b) and can be written as

$$\phi = \phi_{SF} + \frac{\varepsilon_{Si}}{C_0} \frac{\partial \phi}{\partial x} \quad \text{at} \quad x = 0 \qquad (1-20b)$$

At  $x = \infty$ , that is, deep in the substrate, the potential is grounded, hence we have the remaining boundary condition:

$$\phi = 0.0$$

at  $x = +\infty$  . (1-20c)

Solving Eq. (1-20) we obtain the potential  $\phi(x)$  as a function of the spatial coordinate everywhere for  $0 \le x \le \infty$ . In order to calculate the derivatives of the salient physical parameters, we introduce a parameter  $\psi$  defined by

$$\psi = \frac{\partial \phi}{\partial \phi_{cF}} \qquad (1-21a)$$

Then, corresponding to Eq. (1-20) by differentiating them with respect to  $\phi_{sF}$  we obtain an ordinary linear differential equation with respect to  $\psi$  given as

$$\frac{\partial^2 \psi}{\partial x^2} = g(x)\psi(x) \qquad \text{for} \qquad 0 < x < \infty \qquad , \qquad (1-21b)$$

where the boundary conditions for this corresponding case are given by

$$\psi = 1 + \frac{\varepsilon \text{Si}}{C_0} \frac{\partial \psi}{\partial x}$$

at  $x = 0.0$  (1-21c)

and

$$\psi = 0.0$$

at  $x = \infty$  , (1-21d)

where

$$g(x) = \frac{\partial f(\phi, x)}{\partial \phi(x)} = g(\phi(x), x) \qquad (1-21e)$$

Solving Eq. (3-21) we obtain  $\psi(x)$  everywhere for  $0 < x < \infty$ . Hence from Eq. (3-14a) we obtain the gate capacitance  $C_g$  by the relation

$$C_{g} = -\epsilon_{Si} \frac{\partial \psi}{\partial x}$$

$$x = 0$$

(1-22a)

From the solution  $\phi(x)$  of the Eq. (1-21), we obtain the minimum potential  $\phi_m$  and its location  $X_m$ . Then we can identify  $\partial \phi_m/\partial \phi_{SF}$  to be the value of  $\psi$  at  $X=X_m$ . That is,

$$\frac{\partial \phi_{m}}{\partial \phi_{sF}} = \psi(X_{m}) \qquad (1-22b)$$

Then from Eq. (1-15c) we can compute the p-n junction capacitance  ${\rm C_2}$ . Then from the relation (1-14b) we have the surface depletion capacitance  ${\rm C_1}$ , The change of the minimum potential with respect to the signal charge can be computed from Eq. (1-15d).

## 1.8 Conclusion

Since buried channel CCD operates in the reverse biased p-n junction depletion region, which is under thermal nonequilibrium, care must be taken in specifying the form of the Poisson's equation applicable for the structure. Unlike the surface CCD, the signal is to be transferred as a neutral packet away from the semiconductor-oxide interface and the concept of quasi-fermi levels has to be specified in

order to obtain the electrostatic potential and the signal level. By linear depletion approximation the relations among the minimum potential and other physical parameters are studied in detail. The procedure for the Gaussian profile to obtain the effective p-diffusion density  $N_A$  and effective depth  $X_d$  from the surface density  $N_s$  and the p-n junction depth  $X_g$  is presented. The agreement between the exact numerical calculation and the analytic approximation presented in this paper has been shown to be excellent. The actual numerical computation is outlined and we believe the detailed results presented in this presentation will serve as a useful reference and guide-work for those people who are designing the device and studying the transfer mechanism in details. This work is a stepping stone to the two dimensional analysis of buried channel CCD structures which begins with the analysis given herein as basis.

## IMPORTANT FORMULAS

1. Minimum Potential  $\phi_m$

$$\phi_{m} = -\left(1 + \frac{N_{d}}{N_{A}}\right) \left(\phi_{d} - \phi_{sF}\right) f(R)$$

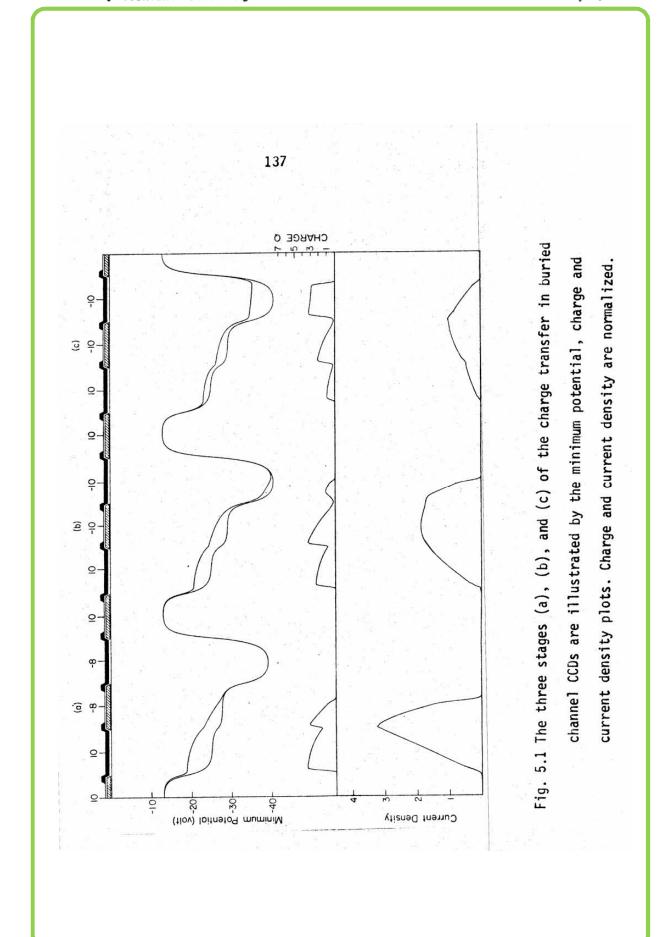

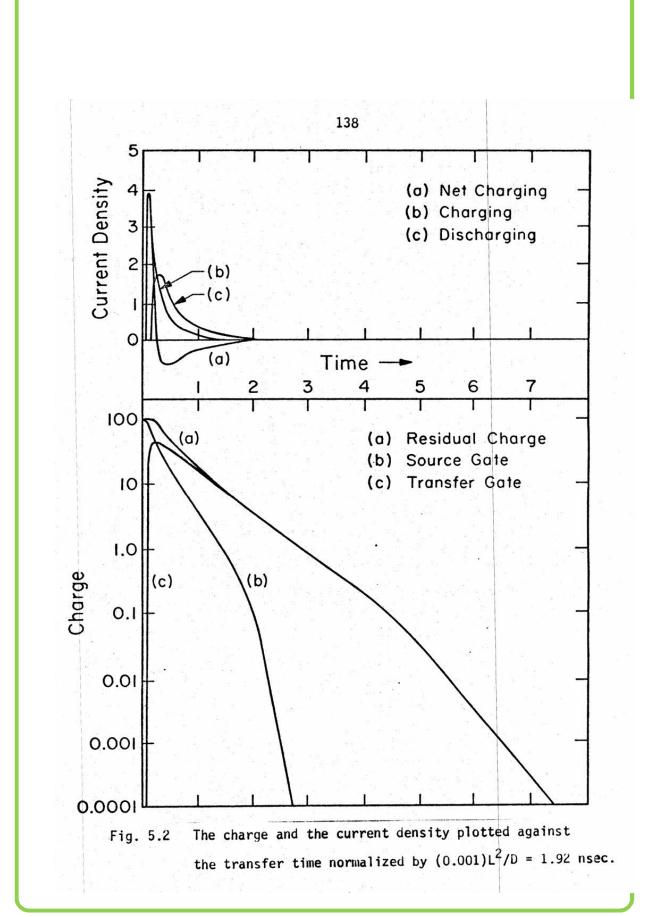

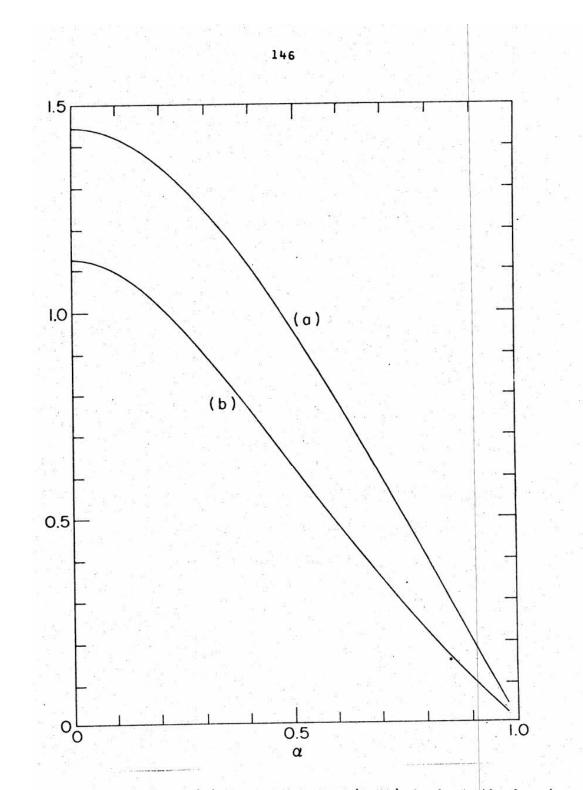

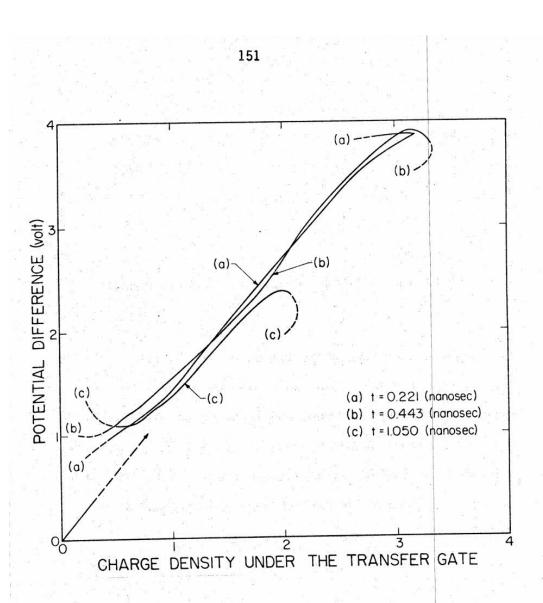

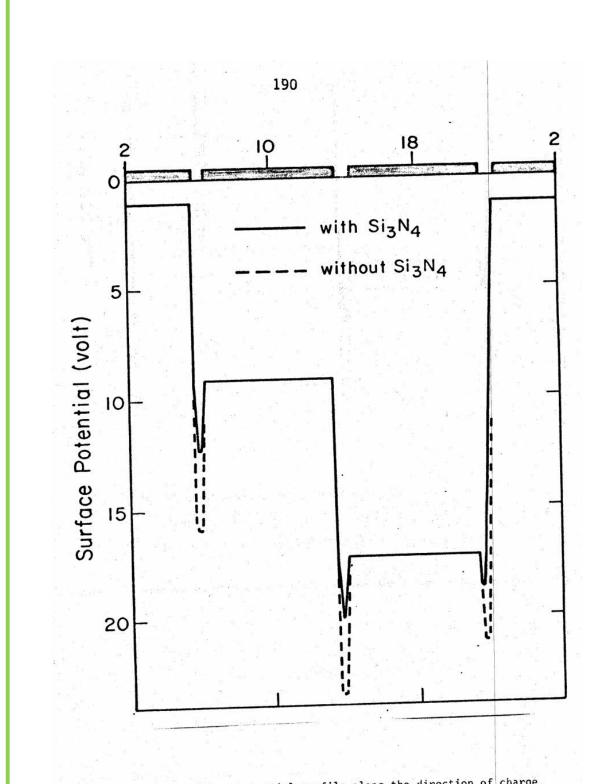

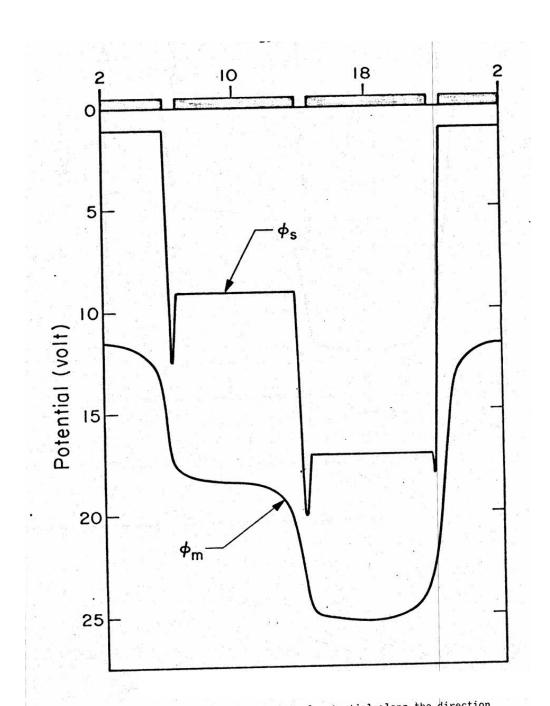

$$\phi_{t} = \frac{N_{A} \epsilon_{Si}}{2C_{o}^{2}}$$