Slide_Sony_Atsugi_Tech_2020_07_10_Slide041_to_050.html

by Yoshiaki Daimon Hagiwara

***************************

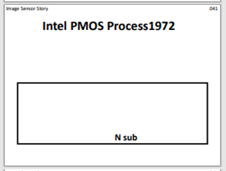

Slide041

***************************

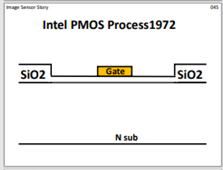

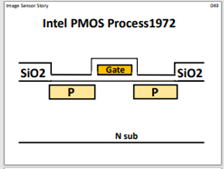

1972年当時は Intel社は PMOS Transistorの商品化に最初成功しました。

NMOSより、PMOS Transistorの方が シリコン表面の固定電荷Qssの抑圧

が簡単だったからです。しきい値の制御に Qss/Co の項の影響は非常

に大きく、固定電荷Qssの変動はしきい値 Vth の変動となり現れて歩留

まり低下の原因でした。それで PMOS Transistor から手がけました。

PMOS Transistor では、Source と Drain 領域を P typeの拡散層で形成

しますので、N type 基板を用います。

***************************

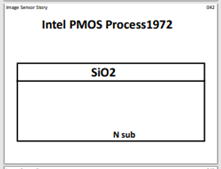

Slide042

***************************

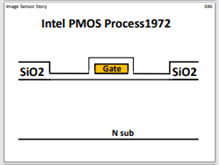

まず、N type 基板の表面を酸化します。

***************************

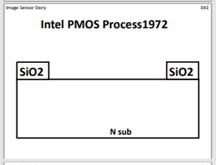

Slide043

***************************

PMOS Transistorの Active 領域を定義し、その部分の酸化膜を除去します。

***************************

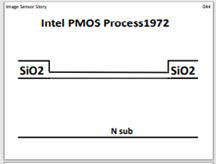

Slide044

***************************

再びその領域を薄く酸化し、Gate 酸化膜として後で使います。

***************************

Slide045

**************************

PMOS Transistorの Polysilicon 電極を形成します。

***************************

Slide046

***************************

PMOS Transistorの Polysilicon 電極の表面を酸化し保護します。

***************************

Slide047

***************************

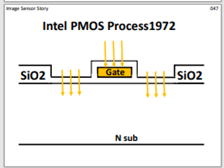

次に Polysilicon 電極 と Active 領域の回りの 厚いFiled 酸化膜を

mask として、イオン打ち込みで source と drain を形成します。

ここで熱拡散による従来の source と drain を形成と違って、

Intel社は イオン打ち込み技術により source と drain を形成しました。

イオン打ち込み技術の場合は、そのsource と drain 領域の不純物原子の

ピーク濃度の位置を、シリコン表面だけでなく、自由に深さを制御できます。

これは KNOWHOWで当時は企業秘密でした。

でもだれでも気が付くことで、Intel社は あえて 特許にしなかったと記憶します。

***************************

Slide048

***************************

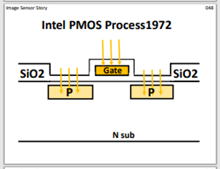

その結果、source と drain 領域は、図の様に 埋め込みP層になりました。

***************************

Slide049

***************************

後は金属コンタクトを このsource と drain 領域と Polysilicon 電極に

つける必要がありますが、さてこの後は Intelはどうしたでしょうか?

***************************

Slide050

***************************

単純にまず、金属コンタクト様に 酸化膜に窓を開けます。

More Slides :

*****************************************************

Slide051_to_060

Slide061_to_070

Slide071_to_080

Slide081_to_090

Slide091_to_100

Slide101_to_110