*******************************************************************

Story of Pinned Photo Diode

hagiwara-yoshiaki@aiplab.com

Hagiwara at Sony is the true inventor of Pinned Photo Diode.

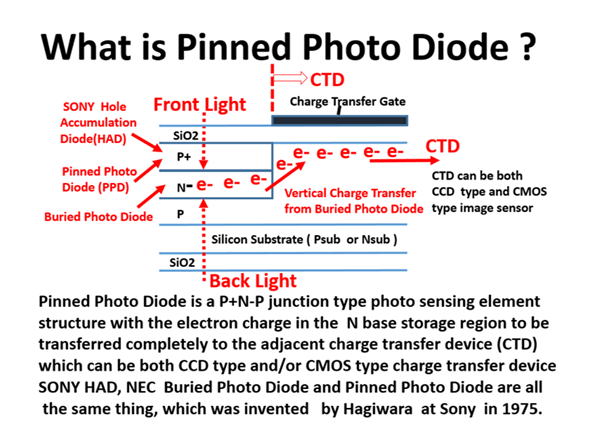

See also ElectronicsStackExchangeSite on What is Pinned Photo Diode ?

*******************************************************************

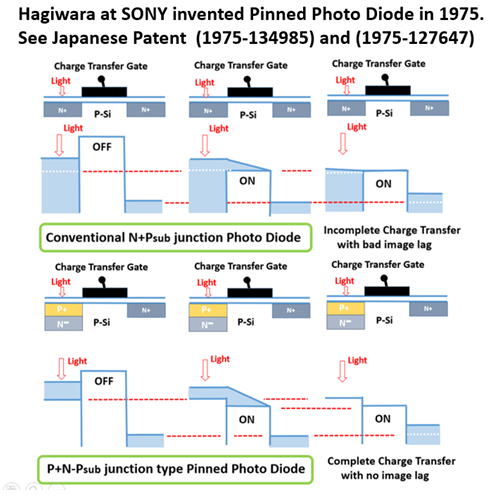

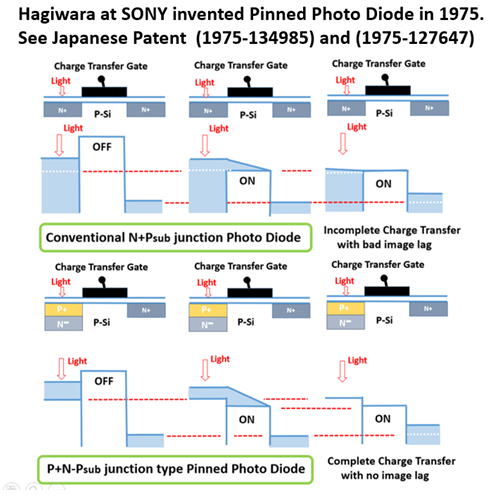

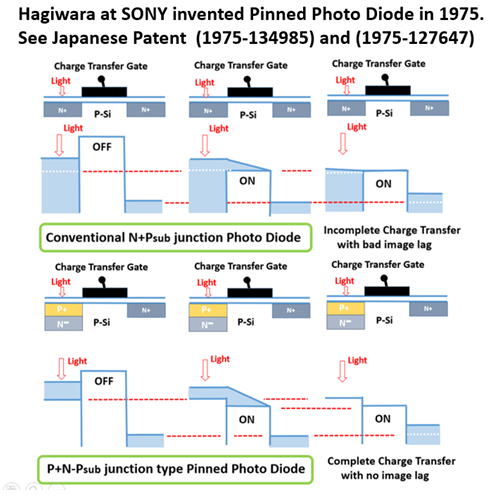

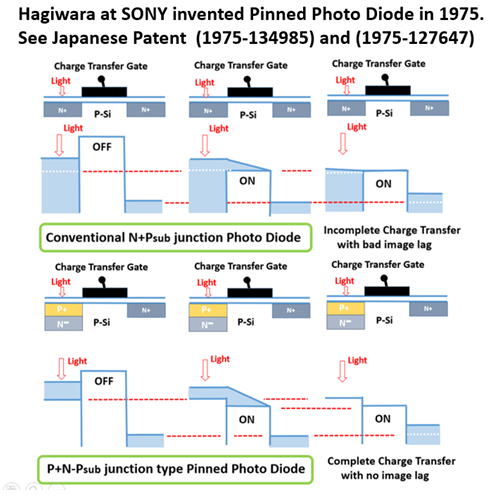

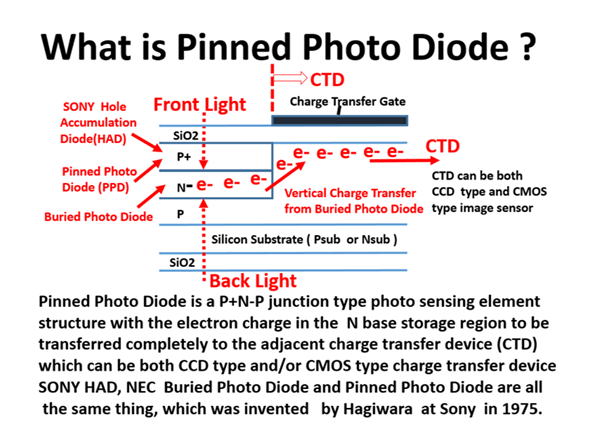

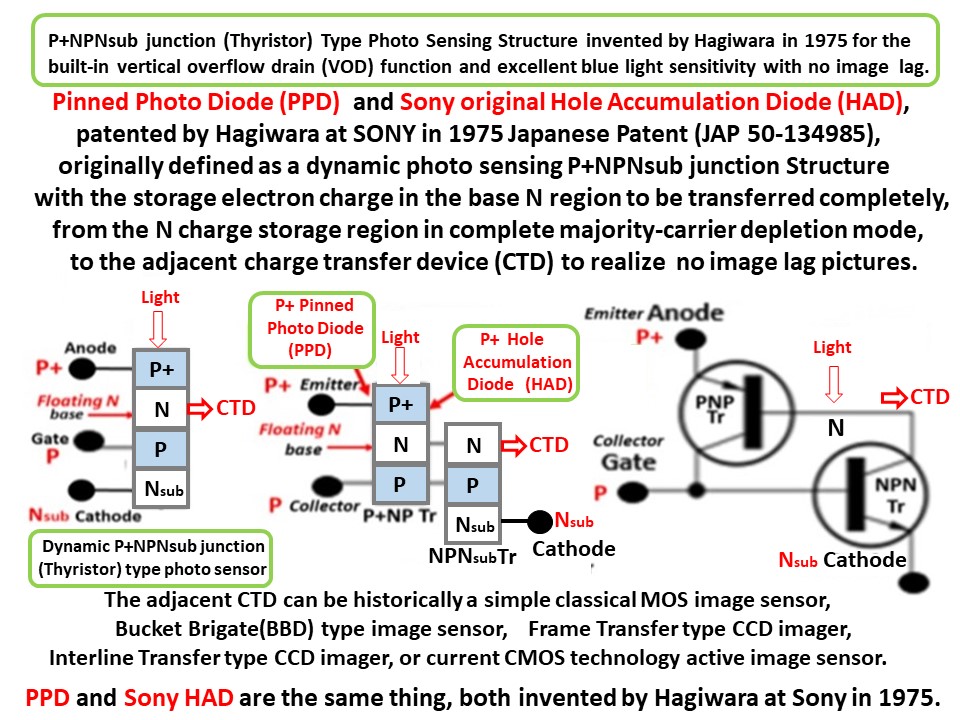

Pinned Photo Diode was invented by Hagiwara of Sony in 1975

Return to The AIPS ( Artificial Intelligent Partner System ) Home Page

Top :

http://www.aiplab.com

*******************************************************************

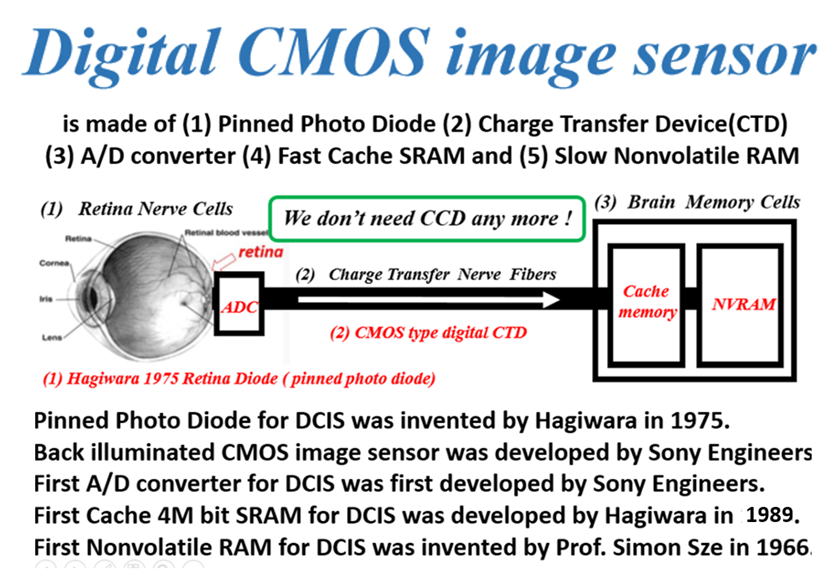

Brief History of Image Sensors.

*******************************************************************

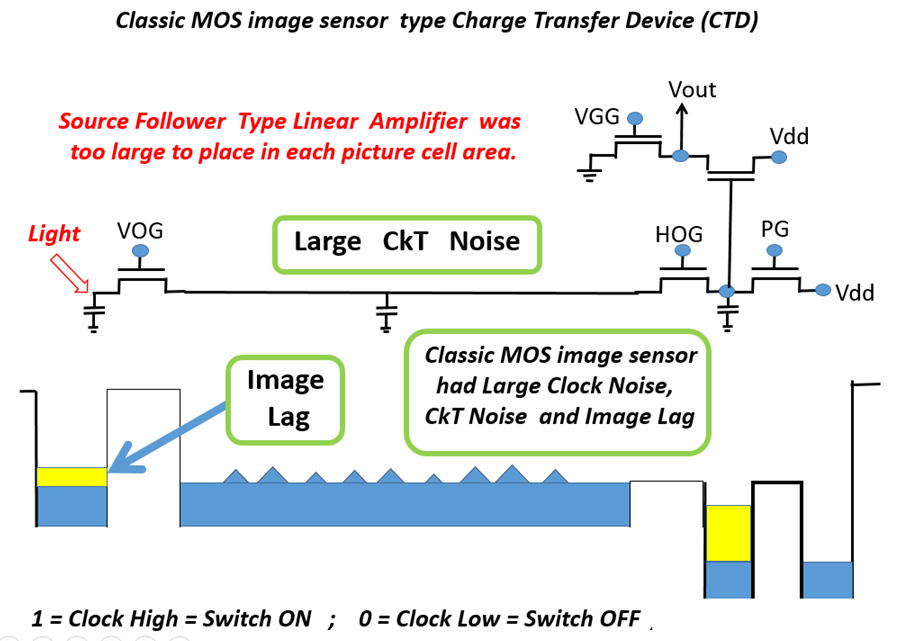

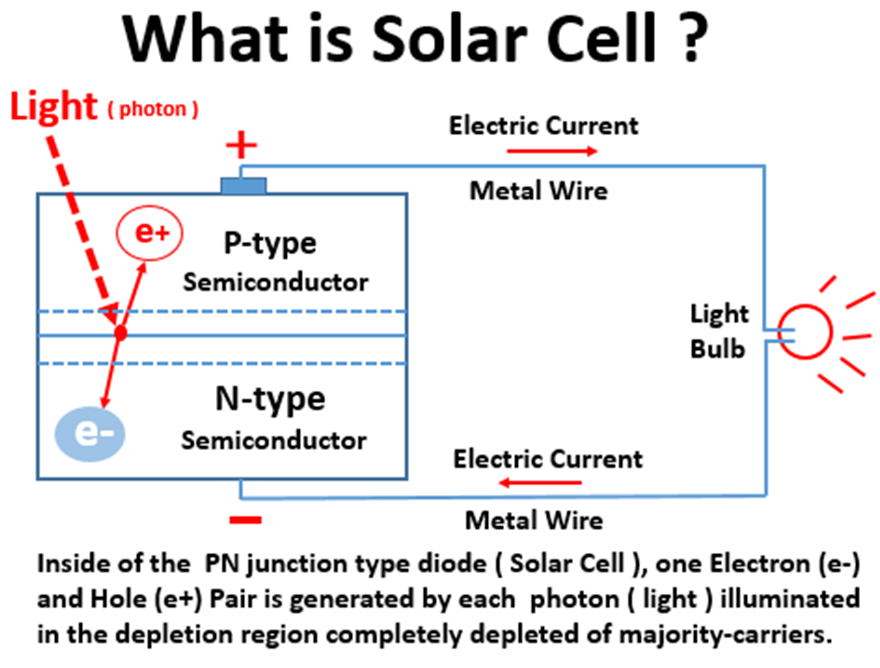

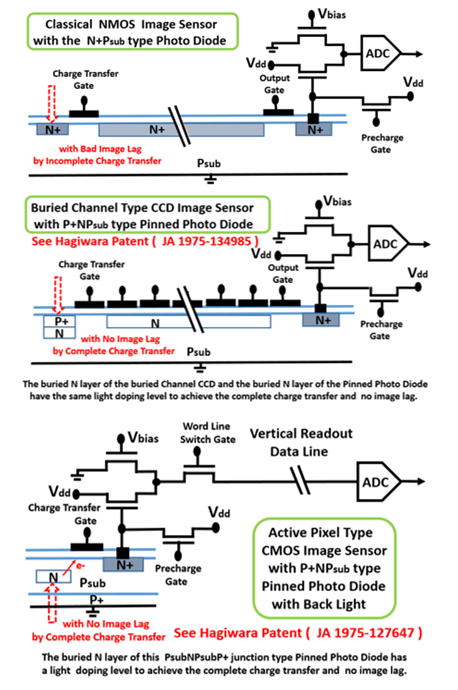

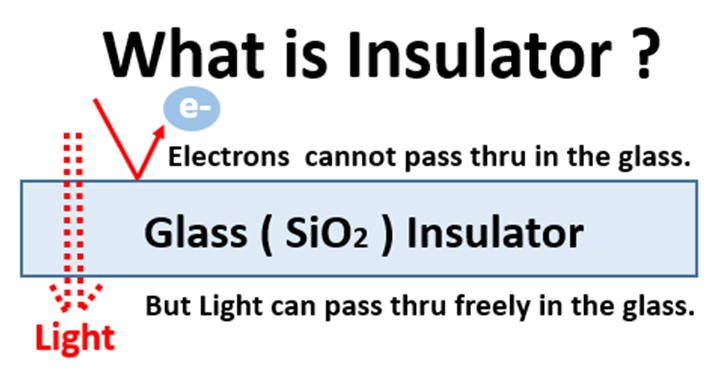

In 1960s, before CCD was invented, we already had beautiful color pictures

by the classical MOS image sensor with an excellent light sensitivity obtained

by the classical N+P junction type photo diode.

But to overcome the very large wire (CkT) noise, the three transistor

active source follower type circuits, invented by Peter Noble, was needed.

But the picture cell area was too small to incorporate this active circuit

in each picture cell area. We all knew that we had to wait untill we have

the complete MOS transistor process scale down, much furthur down.

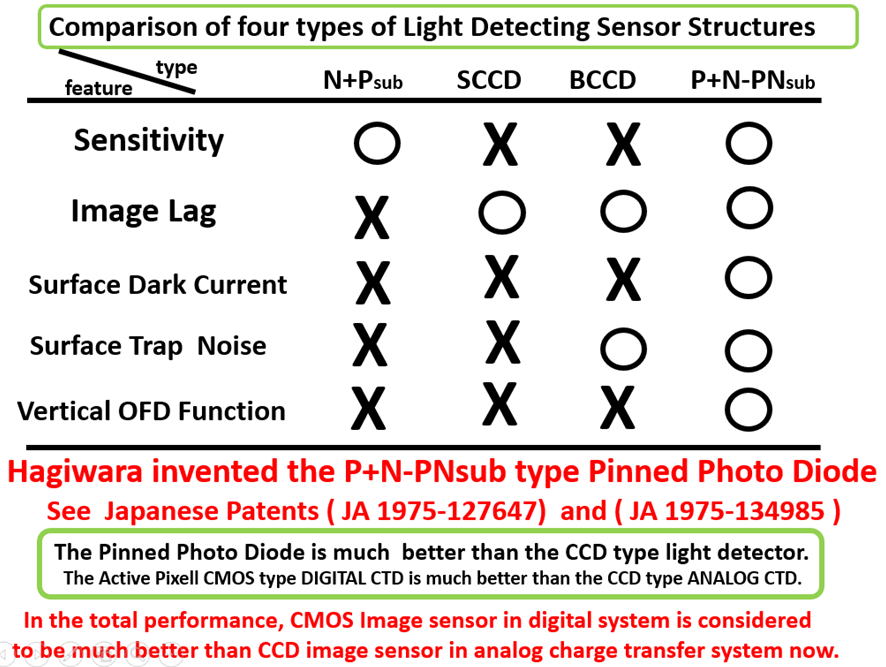

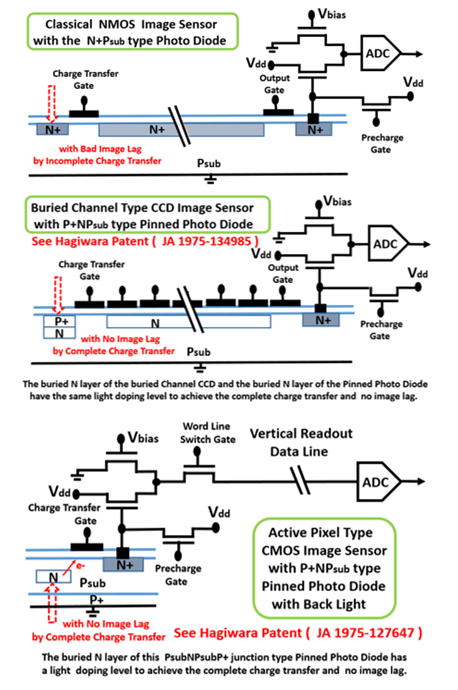

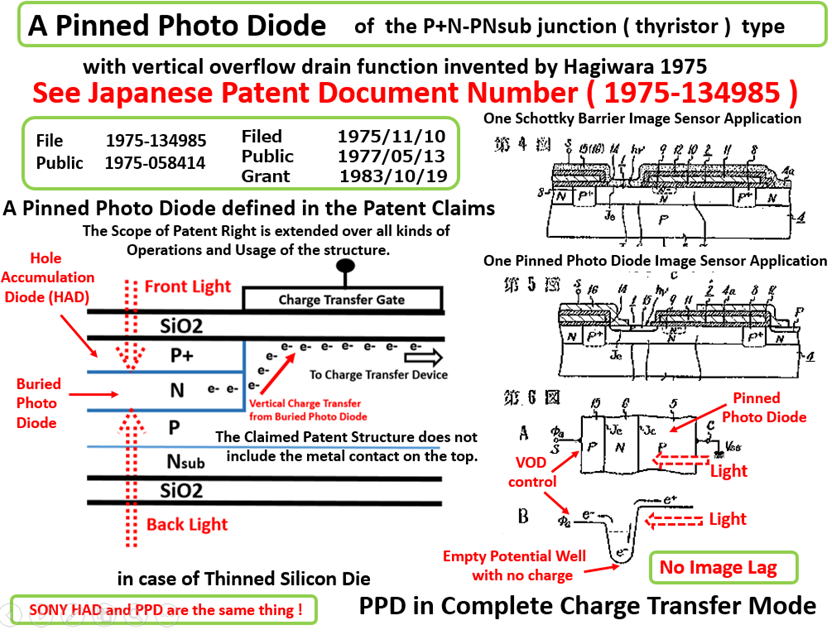

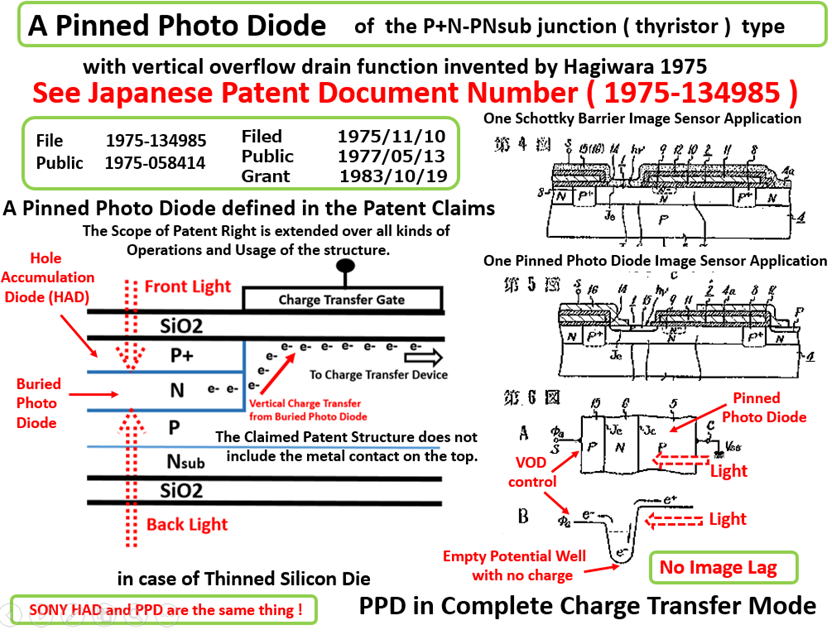

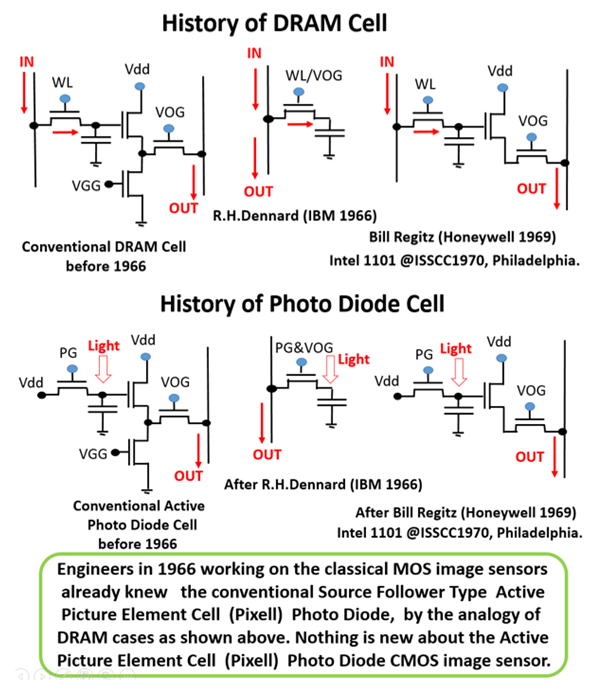

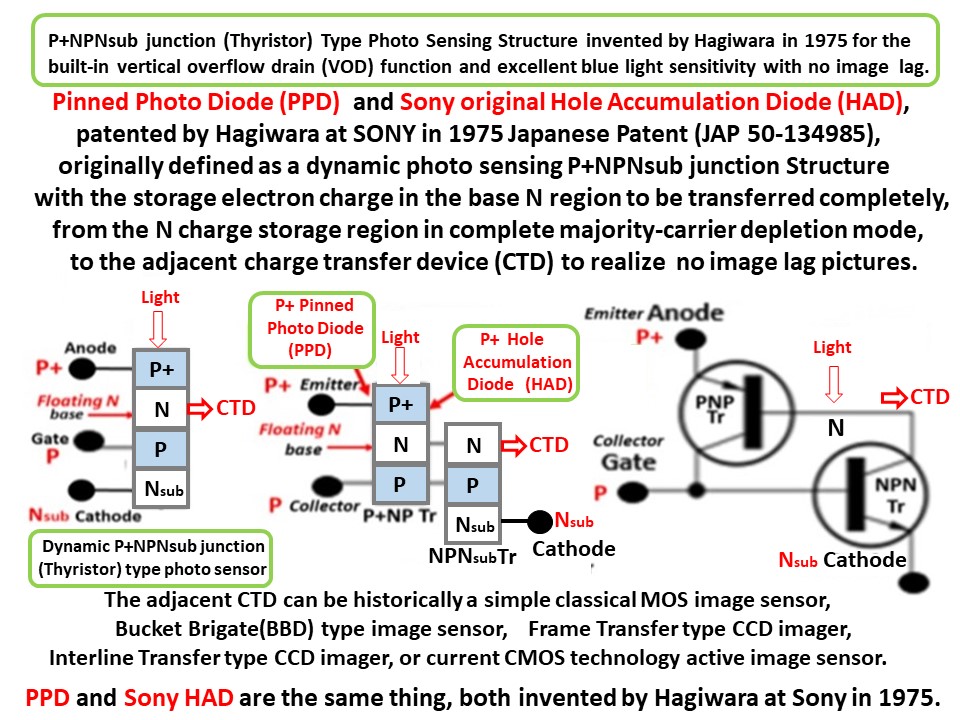

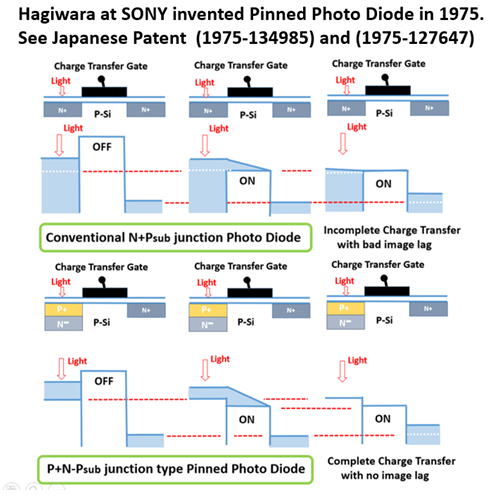

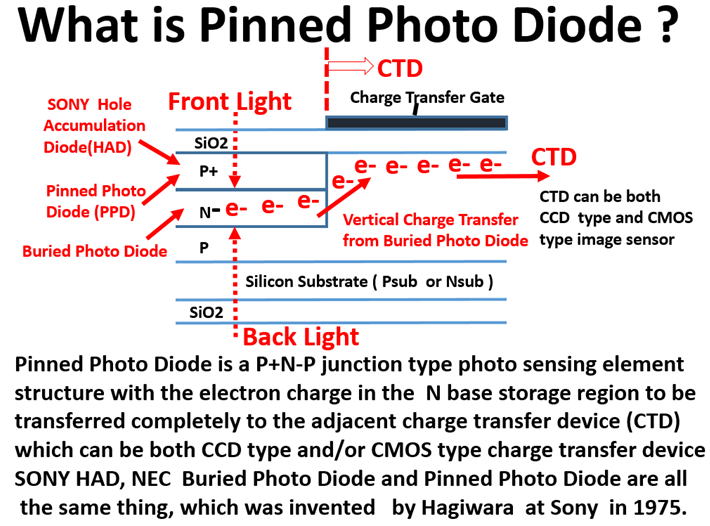

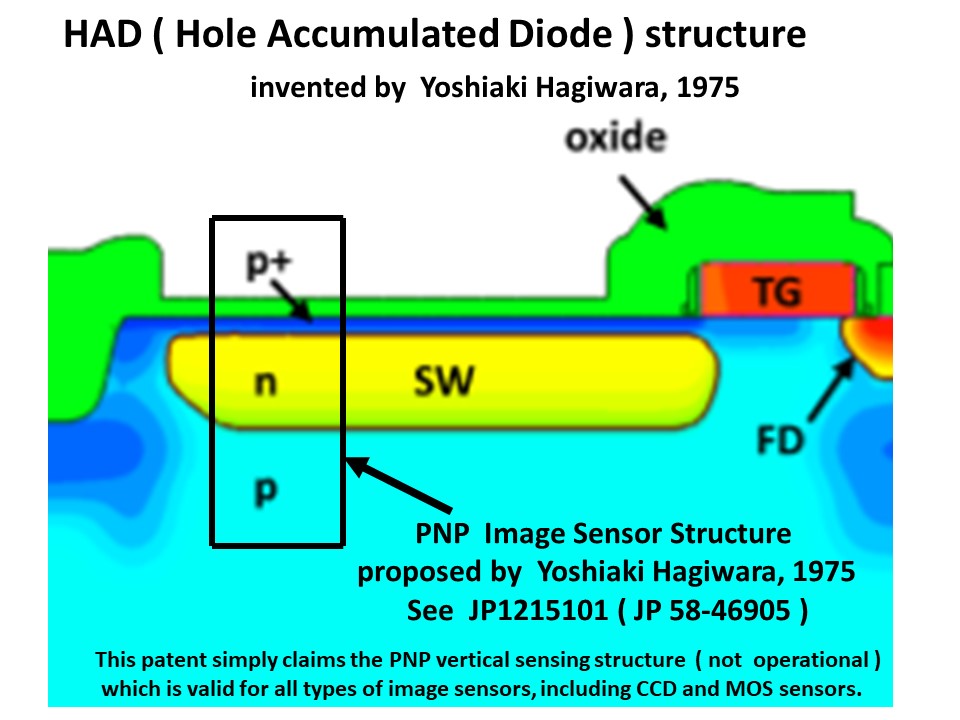

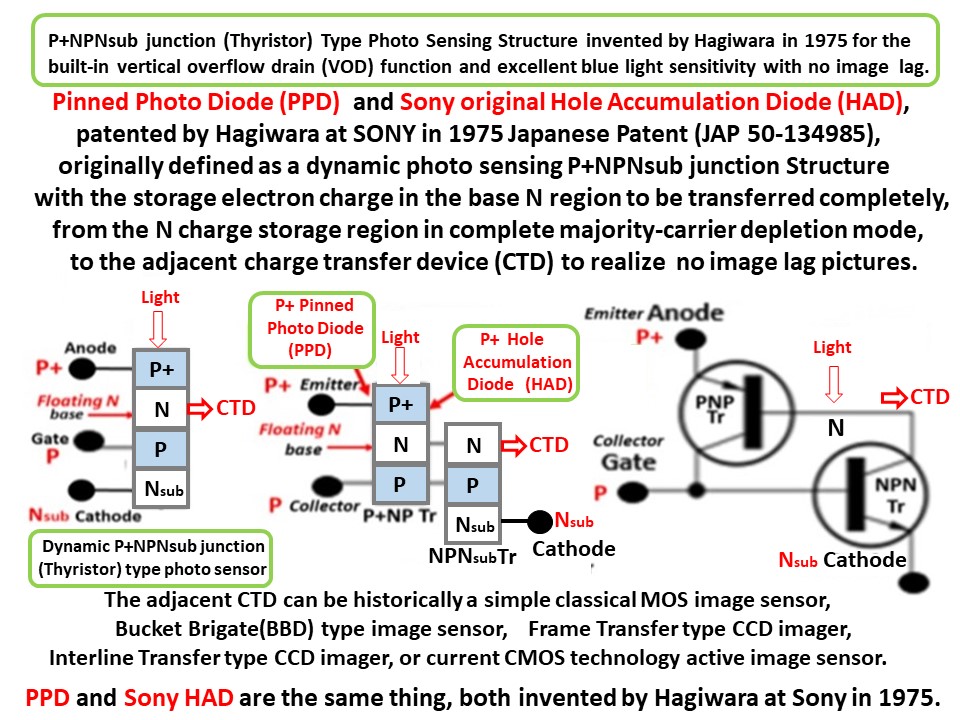

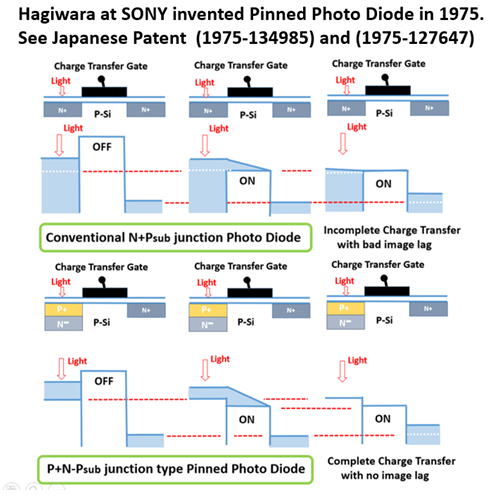

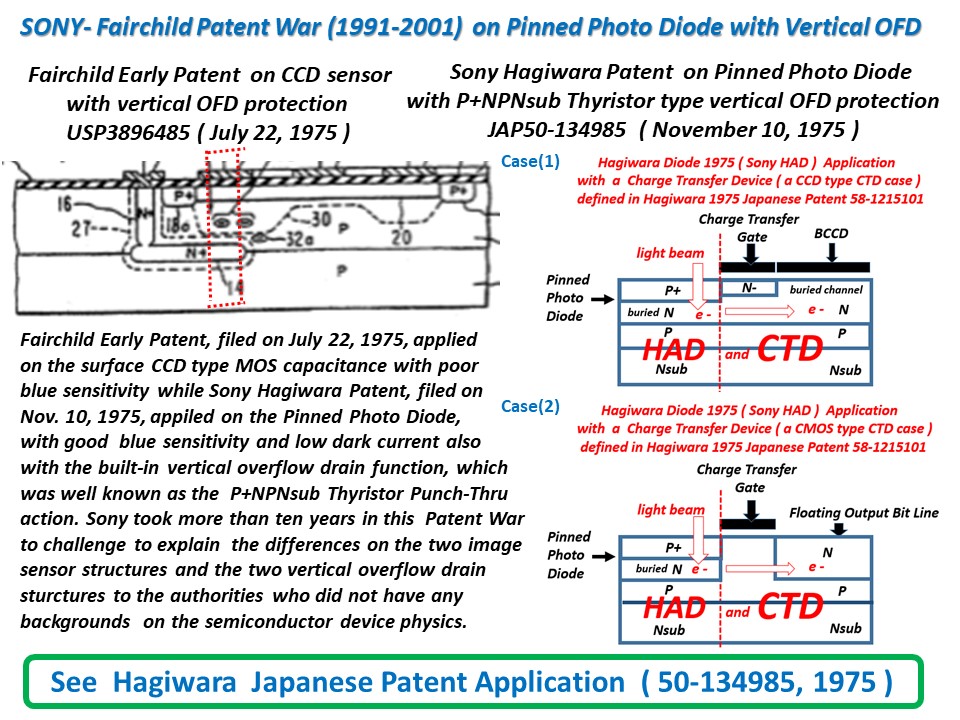

(2) However, the CCD invention gave the image lag free and very low

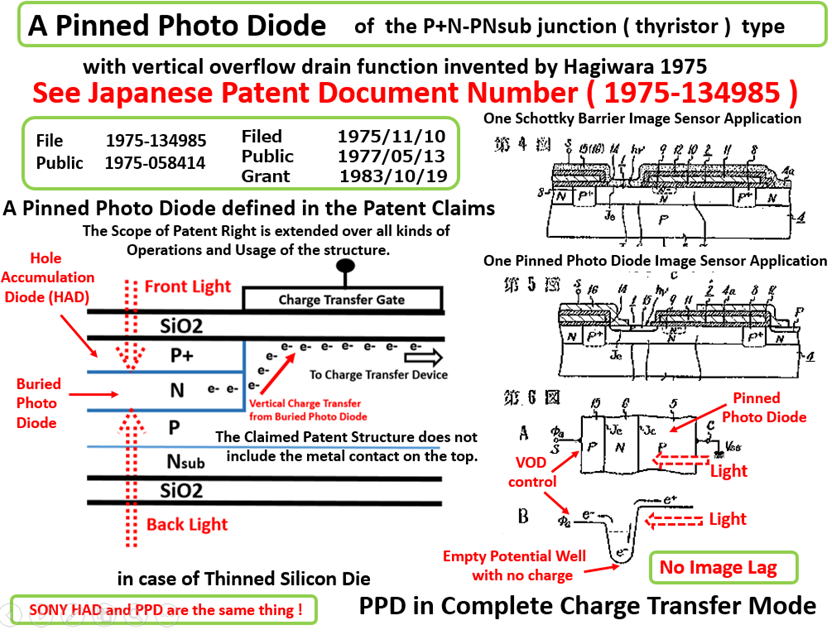

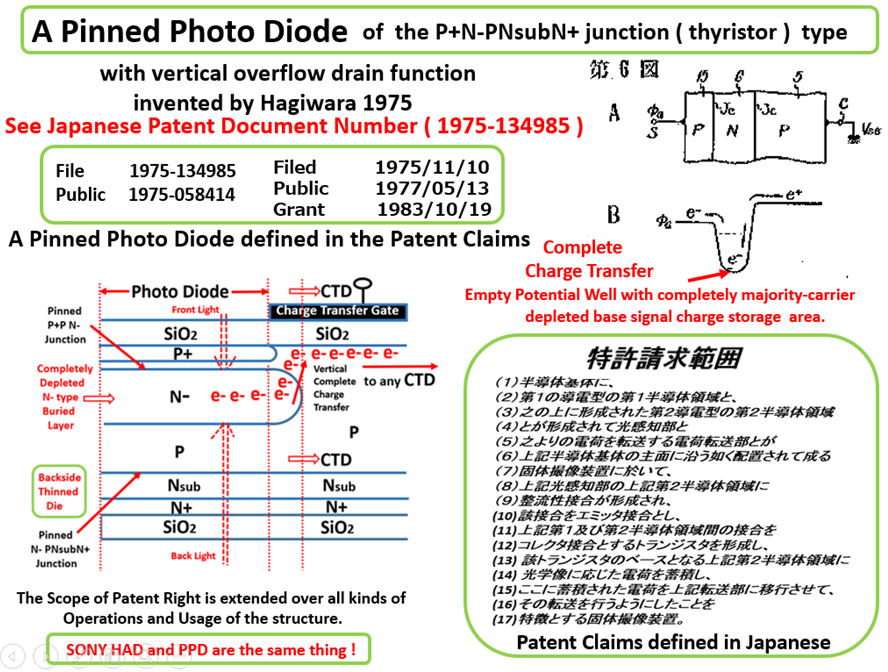

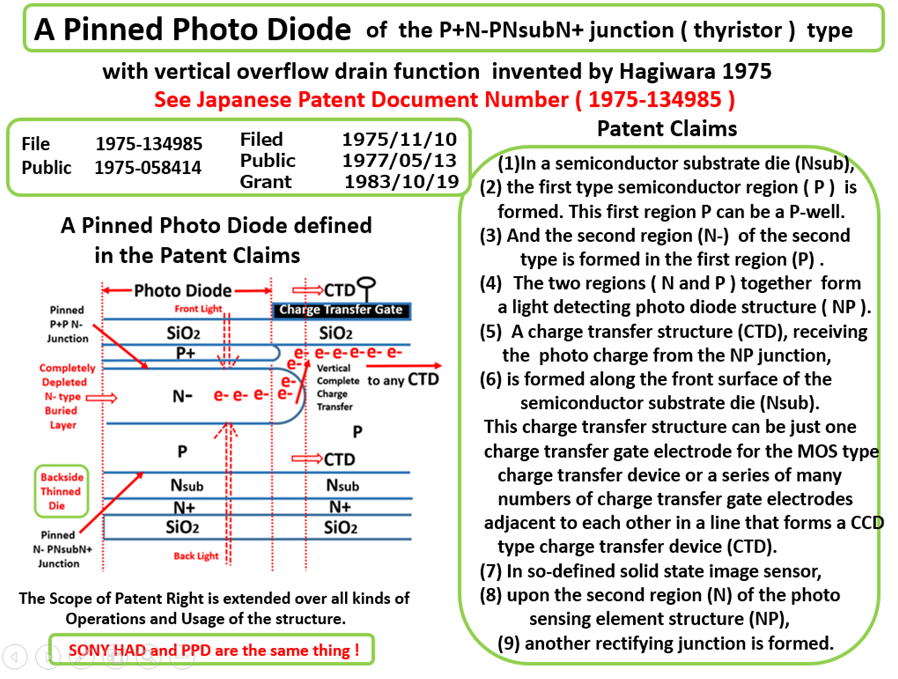

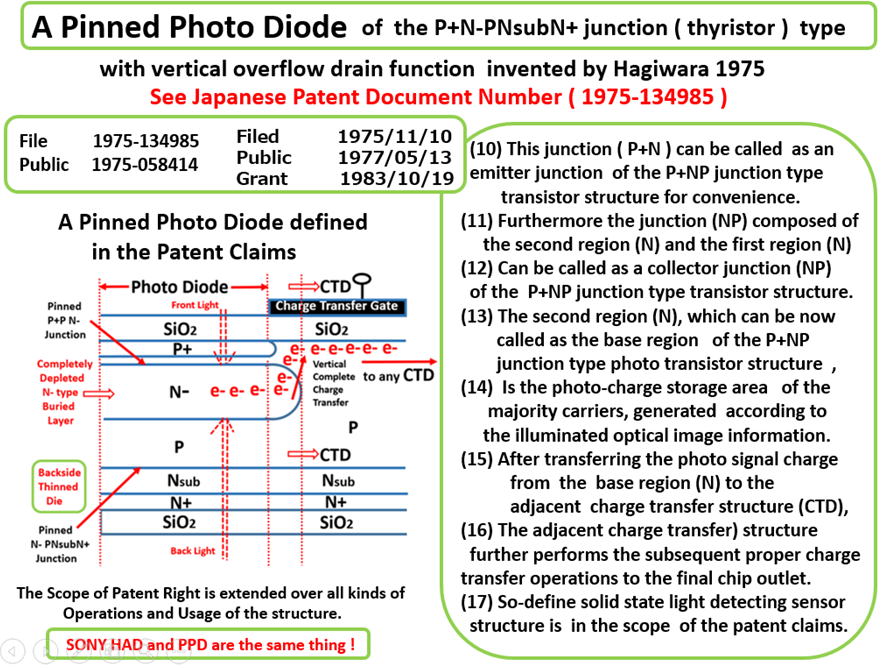

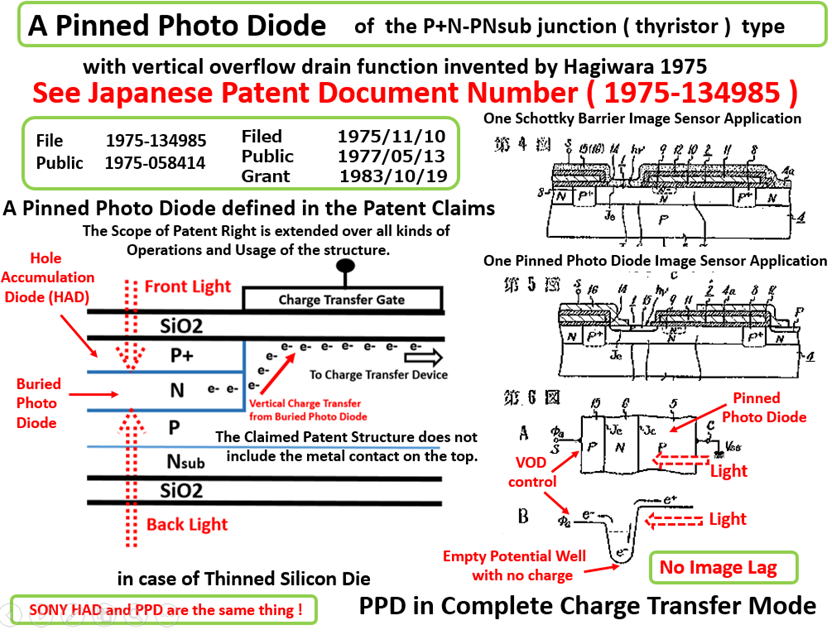

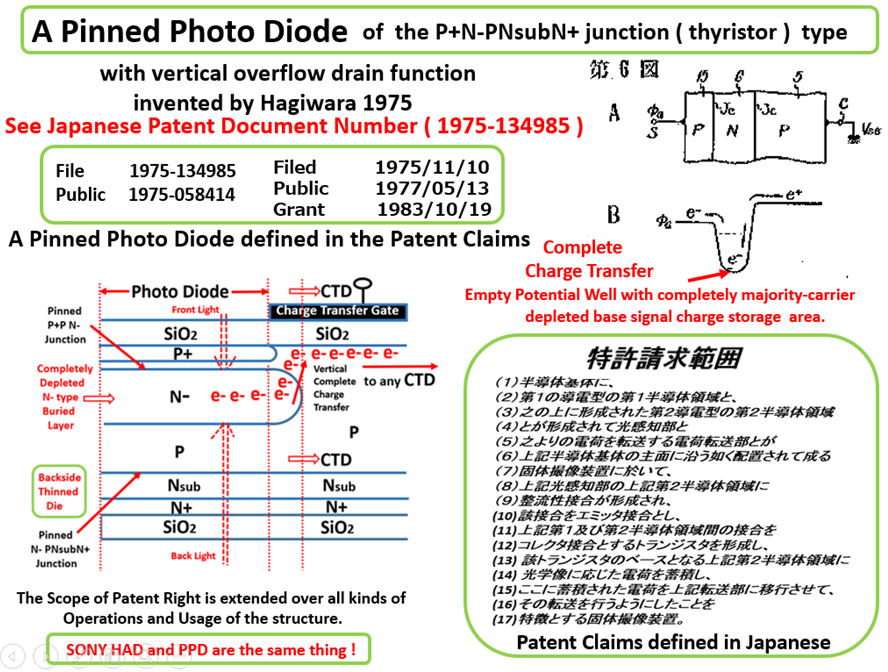

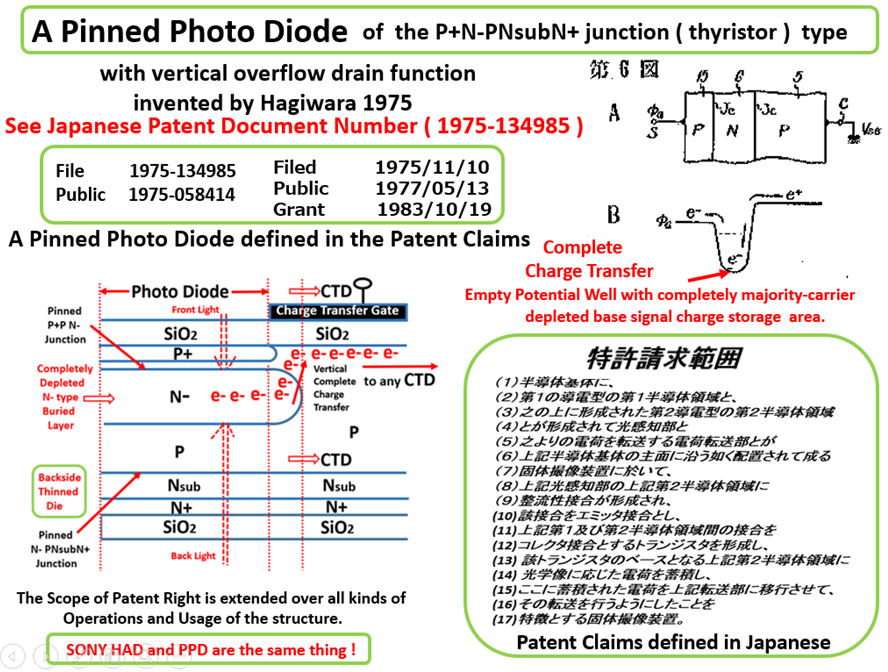

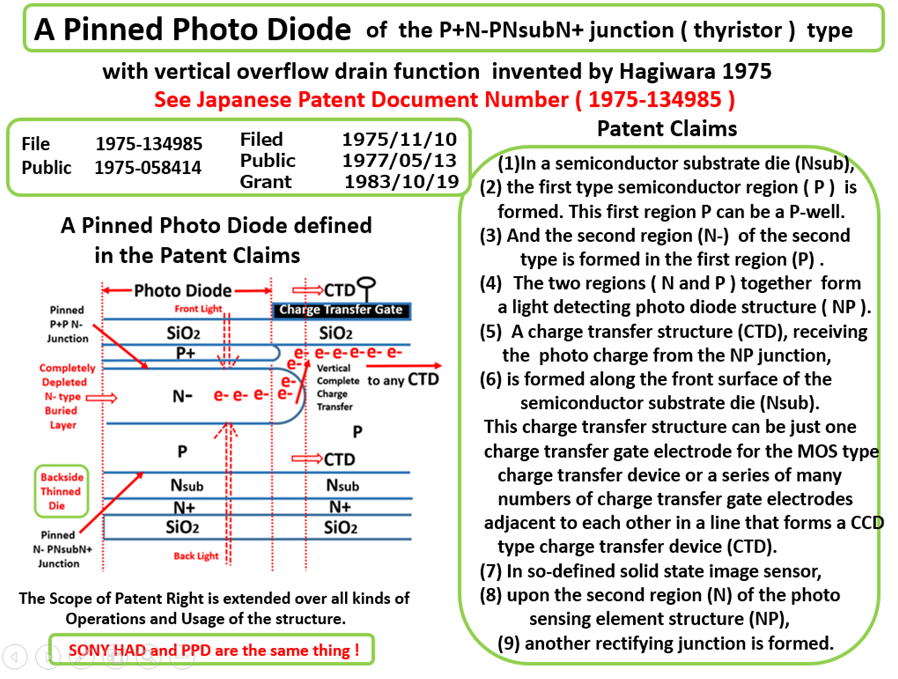

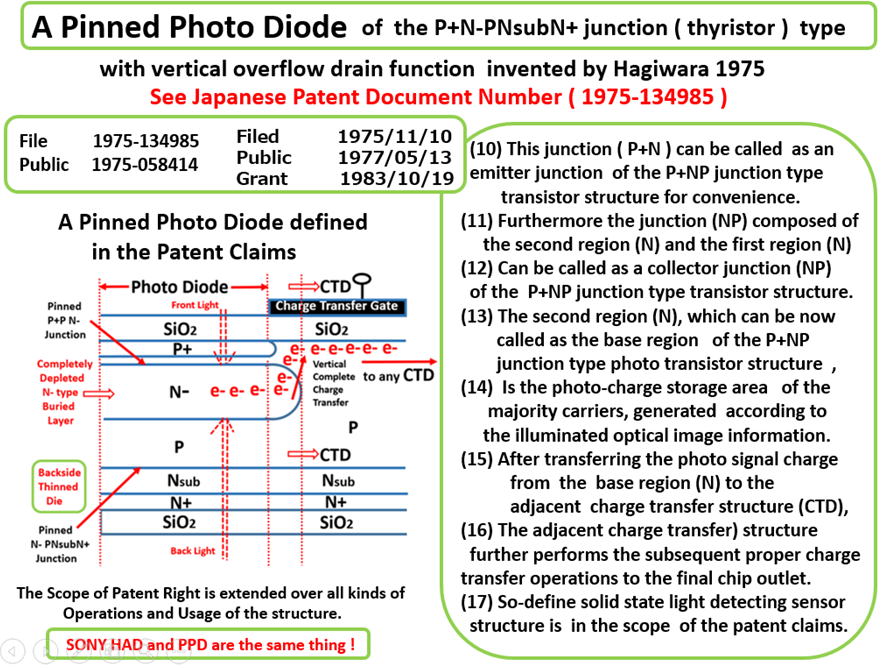

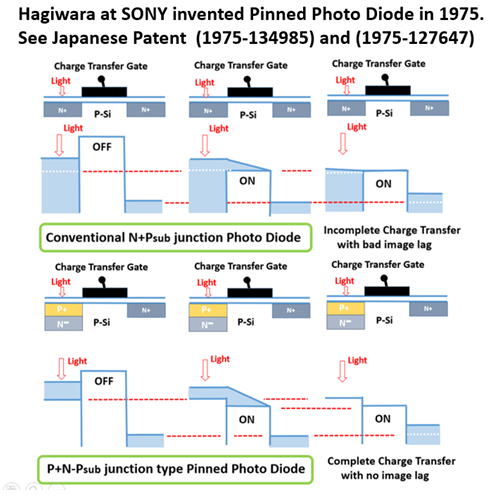

wire (CkT) noise pictures. The CCD became the super star with the

help of the P+NPNsub junctiion (thyrsitor) type photo diode, which

was invented by Hagiwara in 1975. See JAP ( 1975-134985 ) .

CCD consumed a lot of power with only the transfer efficency of 99.999

%,

which was however possible to be applied for the classical NTSC picture

resolution. CCD had the serious trap noise and surface dark current problems.

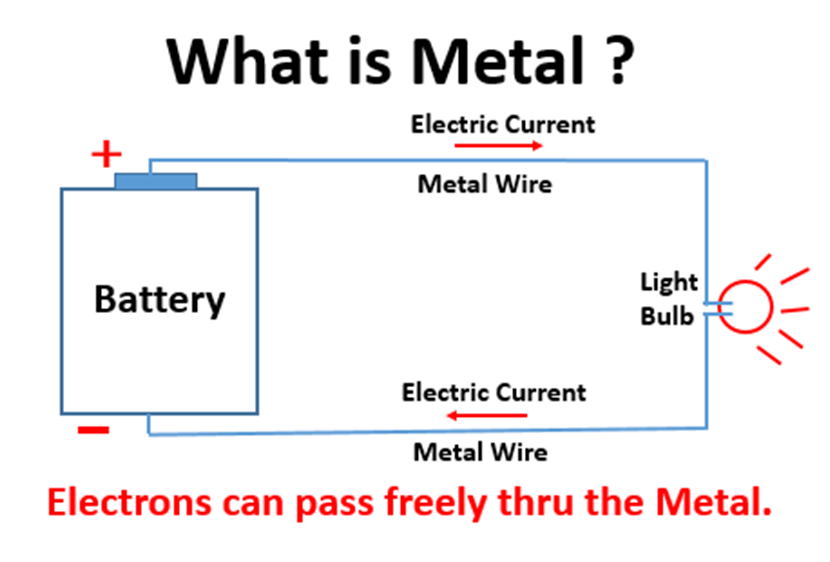

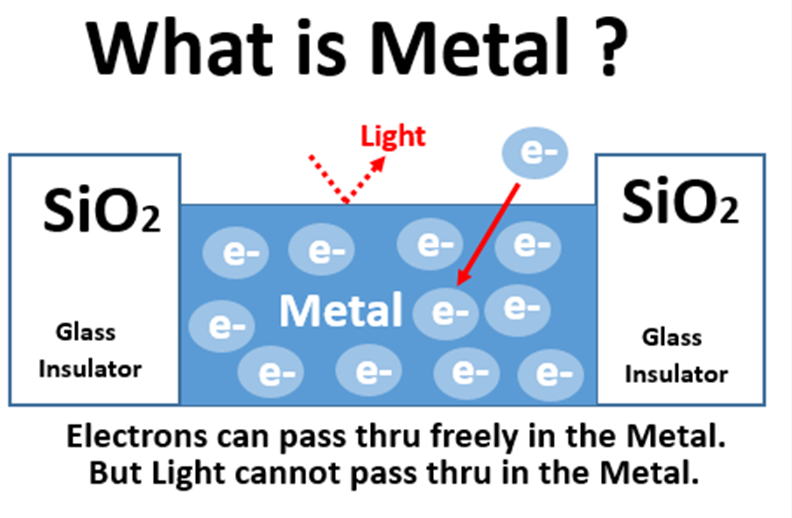

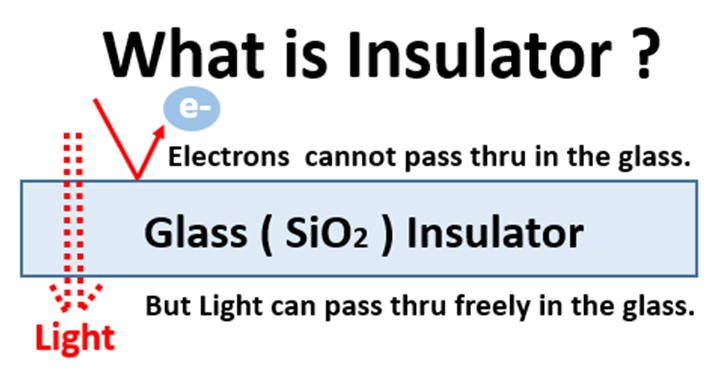

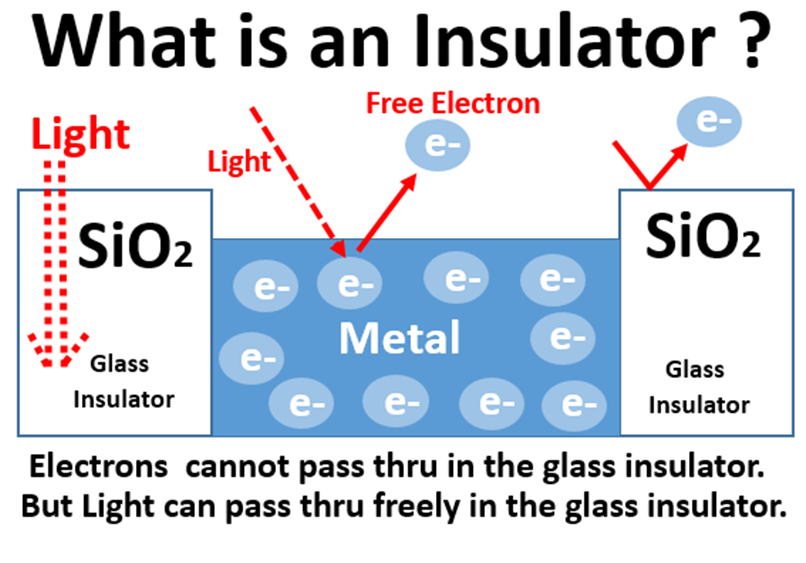

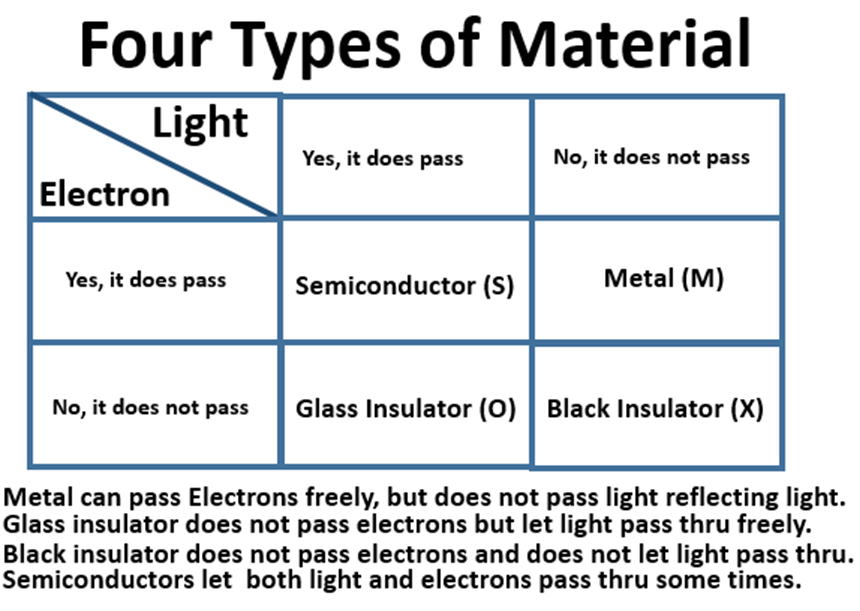

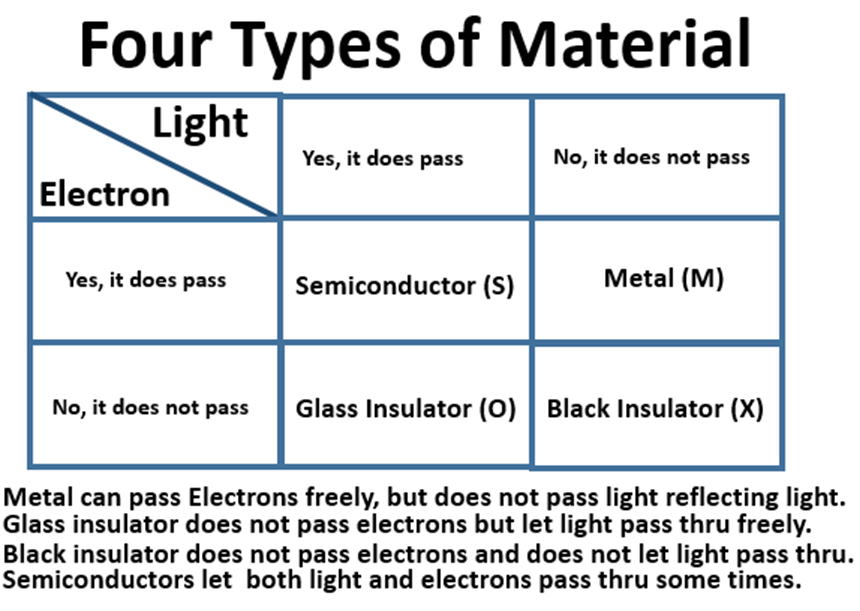

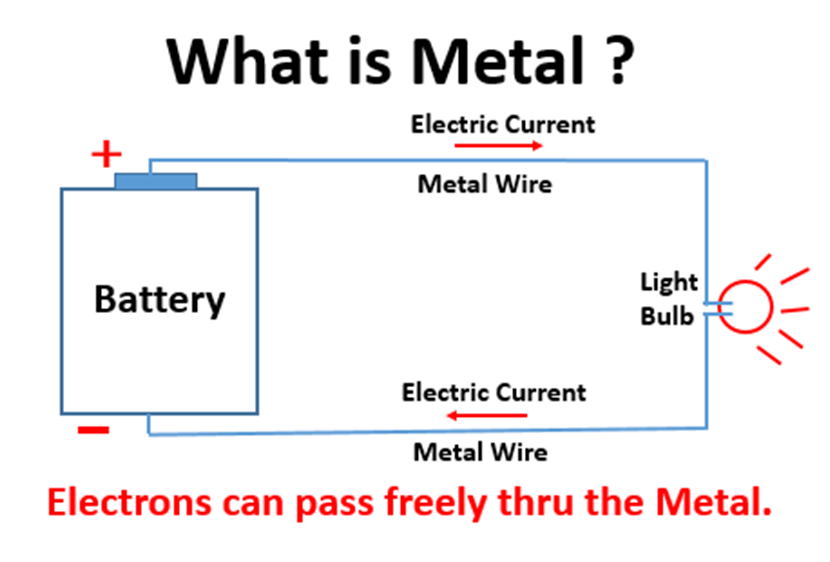

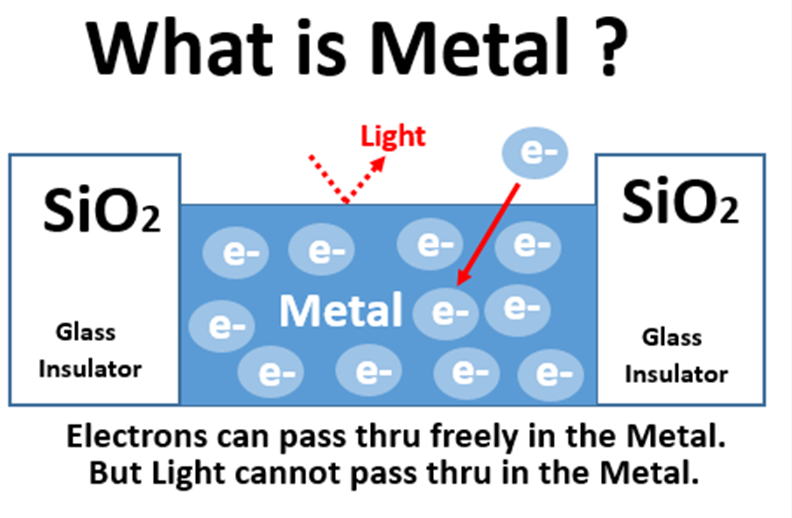

Moreover, CCD had inherently MOS metal-type electrodes that do not pass

light and CCD was not as light-sensitive as the N+P photo diode. So, the

CCD

type light detecting picture cell was replaced by the the P+NPNsub junctiion

(thyrsitor) type photo diode, Hagiwara 1975 invention. See JAP ( 1975-134985

) .

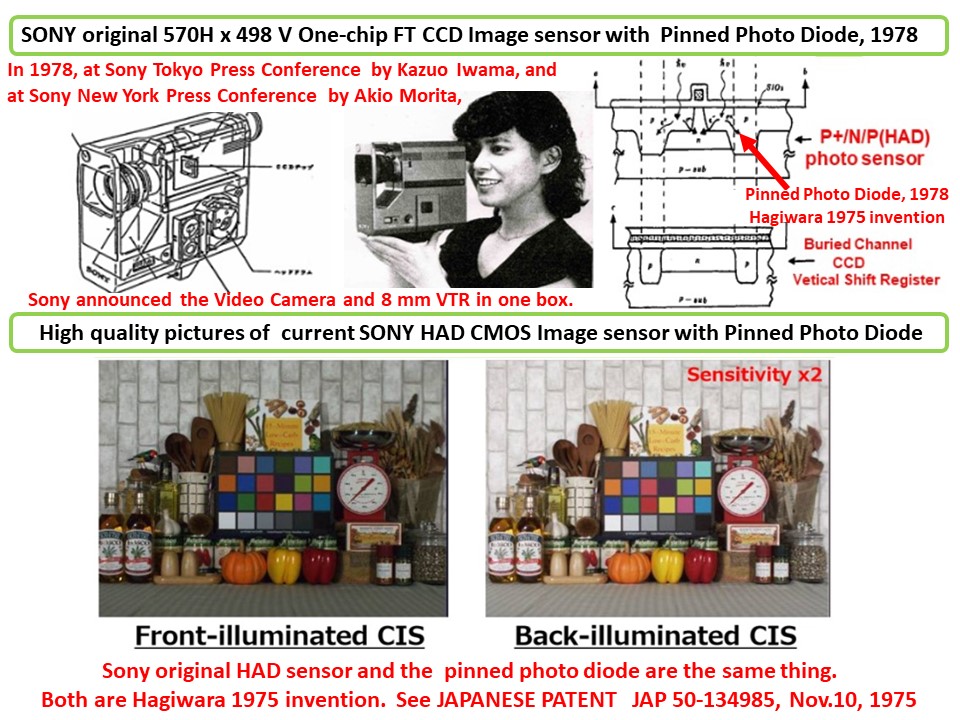

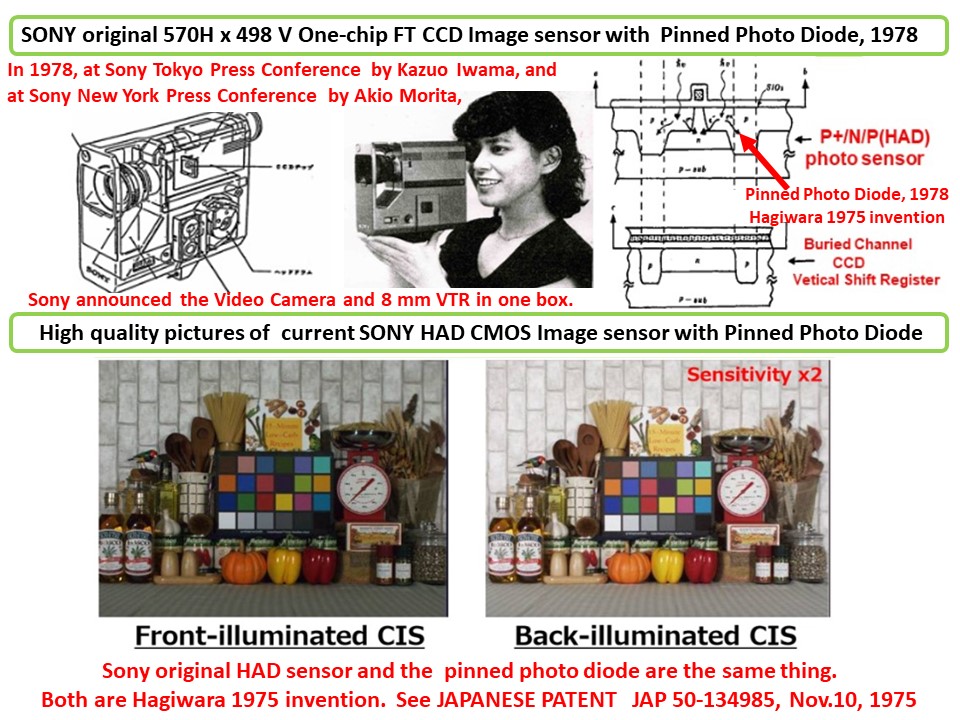

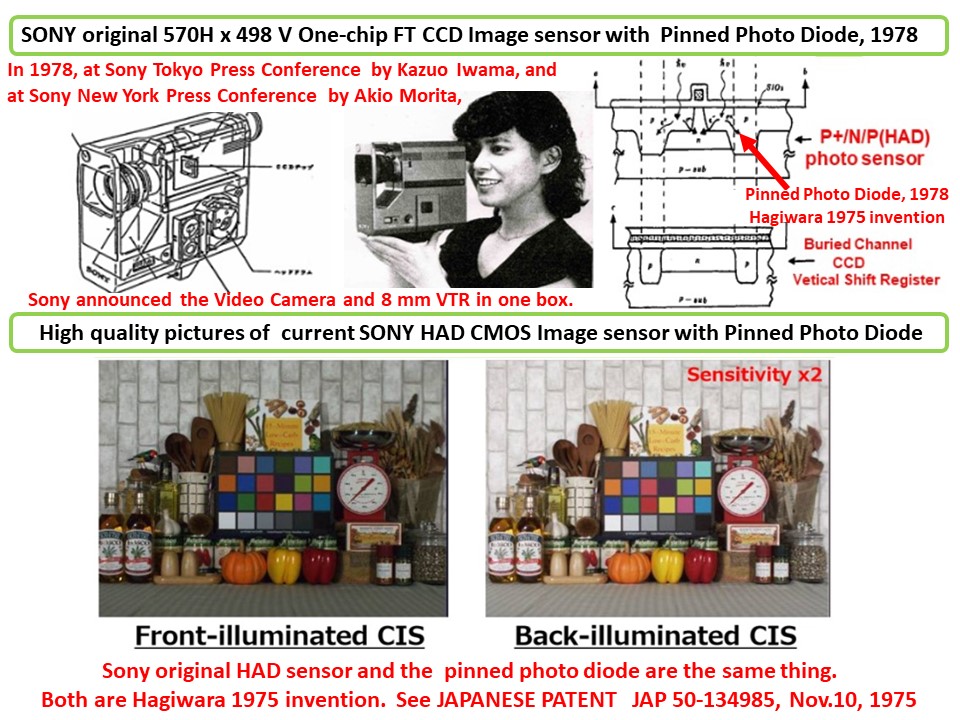

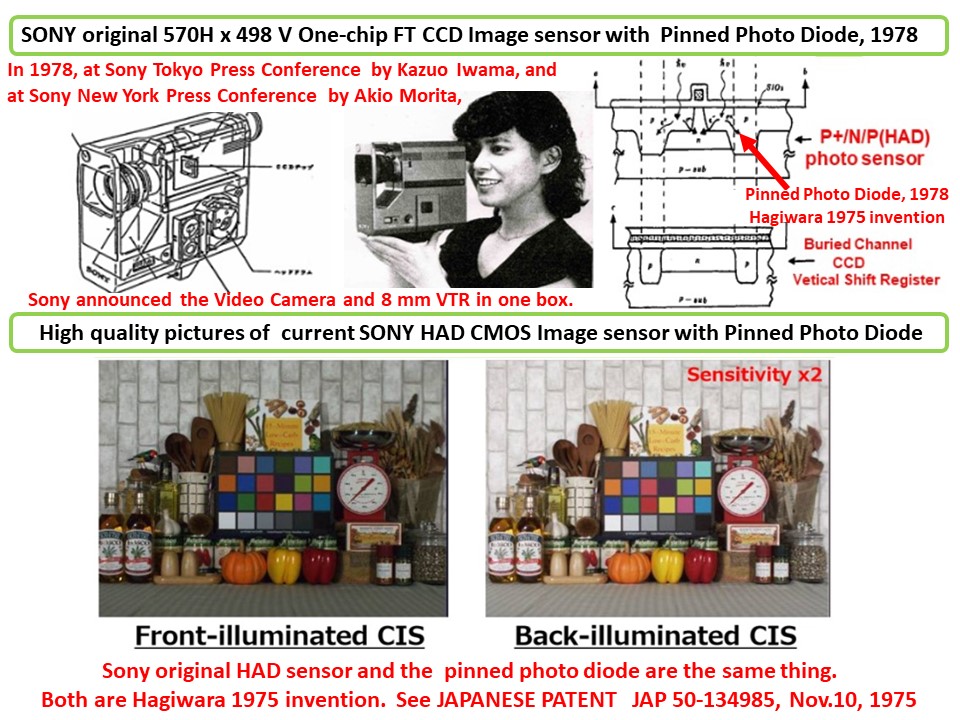

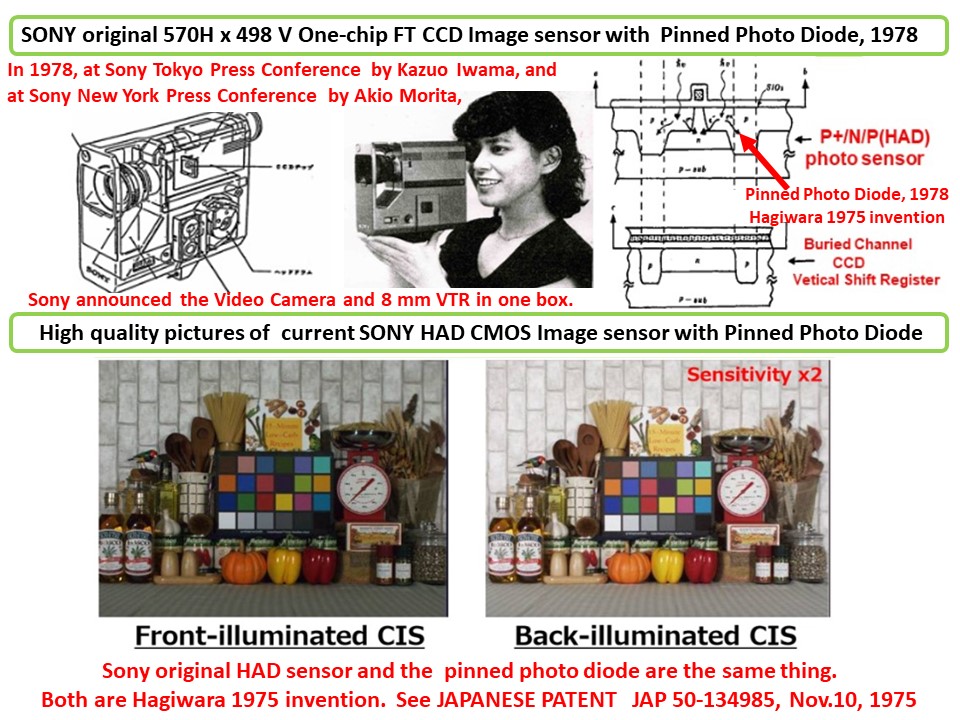

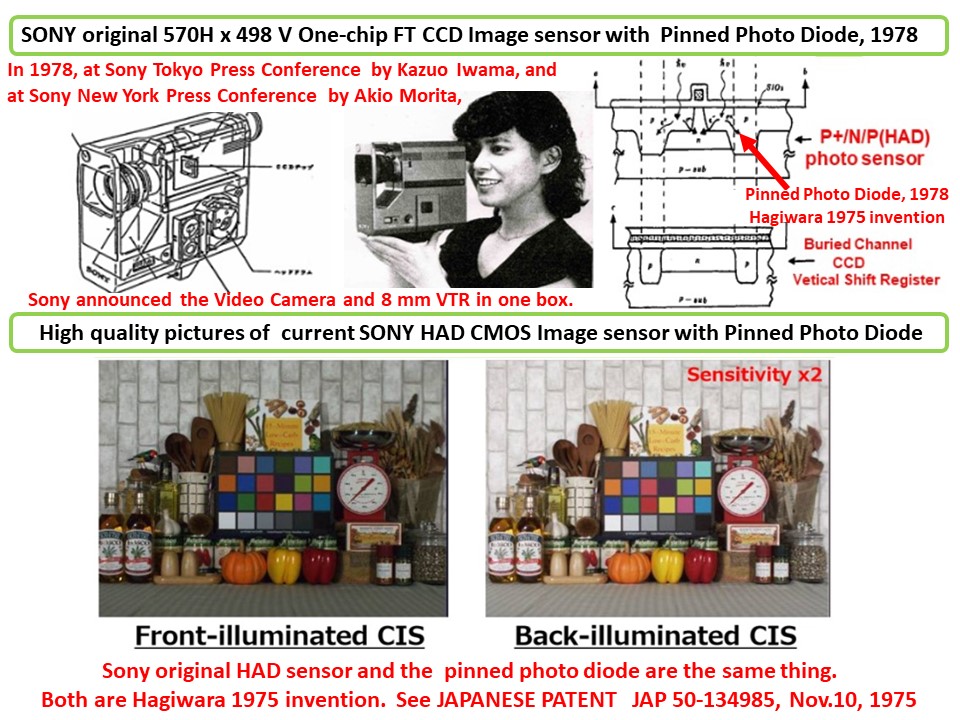

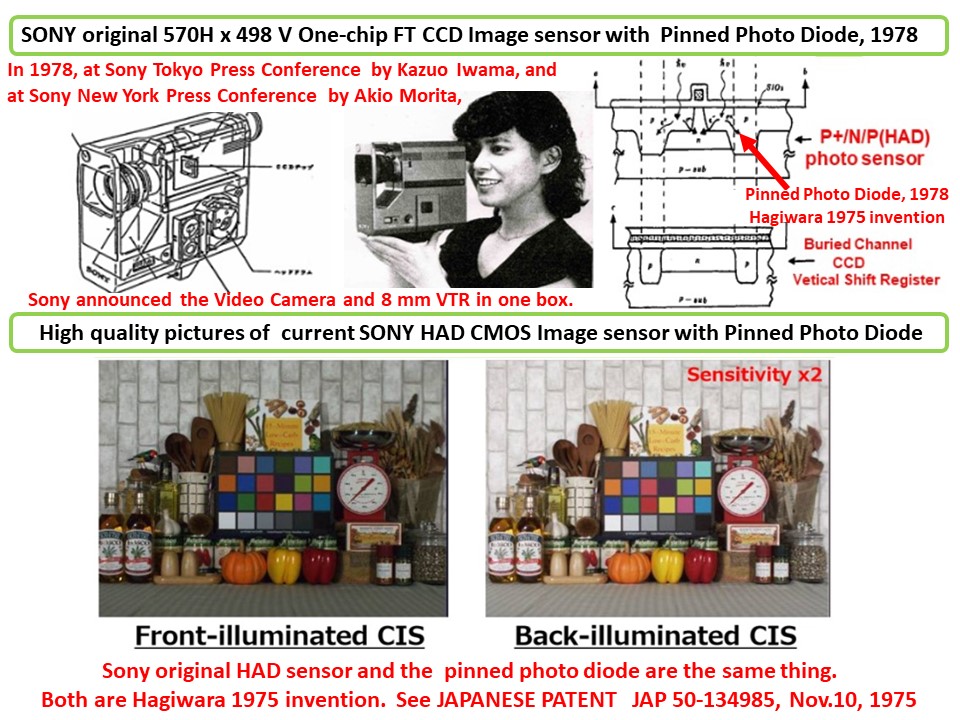

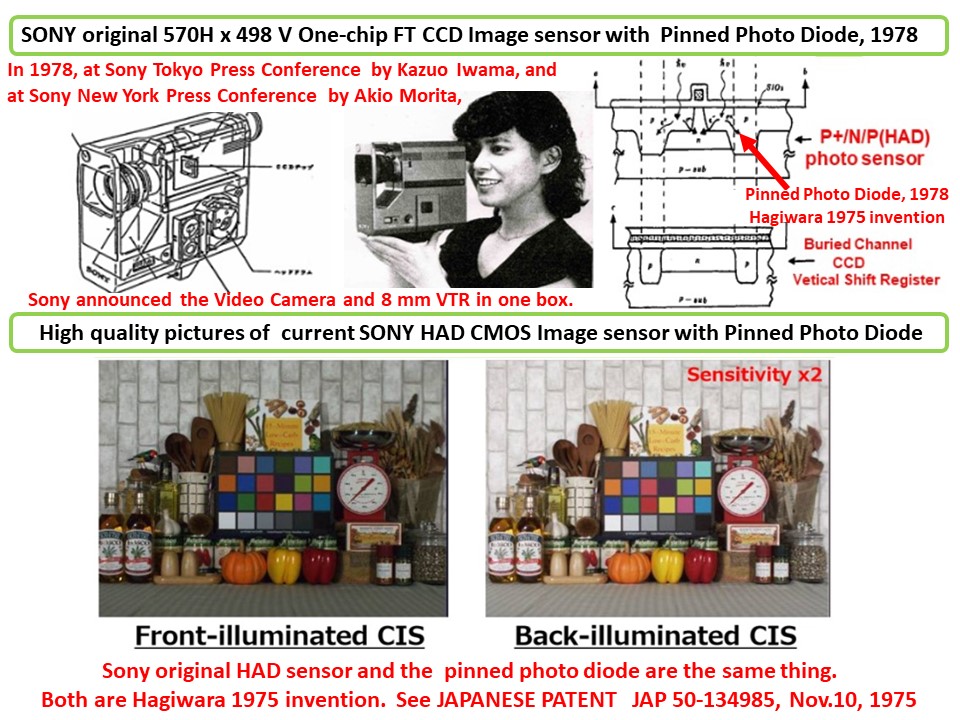

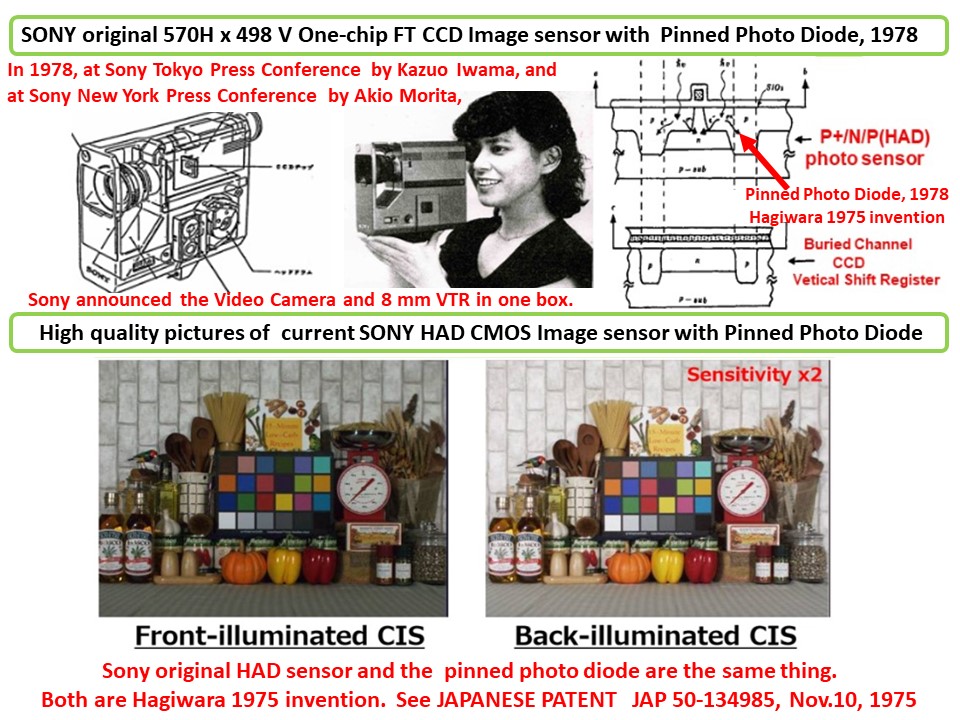

In 1978, SONY annouced in New York and Tokyo Press Conferences the world

first CCD image sensor with no image lag, very highly light sensitive,

low trap

noise, low surface dark current features of the PNP junction type photo

diode

sensor pixel structure,Hagiwara 1975 invention. See JAP ( 1975-134985 ) .

At that time, the world already gave up the CCD image development efforts.

SONY was the only company that never gave up. Sony showed the future of

CCD image sesnor applications. The truth is that Hagiwara in SONY was the

only engineer in the world who did not give up. And Hagiwara showed the

future of CCD image sesnor applications. by the P+NPNsub junctiion type

photo diode, Hagiwara 1975 invention. See JAP ( 1975-134985 ) .

So Hagiwara save the CCD by his 1975 invention, which is now called by

another name, the Pinned Photo Diode.

The truth is that CCD was NOT highly light sensitive, NOT low dark current

and NOT trap noise free image sensor structure. The true super star was

not CCD. The true super star was hiden behind the curtain. The true super

star was Hagiwara 1975 invention, which is now called by another name,

the Pinned Photo Diode. SONY called it as the SONY original HAD sensor.

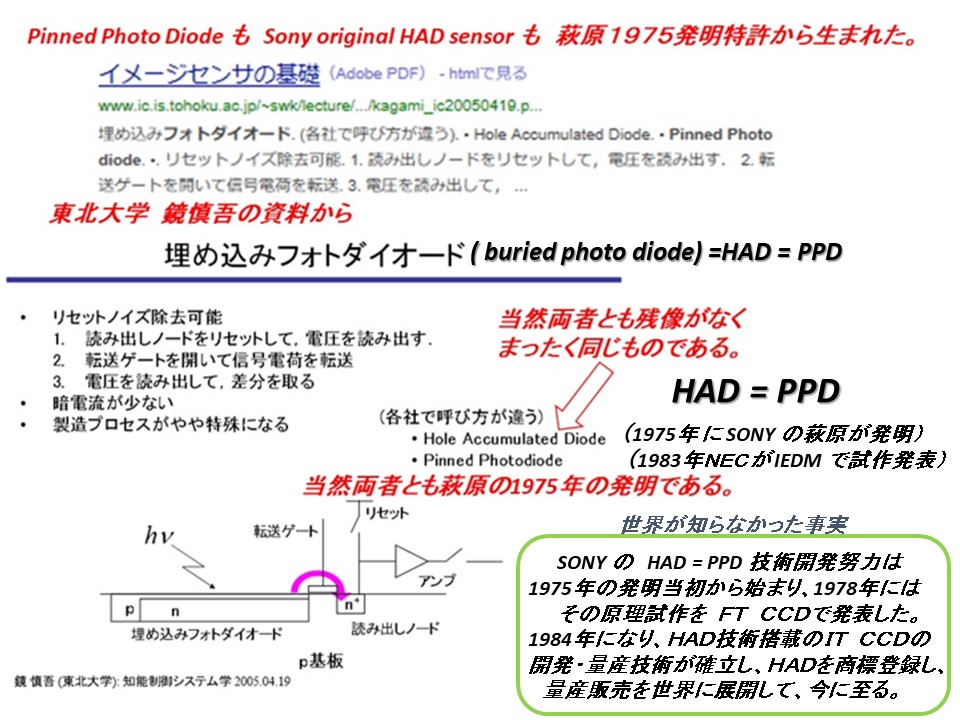

The truth is that the Pinned Photo Diode and the SONY original HAD sensor

are the same thing, that Hagiwara of SONY invented in 1975.

In conclusion, Hagiwara of SONY invented and his team of many dilligent

and hard working SONY engineers developed the stitching technology

for large area image sensors. The world followed after SONY efforts.

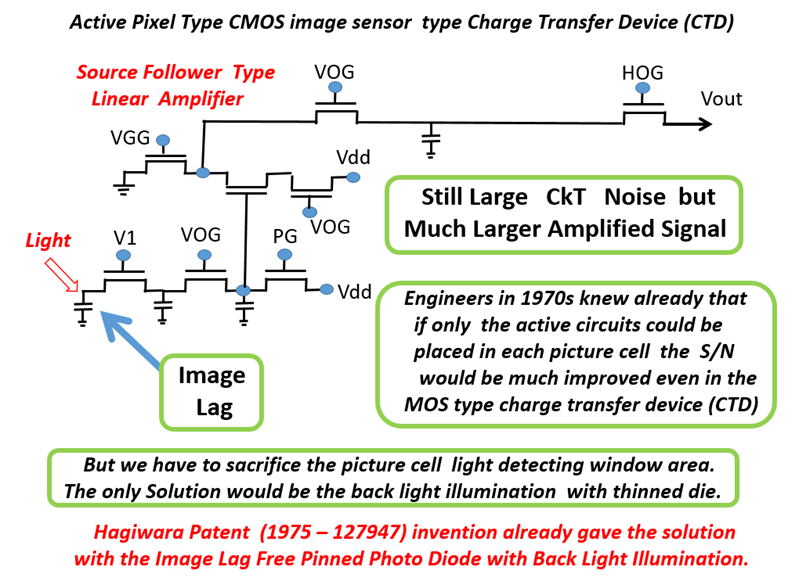

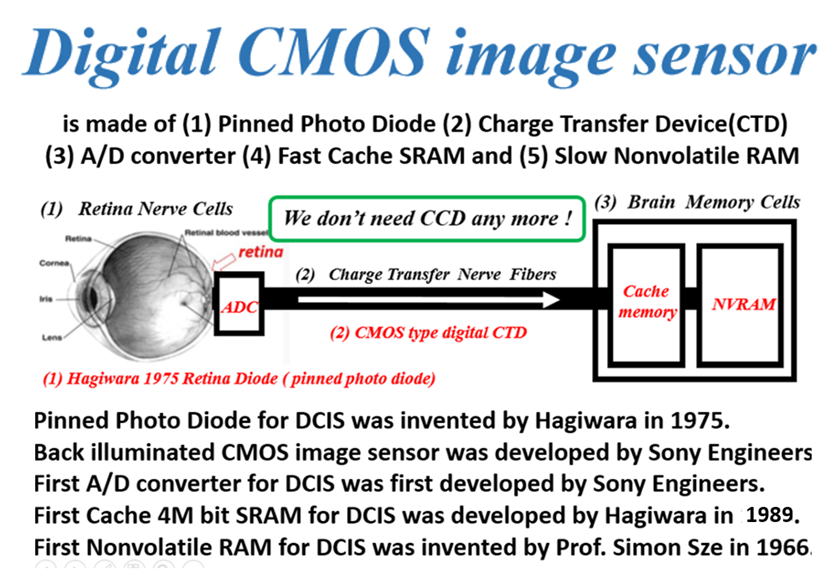

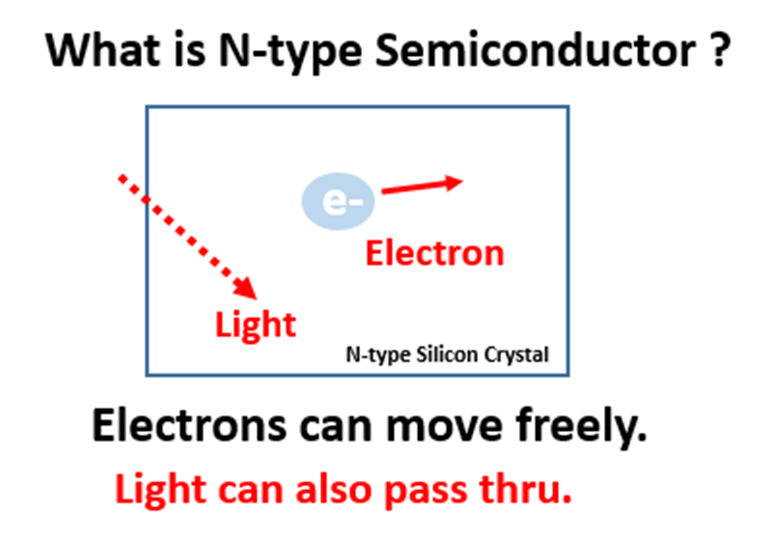

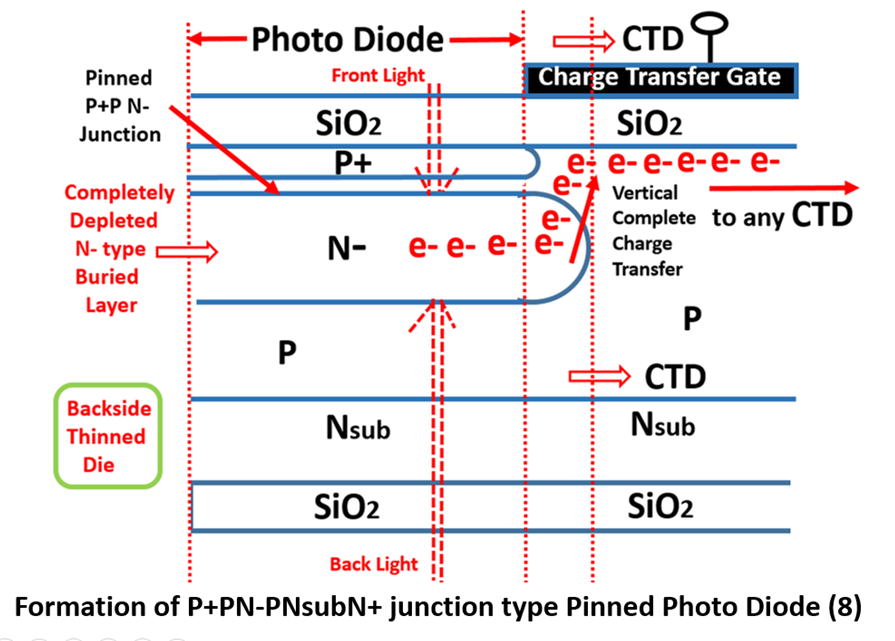

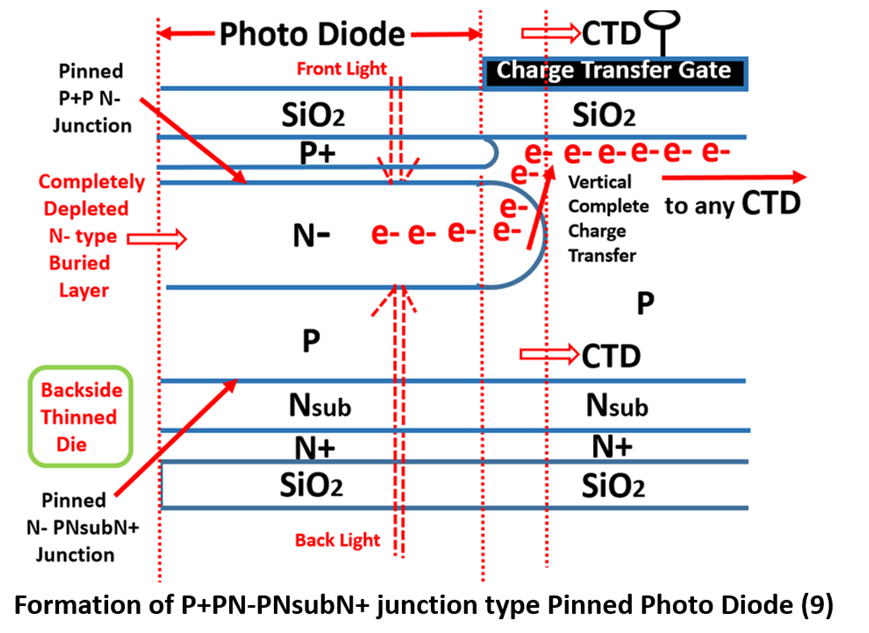

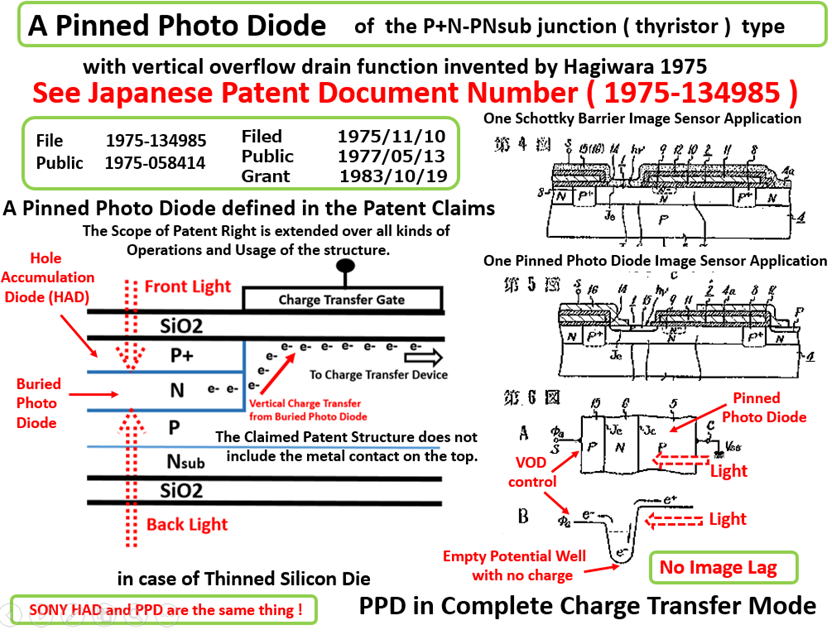

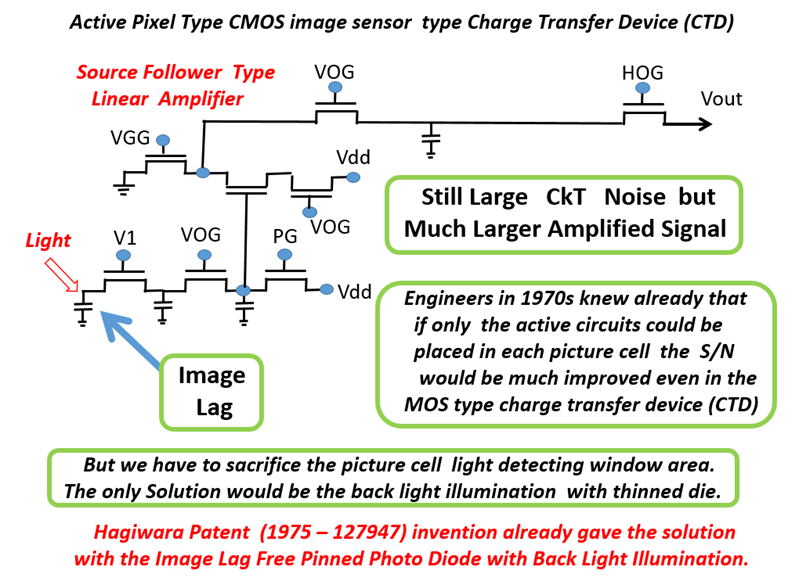

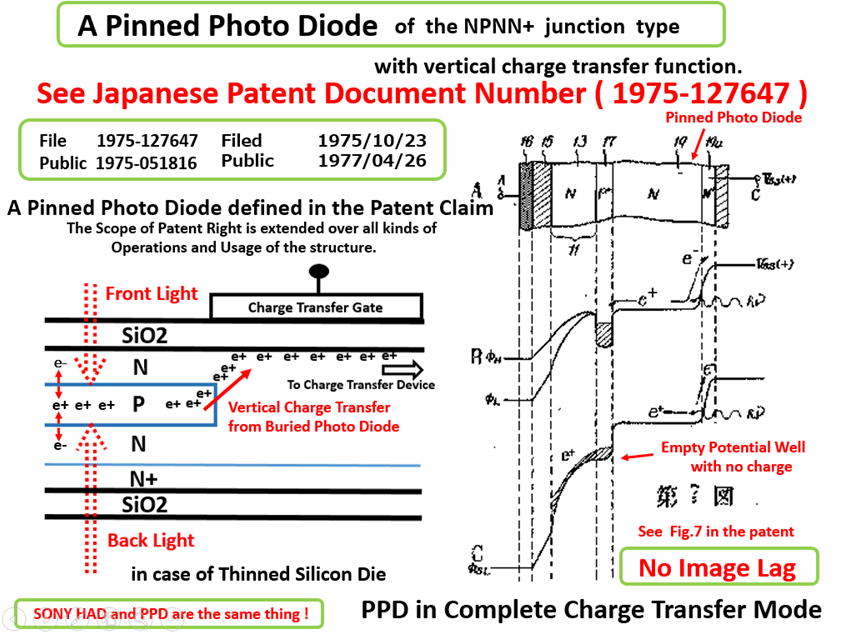

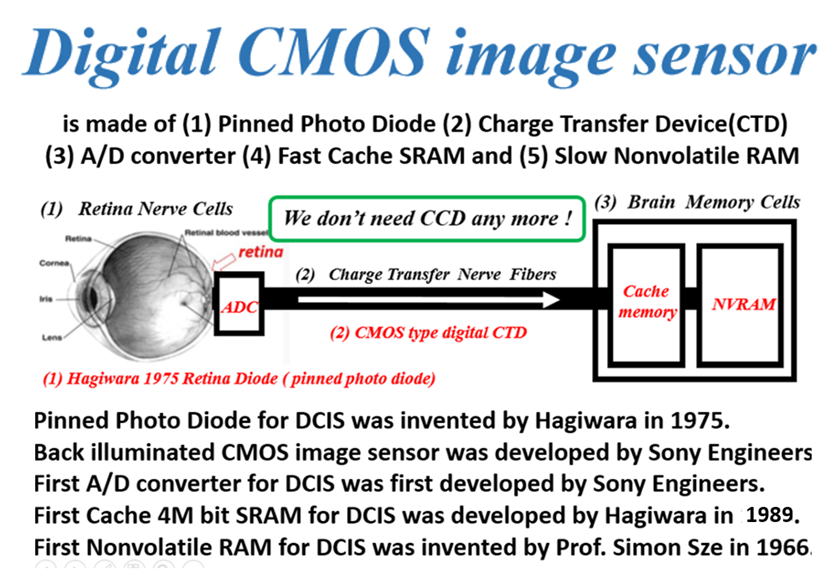

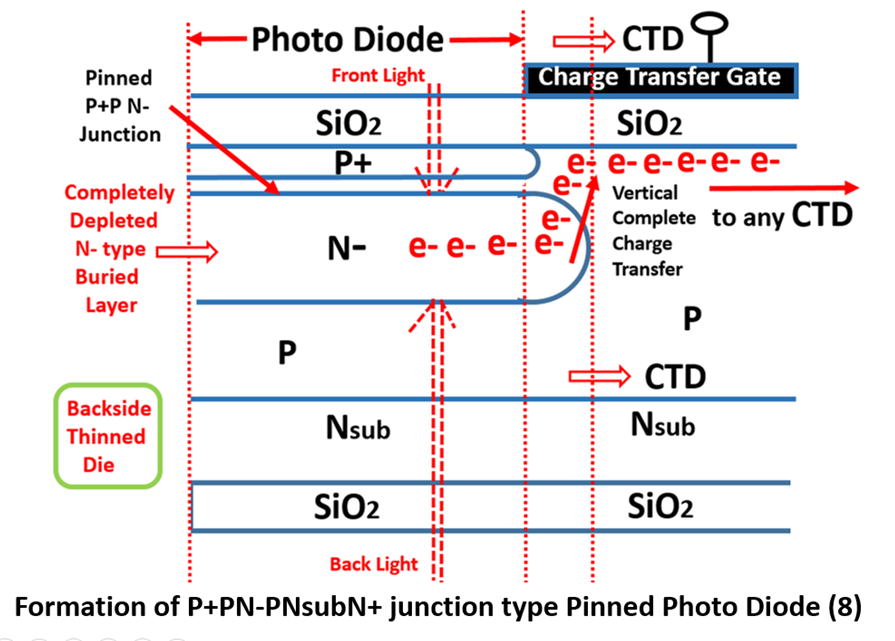

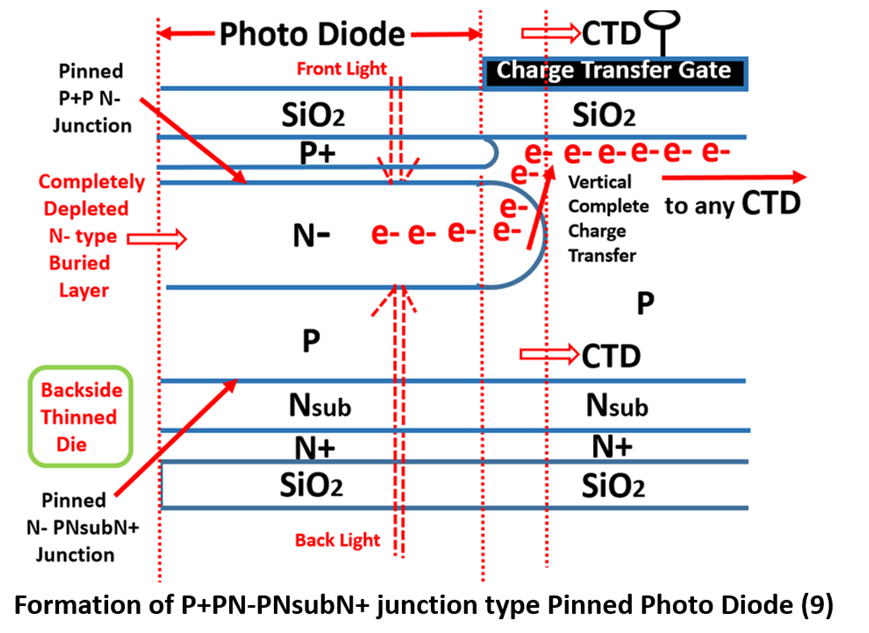

(3) Now, the complete CMOS transistor process scale down was achieved.

And the scale-downed three transistor active source follower type circuits,

originally invented by Peter Noble, can be now easily incorporated in each

picture cell of the CMOS image sesnors, with the help of the P+NP junctiion

type photo diode with the back light illumination scheme, which is again

the

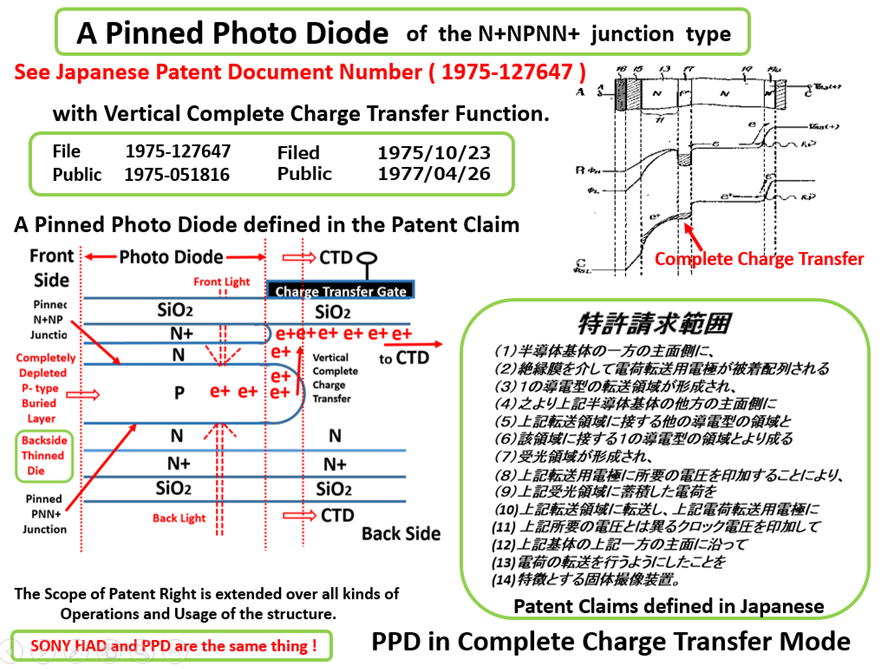

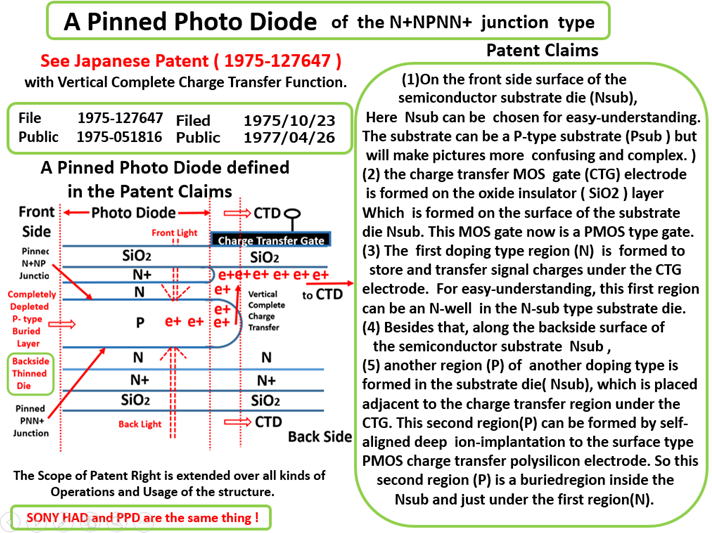

invention by Hagiwara in 1975. See JAP( 1975-127647 ).

SONY diligent and hard working engineers developed the modern dgital

CMOS image sensor with the back light illumination scheme for the

first time in the world.

Now again SONY owns the world record in low-noise in the voltage domain

for the modern digital CMOS image sensors (CISs).

Hagiwara 1975 invention ( JAP 1975-134985 ) helped CCD image sensor in

the past.

Hagiwara 1975 invention ( JAP 1975-127647 ) is helping CMOS image sensor

now.

Hagiwara and his original team of SONY diligent and hard working engineers developed

the stitching technology of both CCD and CMOS large area image sensors.

CCD was considered as the Super Star in the image sensor world in the past,

and the inventors were awarded with the NOBEL prize. But now CCD has

completely dissappeared from the modern digital image sensor world.

So who were the real super stars in the world ?

And now who are the real super stars in the world ?

*******************************************************************

*******************************************************************

*******************************************************************

See three invited talks related to SONY HAD sensor now called also as Pinned

Photo Diode.

(1) International Conference CCD79 in Edinburgh, Scotland UK

(2) International Conference ESSCIRC2001 in Vilach, Austria.

(3) International Conference ESSCIRC2008 in Edinburgh, Scotland UK

*******************************************************************

Hagiwara was invited in these international conferences because of his

contributions

to the image sensor community and related digital system LSI chip design

works.

*******************************************************************

**************************

Story of Pinned Photo Diode

Hagiwara at SONY is the true inventor of Pinned Photo Diode

**************************

See ElectronicsStackExchangeSite on What is Pinned Photo Diode ?

*******************************************************************

See three invited talks related to SONY HAD sensor now called also as Pinned

Photo Diode.

(1) International Conference CCD79 in Edinburgh, Scotland UK

(2) International Conference ESSCIRC2001 in Vilach, Austria.

(3) International Conference ESSCIRC2008 in Edinburgh, Scotland UK

*******************************************************************

Hagiwara was invited in these international conferences because of his

contributions

to the image sensor community and related digital system LSI chip design

works.

*******************************************************************

*******************************************************************

Questions by Prof. Albert Theuwissen are ,

- who invented and developed the stitching technology

for large area image sensors ?

- who owns the world record in low-noise

in the voltage domain for CMOS Image Sensor (CIS) ?

*******************************************************************

Hagiwara believes that

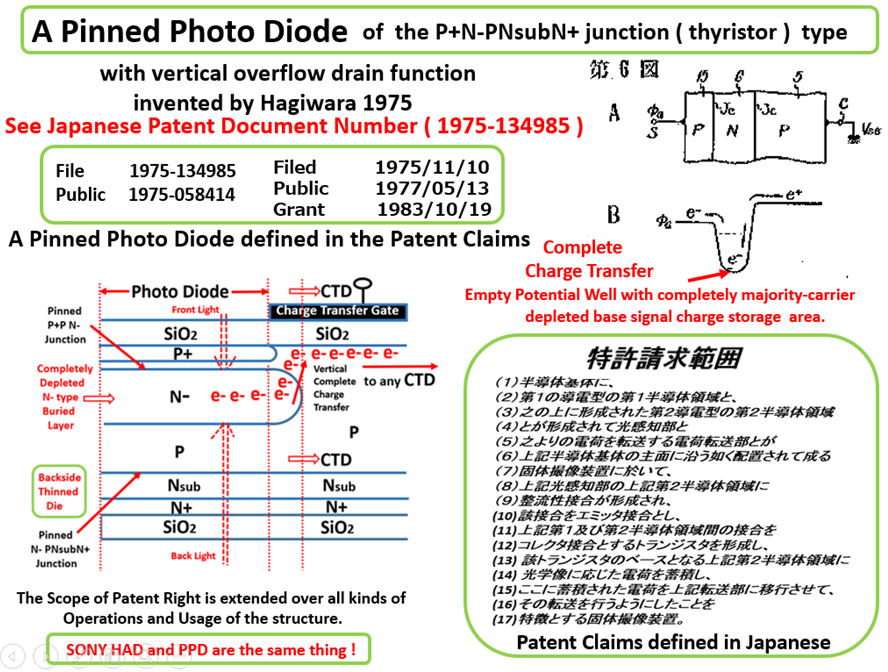

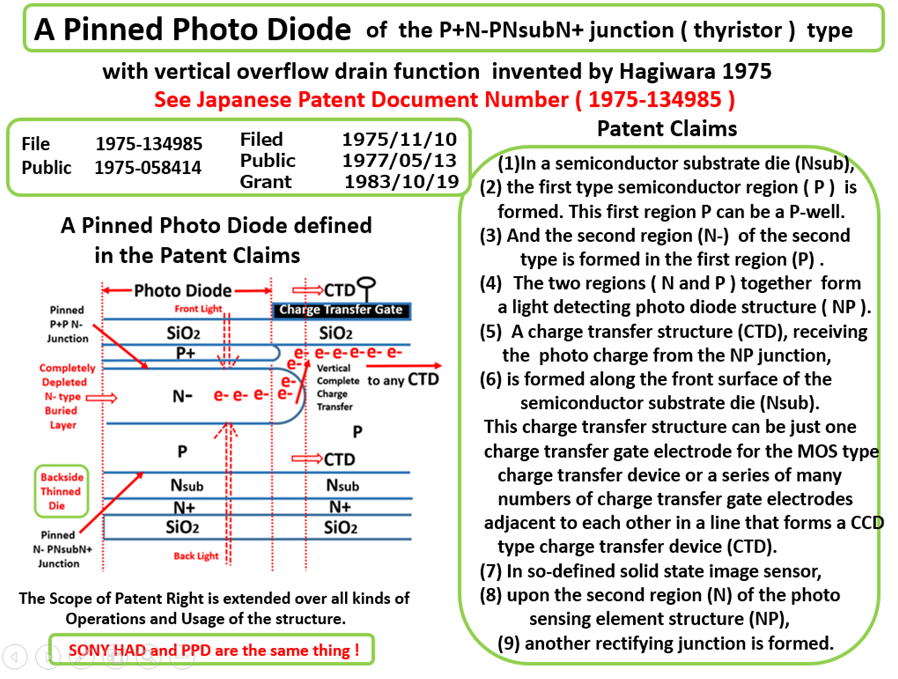

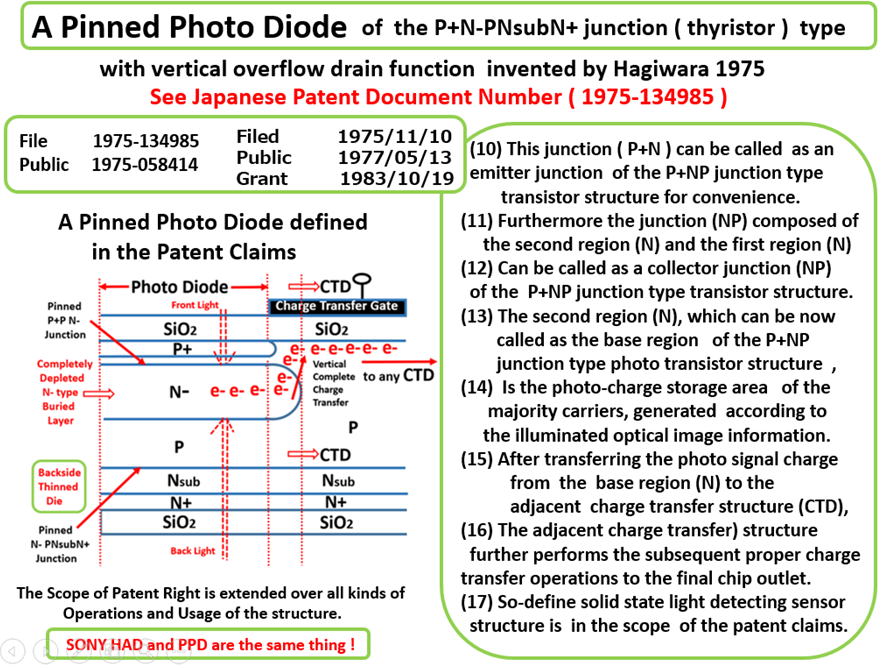

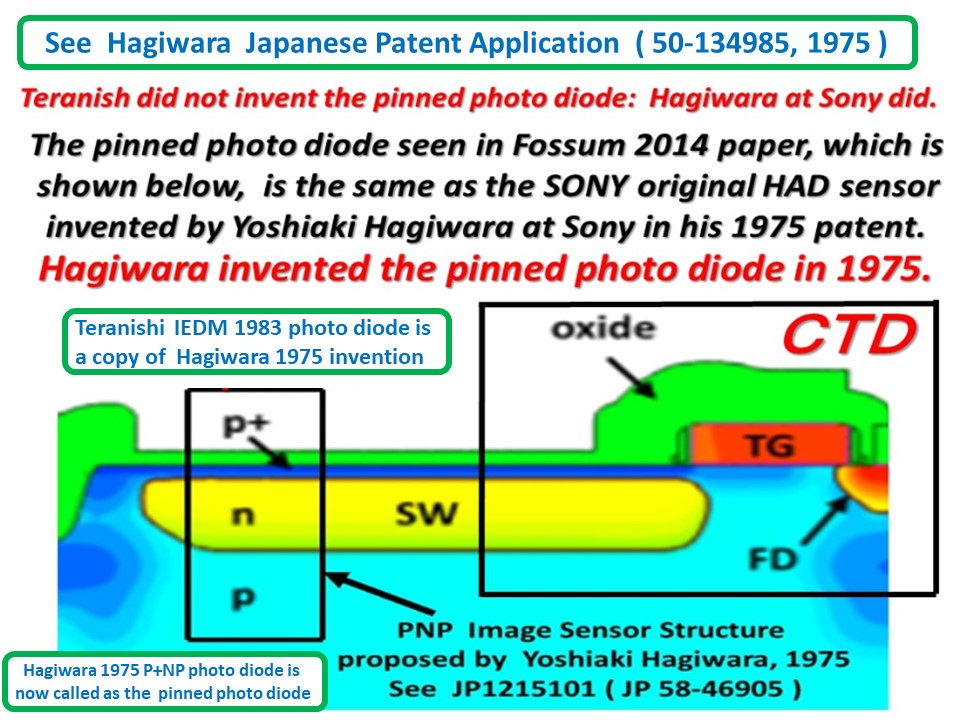

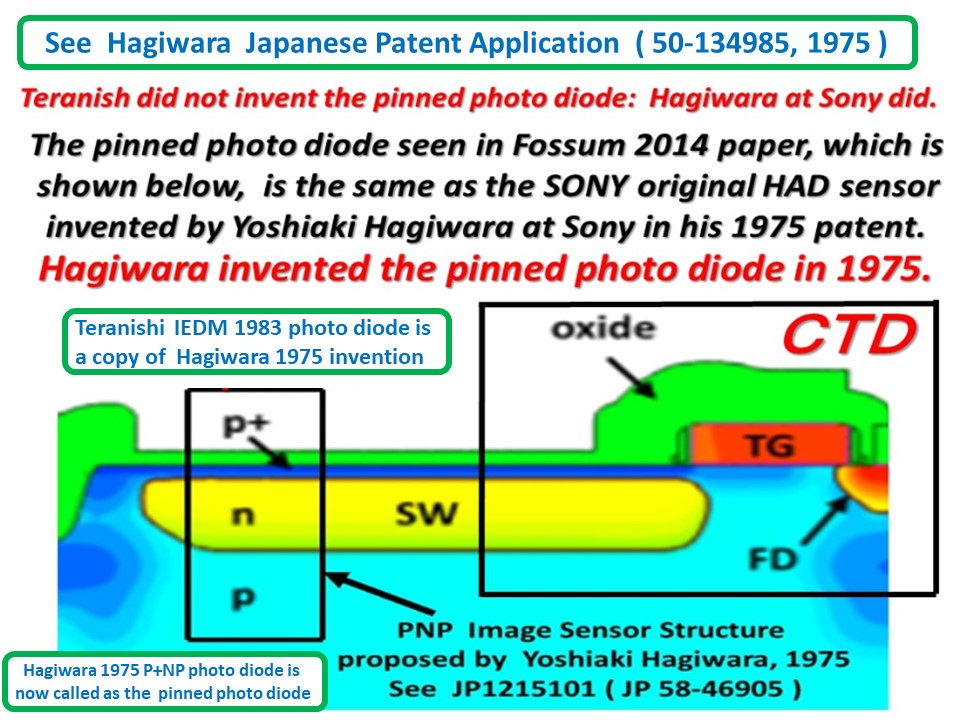

Hagiwara invented it , in the Japanese 1975 patent ( 1975-134985 ) as the P+NPNsub

junction ( Thyristor ) type Light Detecting Picture Cell Structure, and Sony diligent

engineers, including Haggiwara, developed, the stitching technology for large area image

sensors. SONY called it as the SONY original HAD sensor technology in SONY business.

Naturally, the technical world did not use the SONY businesss Brand Name HAD, and

called it by another name, the Pinned Photo Diode. But the Pinned Photo Diode and

SONY original HAD are the same thing, both invented by Hagiwara in 1975.

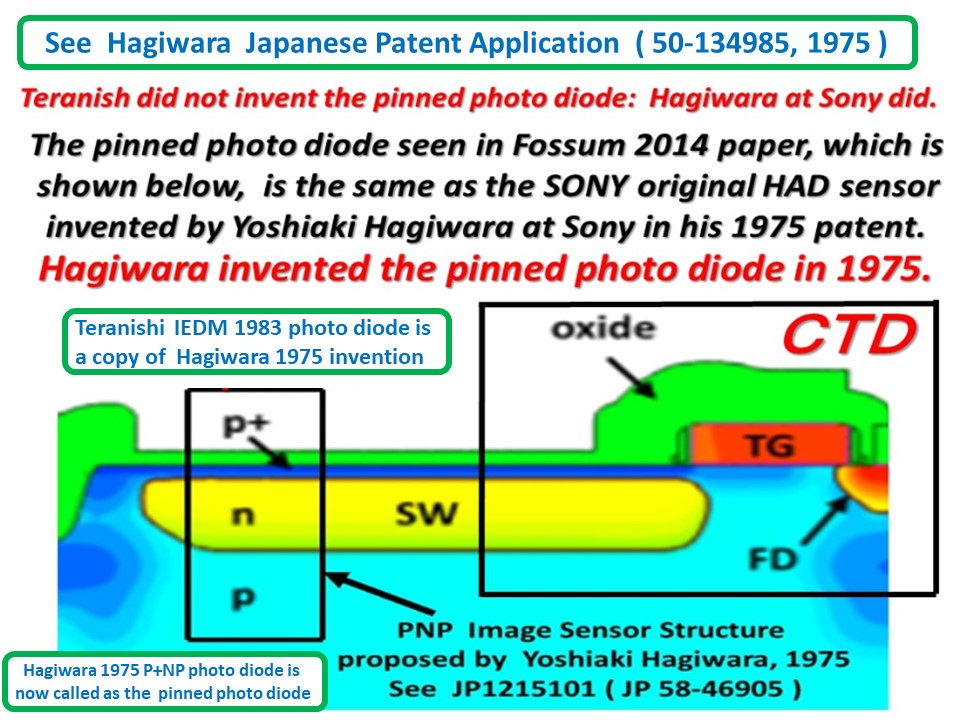

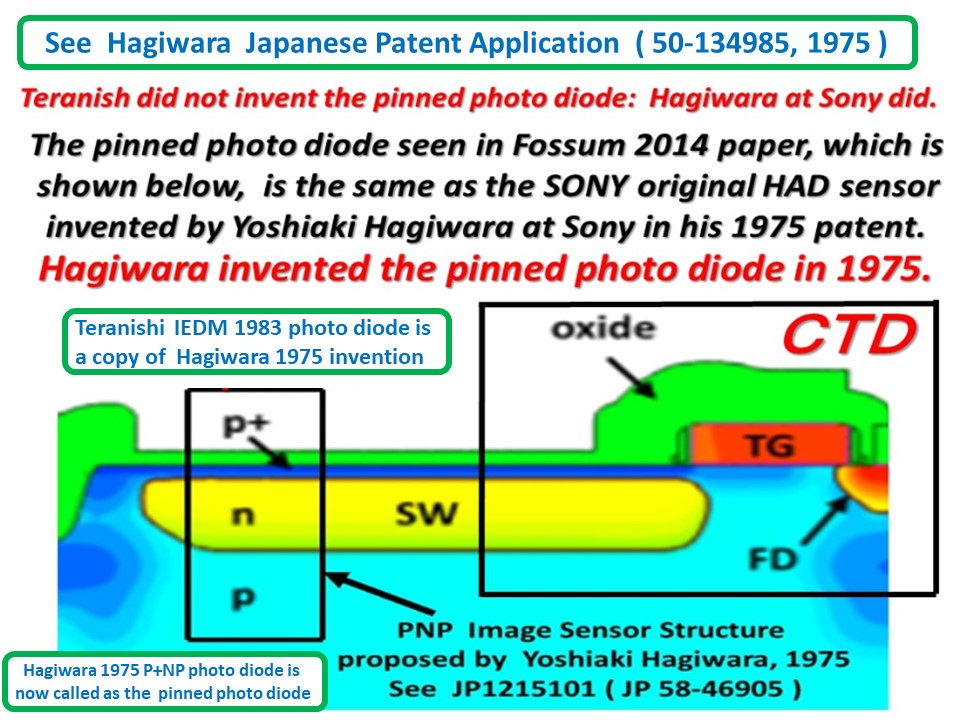

At least, Teranishi did not invent the Pinned Photo Diode.

Hagiwara is the inventor of the Pinned Photo Diode.

Sony diligent engineers developed and now Sony owns

the world record in low-noise in the voltage domain for CMOS Image Sensor

(CIS)

with the Pinned Photo Diode with the Back Light Illumination, that was

also invented

by Haiwara of SONY in 1975 the Japanses 1975 patent ( 1975-127647 ).

At least, Fossum is not the inventor of the active image sensor picture

element.

Peter Noble is the inventor of the active image sensor picture element.

http://www.pjwn.co.uk/

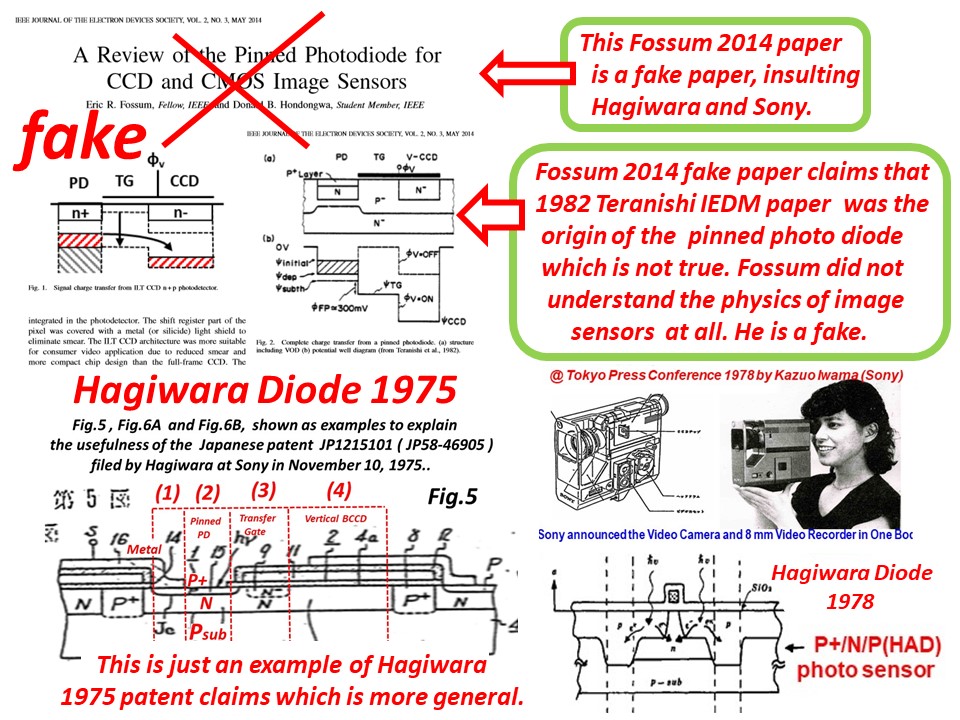

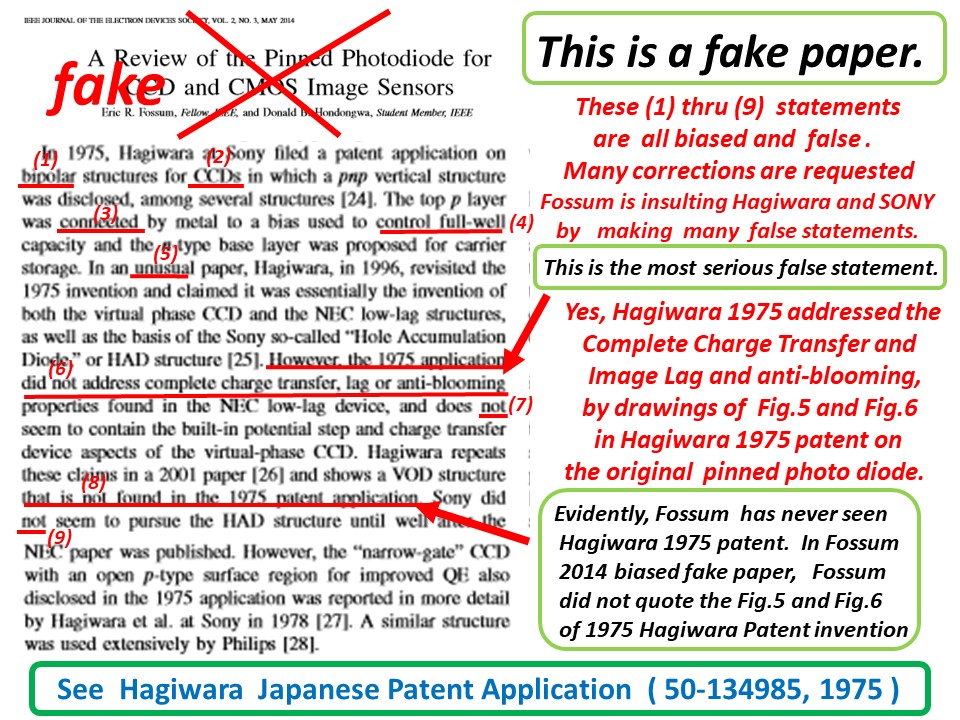

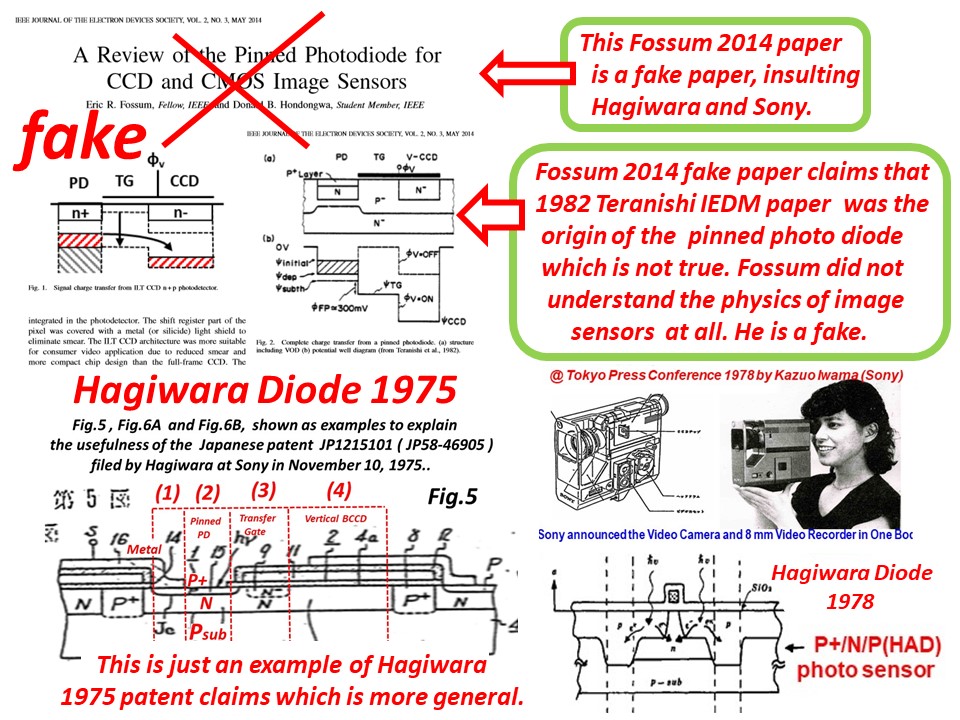

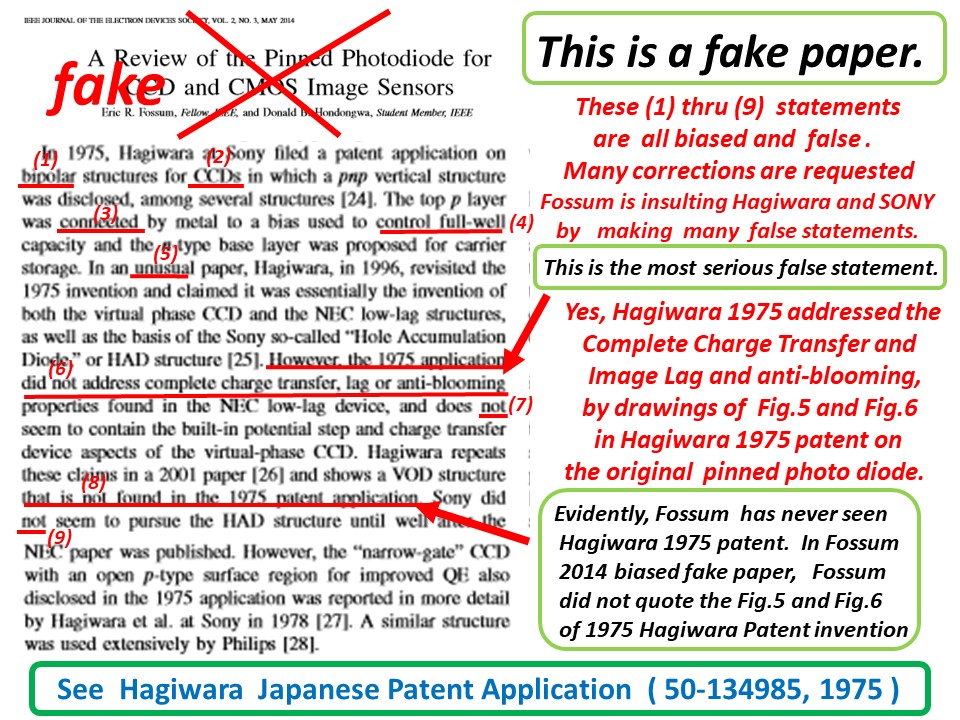

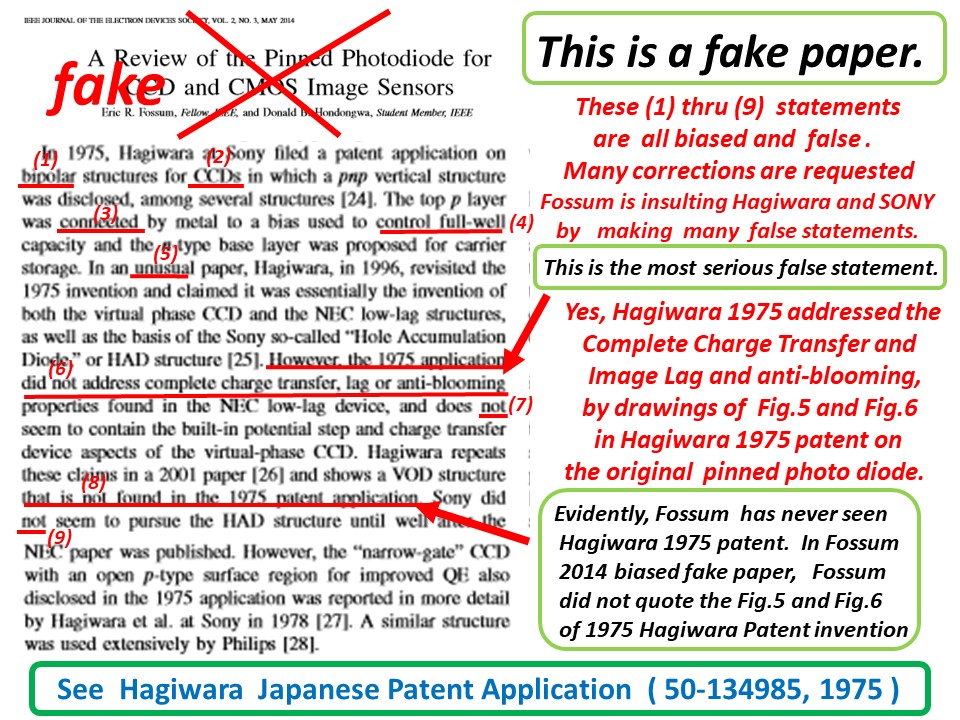

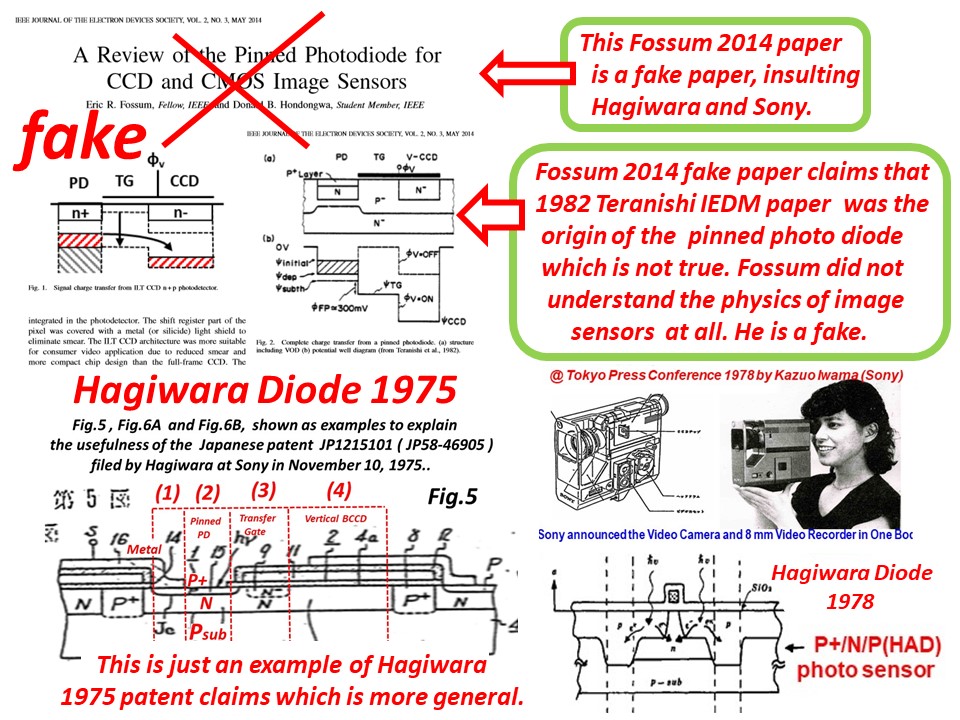

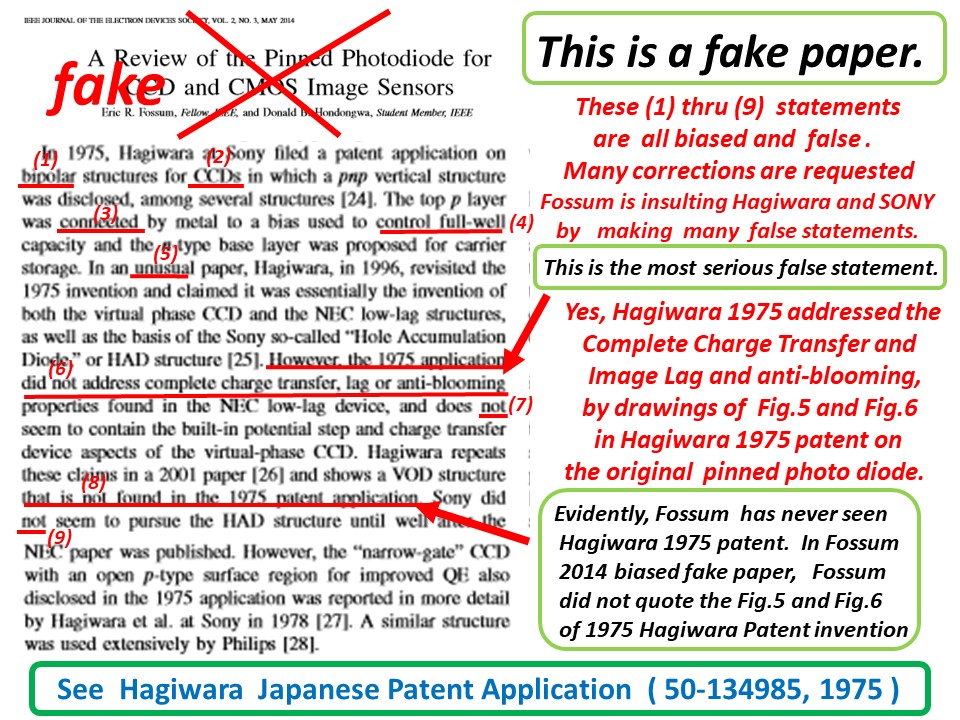

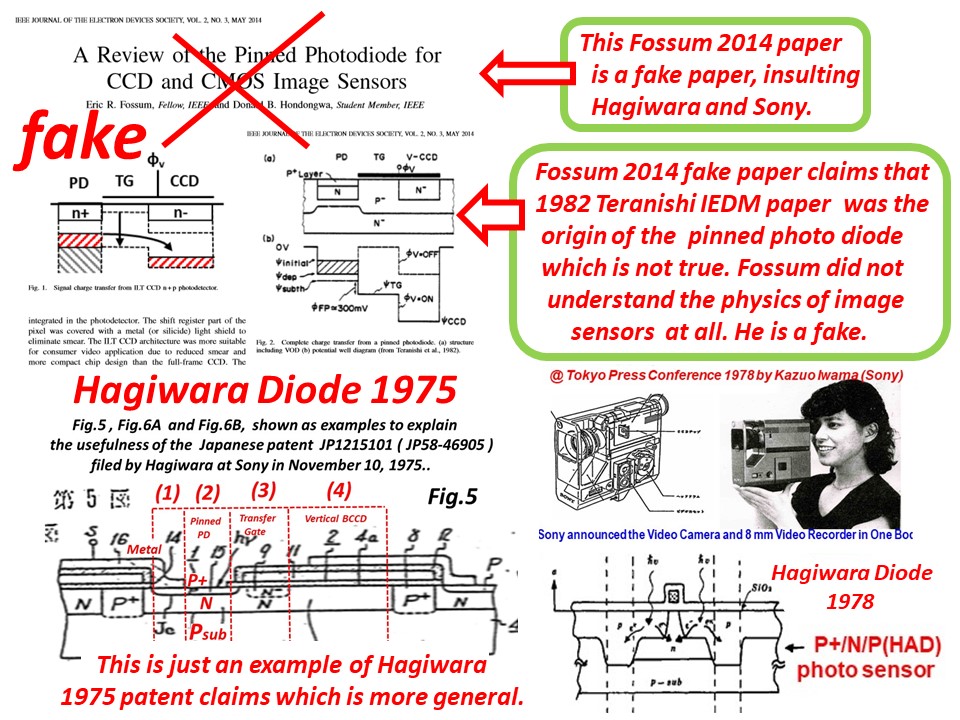

In the Fossum 2014 fake paper, Fossum attacked Hagiwara 1975 patent with lies,

insulting Sony and Hagiwara honor and pride on purpose. I could not understand

Fossum motivation. But I am now convinced that Fossum wanted Fossum himself

to be recognized by the world, with false explanations on Fossum friend Teranishi

as the TRUE inventor of the Pinned Photo Diode,NOT Hagiwara.

Fossum wanted to convince the world that Fossum himself developed the modern

CMOS digital camera. But now I understand that Peter and SONY diligent engineers

including Hagiwara. This is not fair at all. It is all lies. The world should know the truth.

Until last June I did not know what is the Pinned Photo Diode. I knew SONY HAD.

But I did not know myself that SONY HAD and the Pinned Photo Diode are the

same thing. My friends in Sony informed me that Teranish received awards from

Queen Elizabeth and Japanese Emperor as the inventor of the Pinned Photo Diode.

SONY diligent engineers were not happy at all. Maybe, Albert and Peter also felt it

as a bad news ? So I began to study what is Pinned Photo Diode last June.

Then I found the Fossum 2014 fake paper. I became really MAD at Fossum.

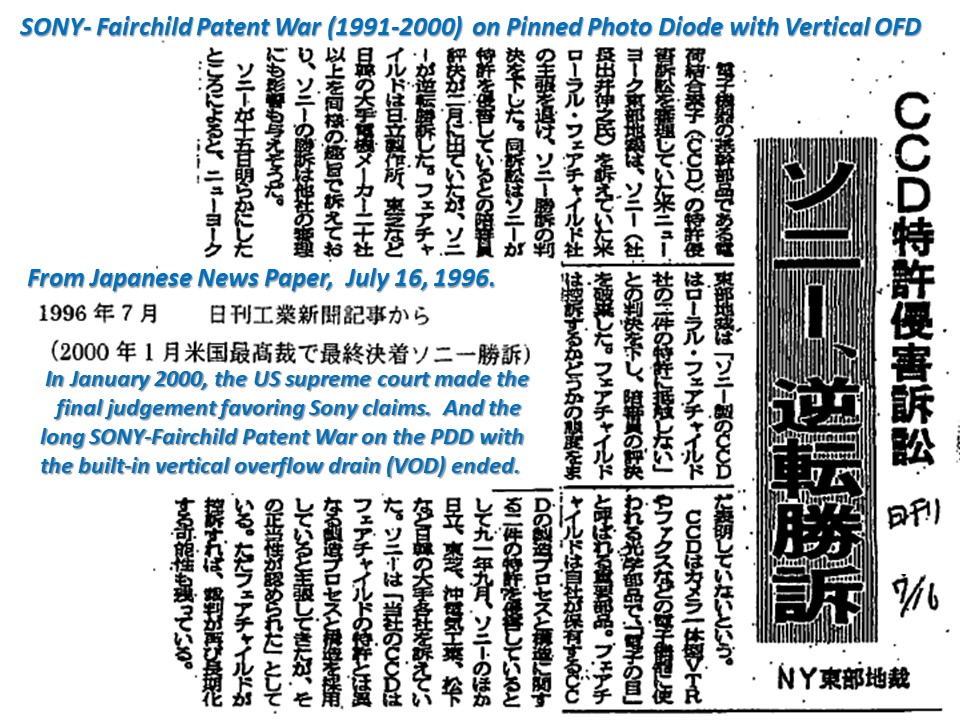

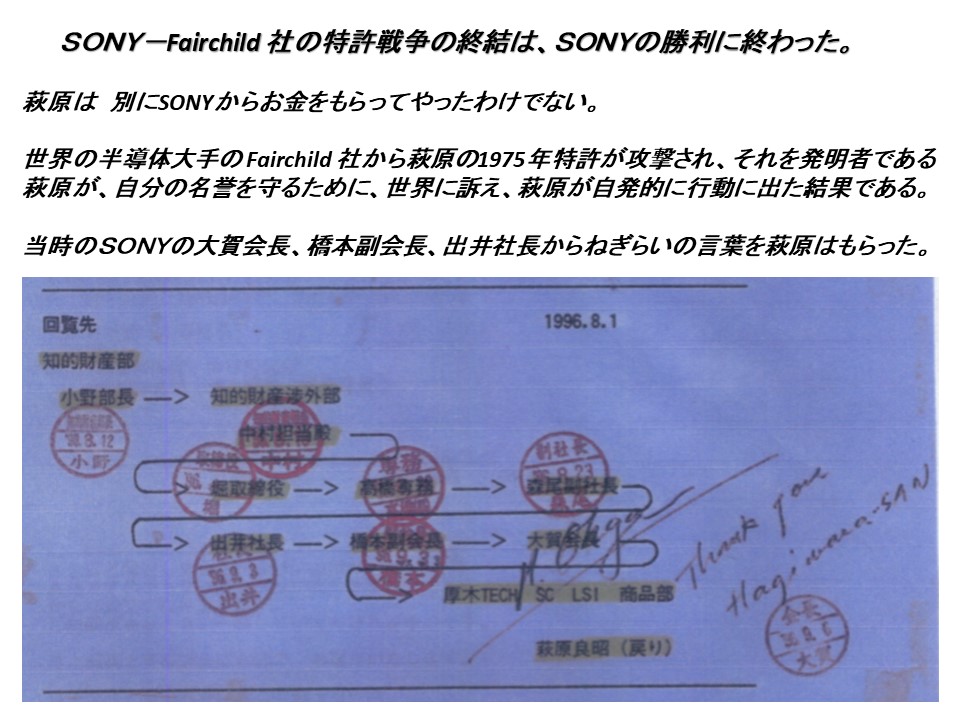

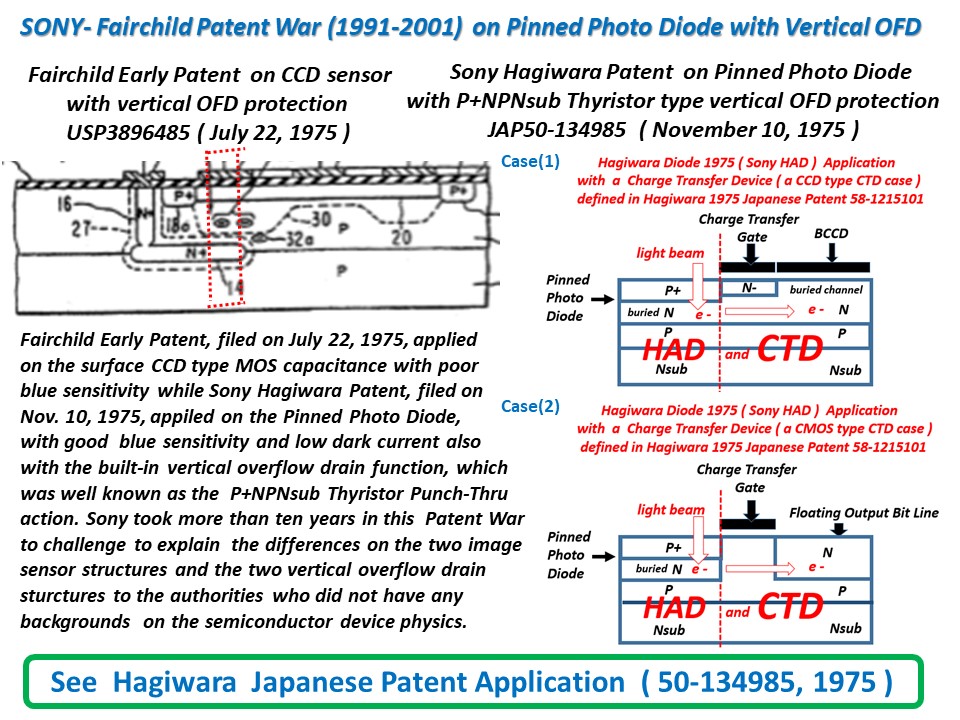

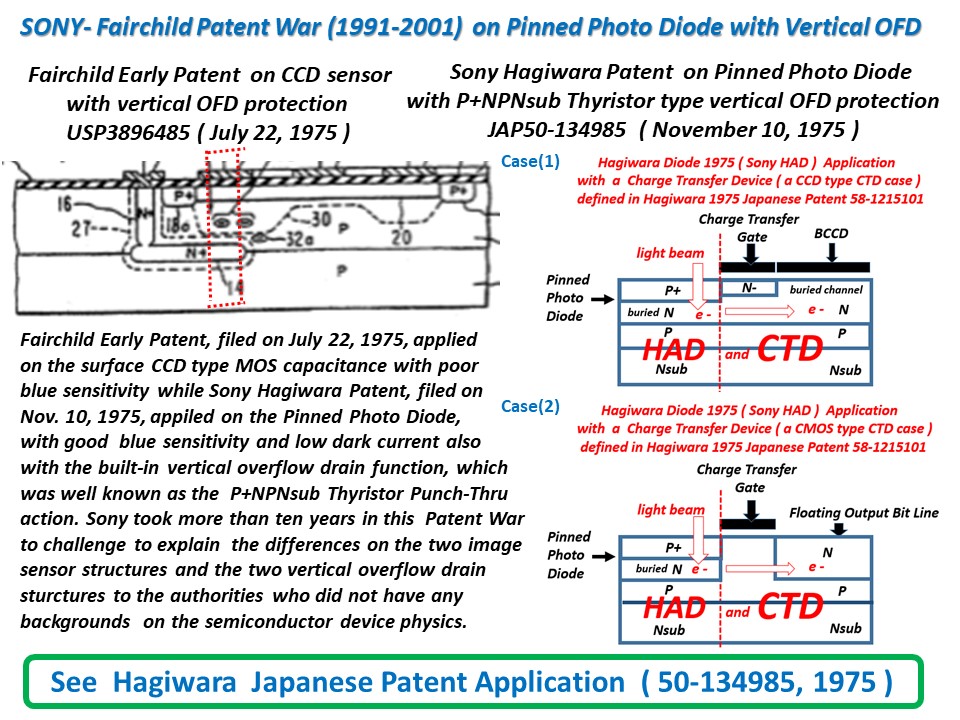

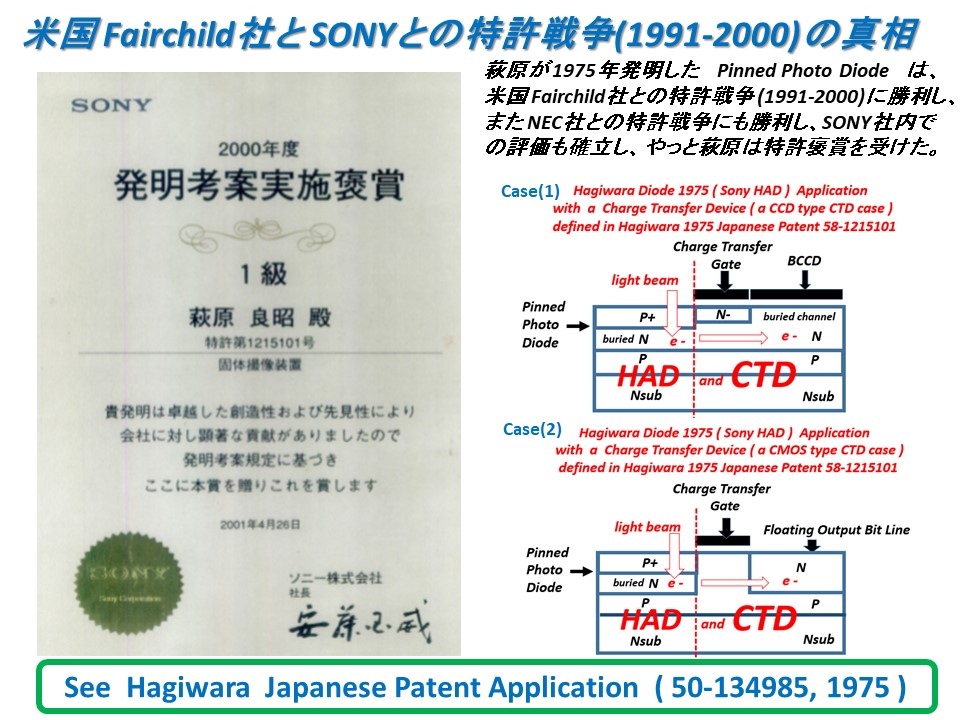

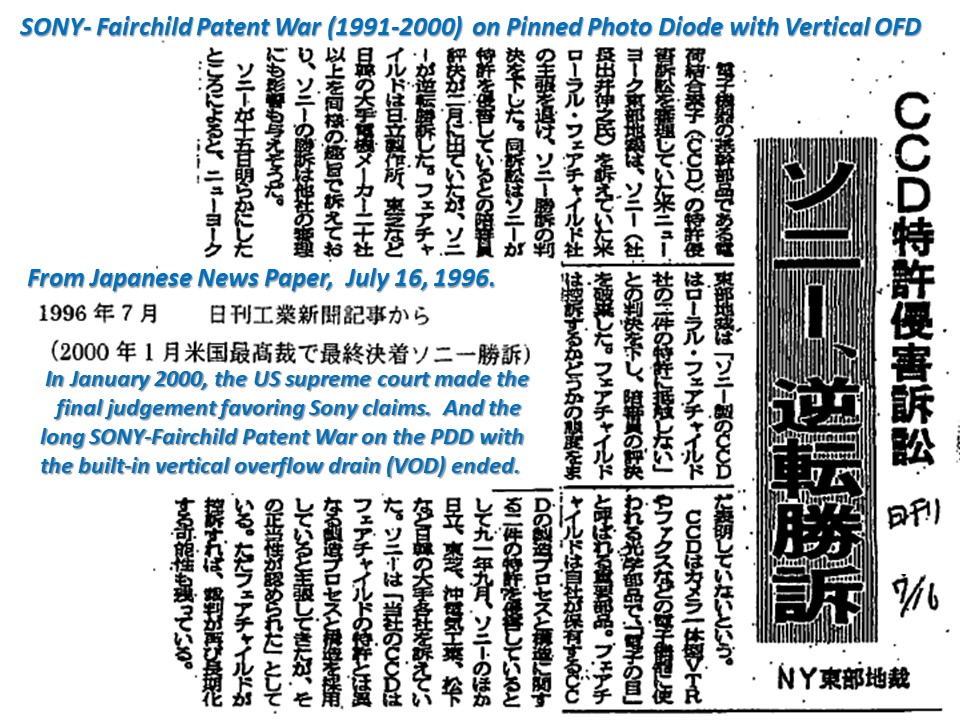

Besides, SONY won the SONY-NEC Patent war by Hagiwara 1975 patent

against the Teranishi1979 patent a long time ago. So Teranish should know that

Hagiwara is the inventor even though Teranishi published his work in IEDM1982.

Teranishi work was just a copy of Hagiwara 1975 patents that defined as one

Example case of Interline CCD image sensor with the complete charge transfer

Mode ( no image lag ) P+NPNsub junction type photon detector structure,

which is now called as the Pinned Photo diode.

But it is now more than four years after Fossum 2014 fake paper publication.

I found this fake paper, really too late.

I was very, very late since I do not belong to the image sensor community any more.

Yes, with my interests in the intelligent image sensors included, but my current major

interests are in the AIP ( Artificial Intelligent Partner ) systems, including AI software

and AI digital circuit system applications.

Yes, I try to be calm, but cannot be silent.

I feel that the world should know at least what is the truth.

I don’t think I can change the past history.

But people can learn the truth anytime, now and in future.

Yes, many people contributed.

Their diligence and efforts must be much worth recognitions.

*******************************************************************

http://www.aiplab.com/Hagiwara_at_Sony_is_the_true_inventor_of_Pinned_Photo_Diode.html

http://www.aiplab.com/Story_of_Pinned_Photo_Diode.html

http://www.aiplab.com/

*******************************************************************

*******************************************************************

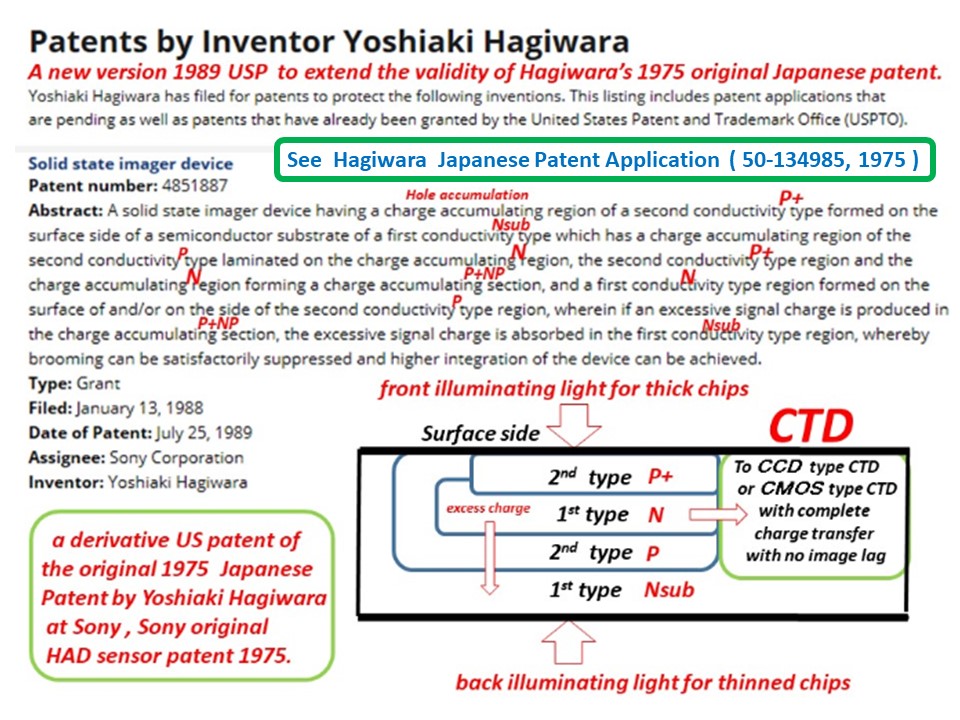

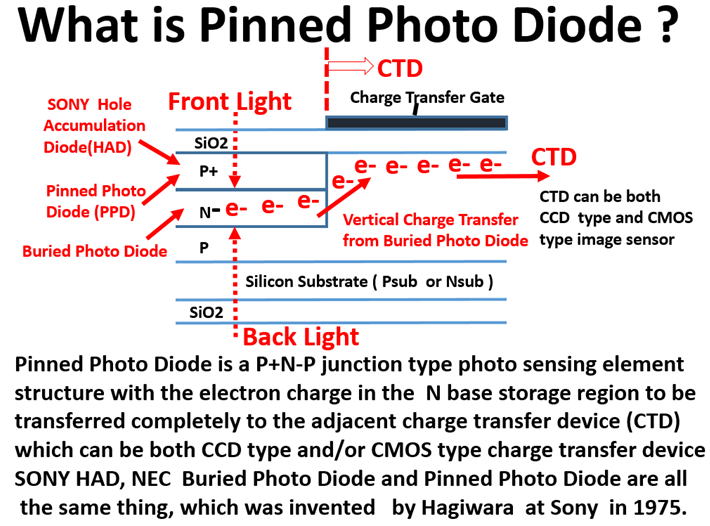

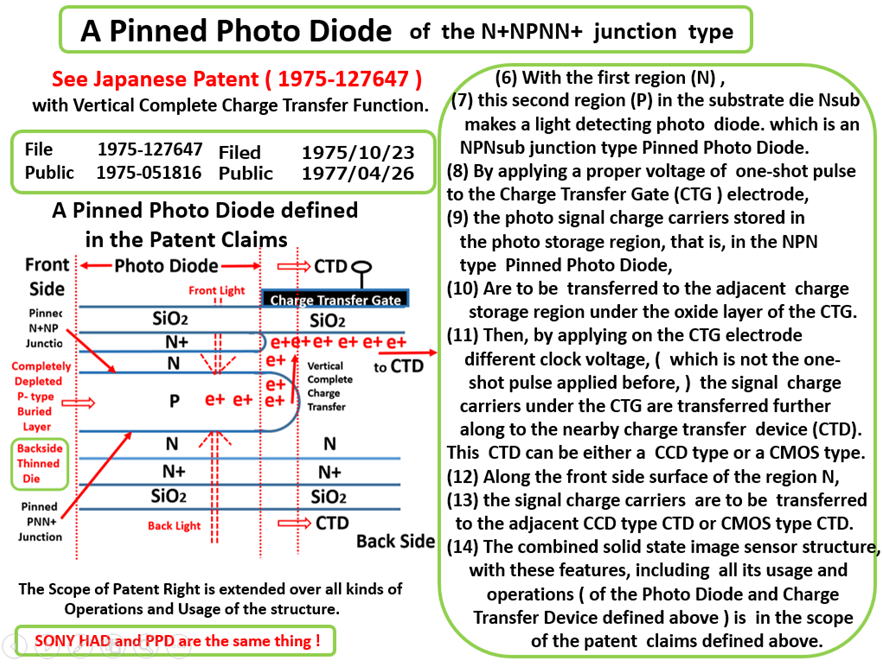

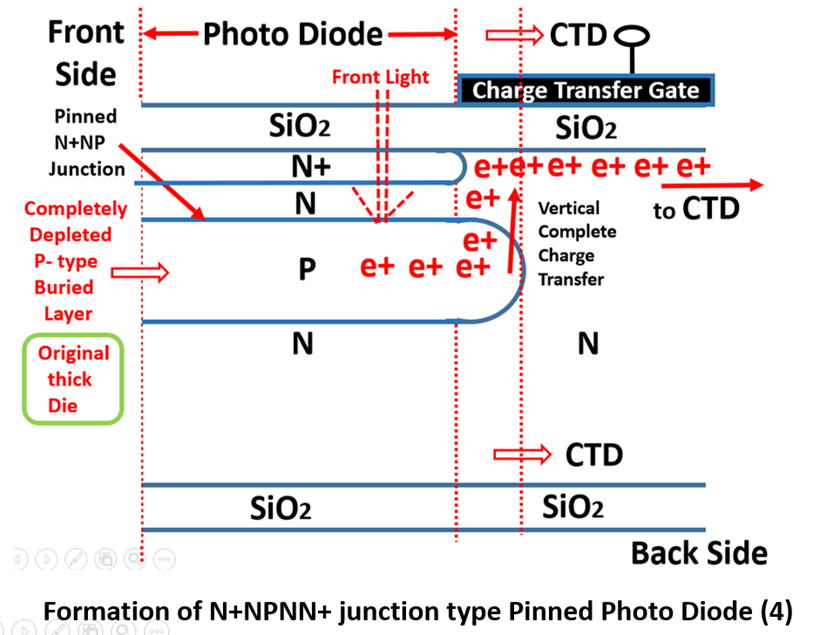

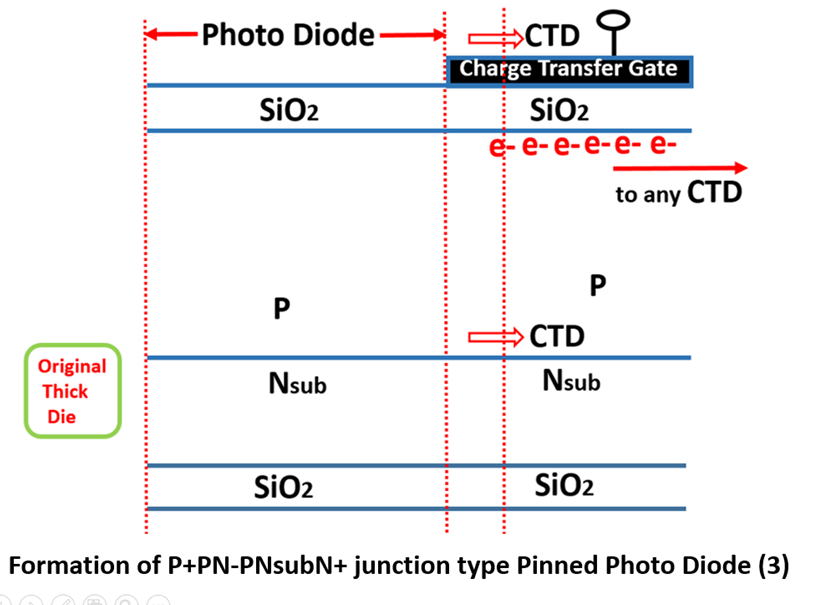

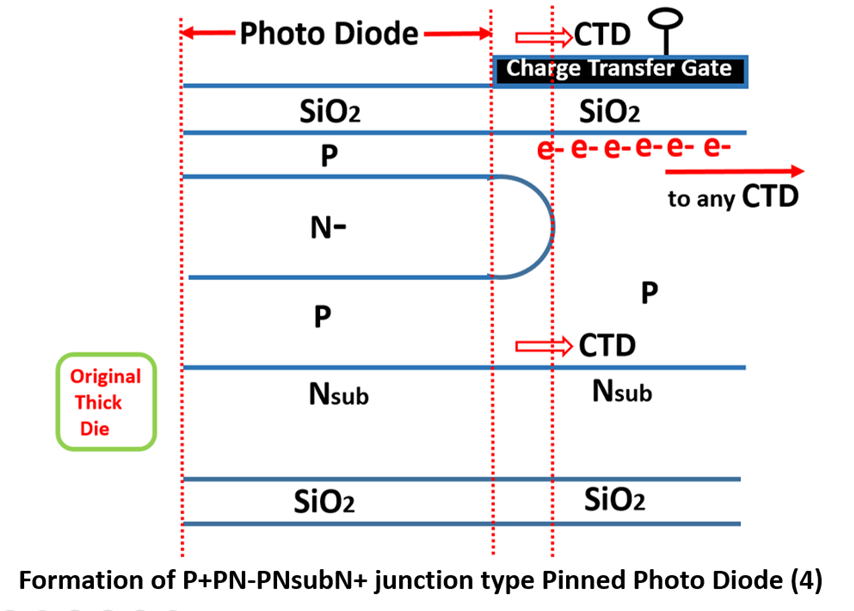

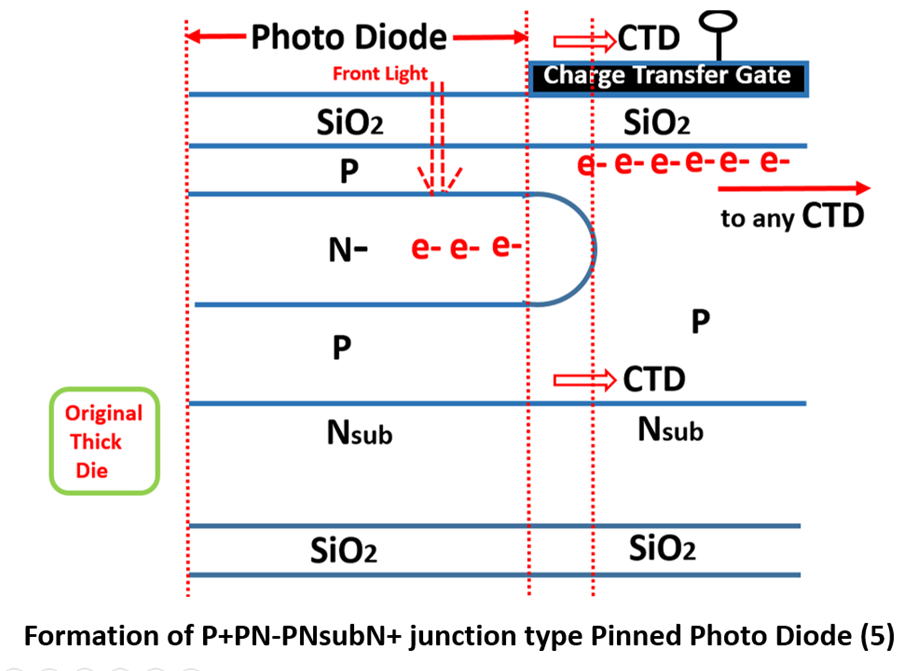

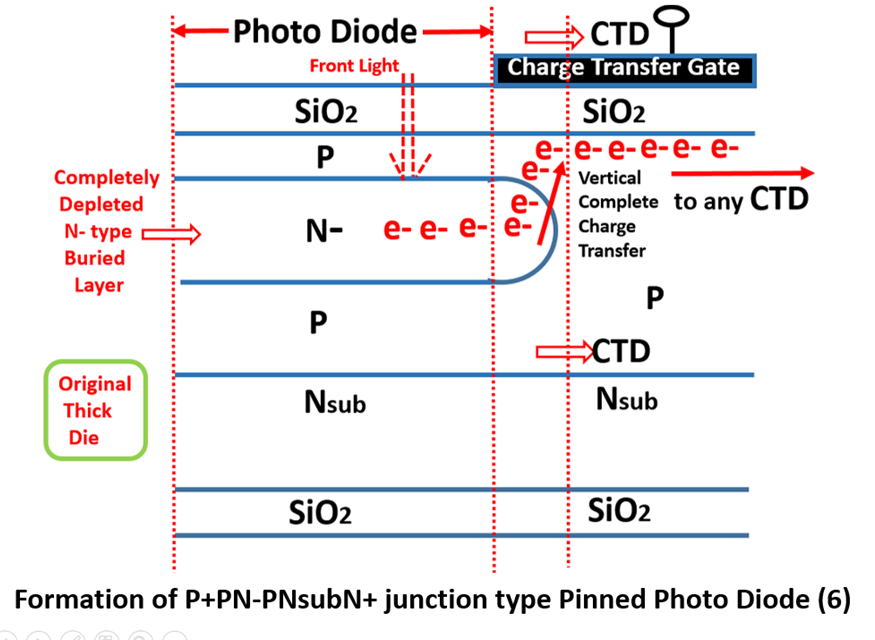

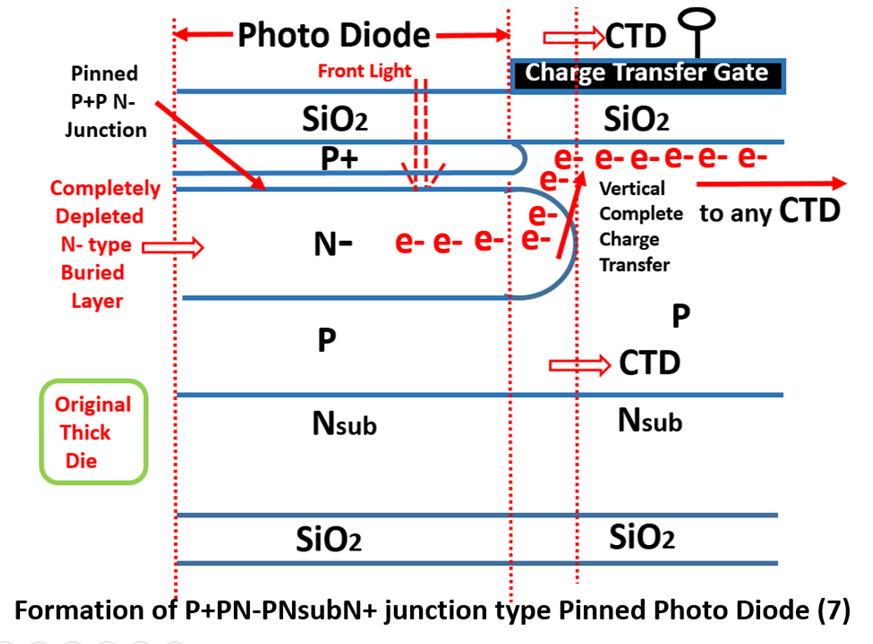

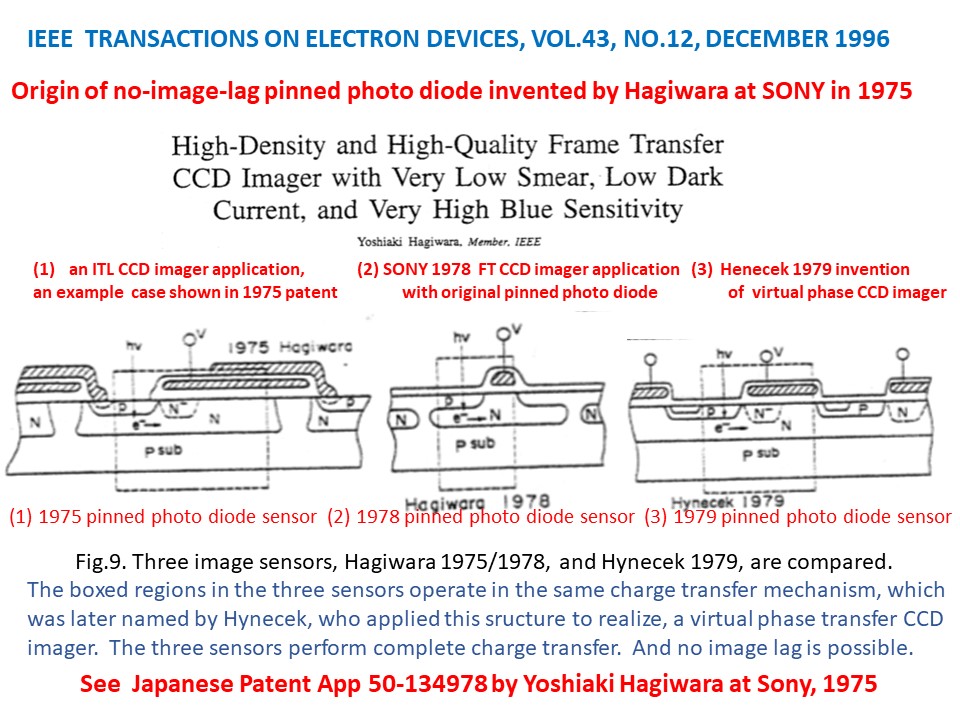

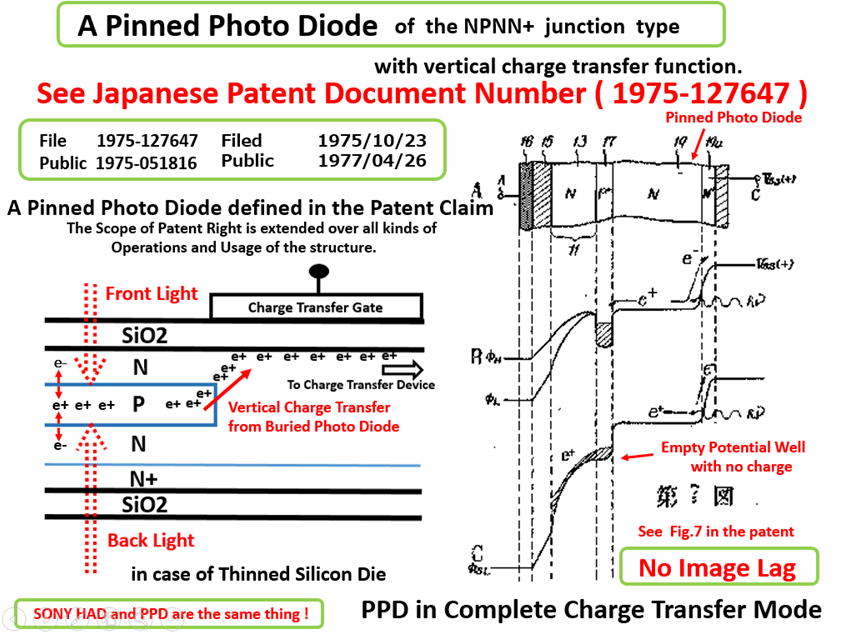

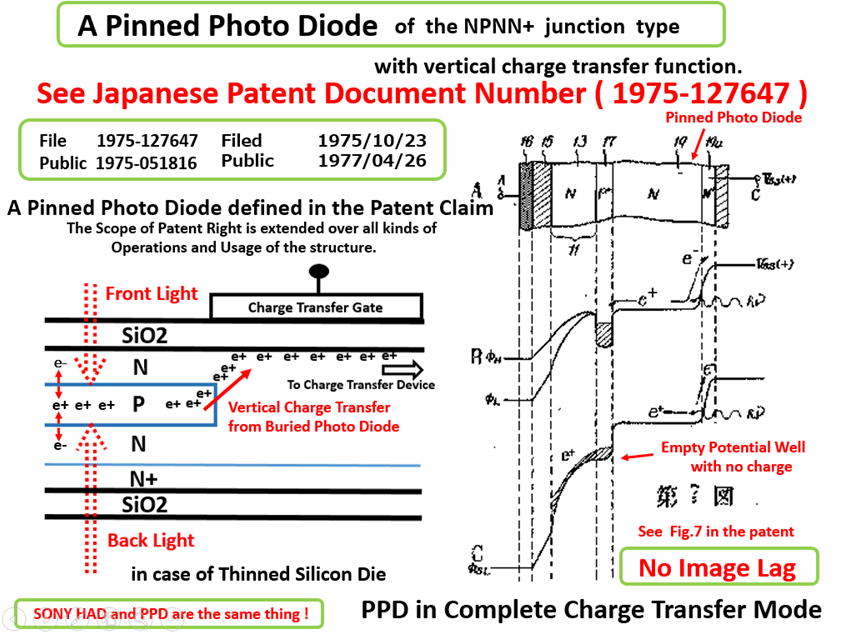

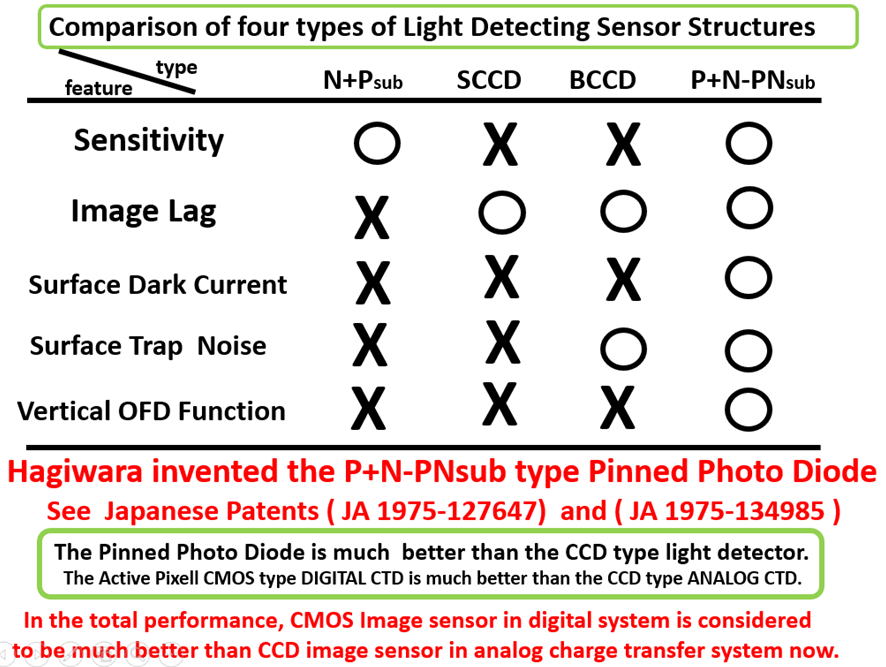

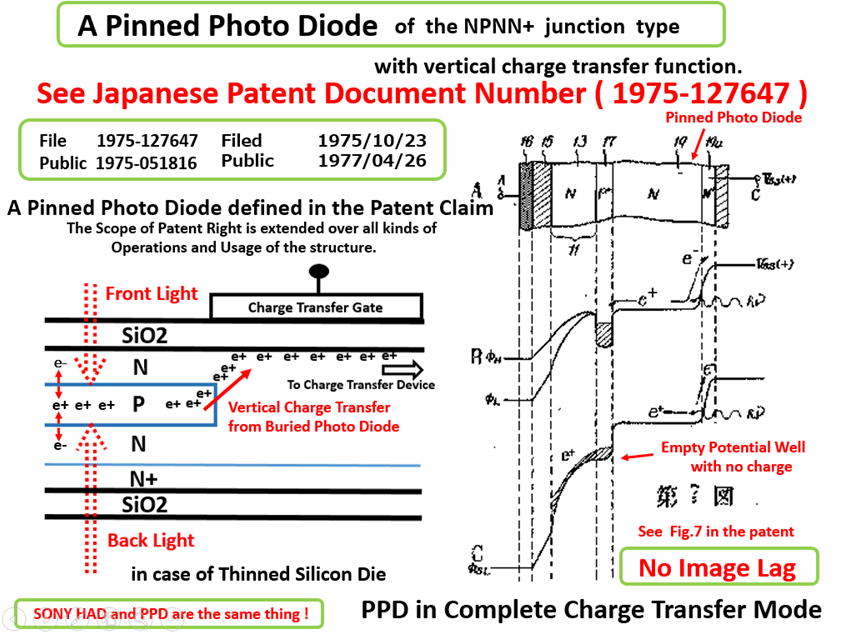

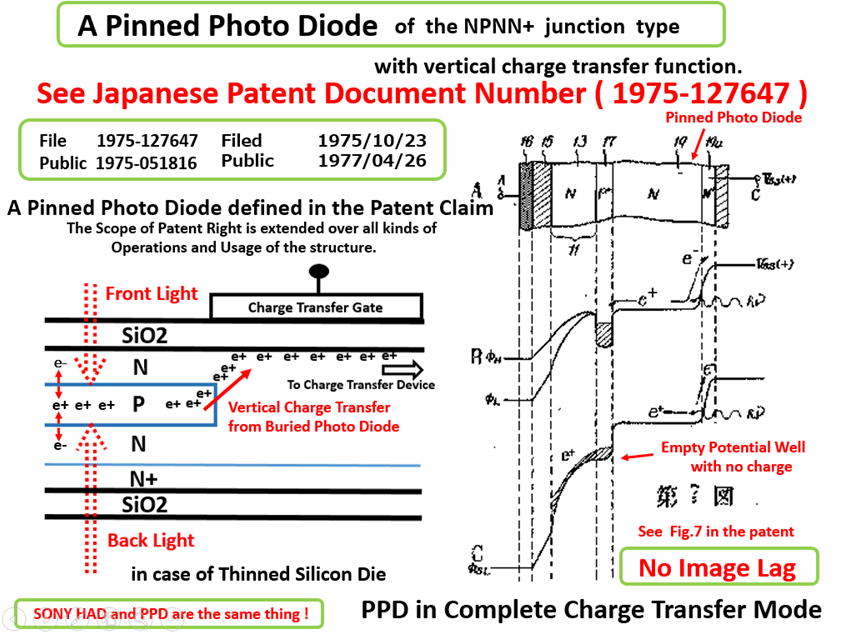

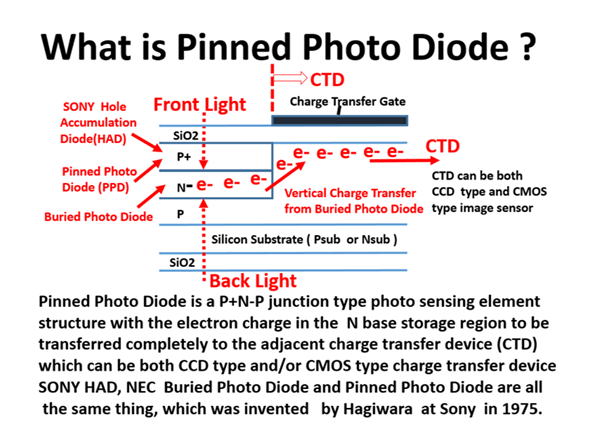

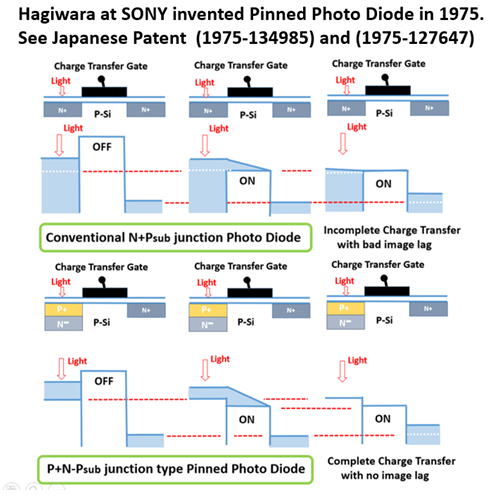

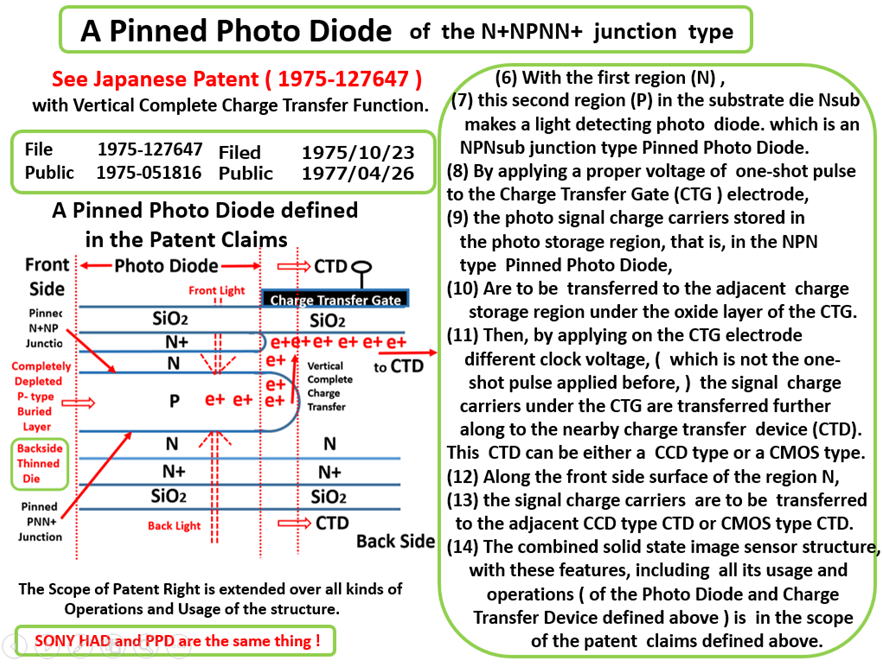

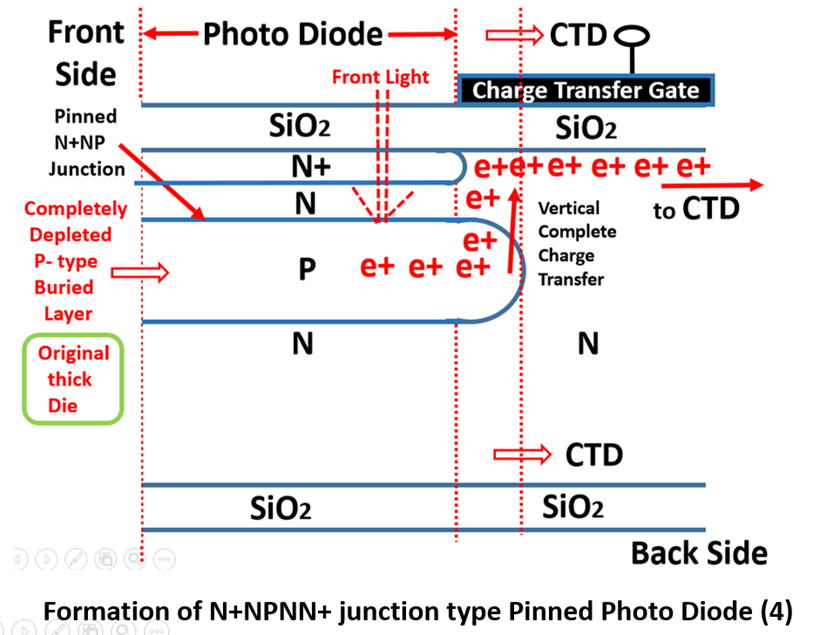

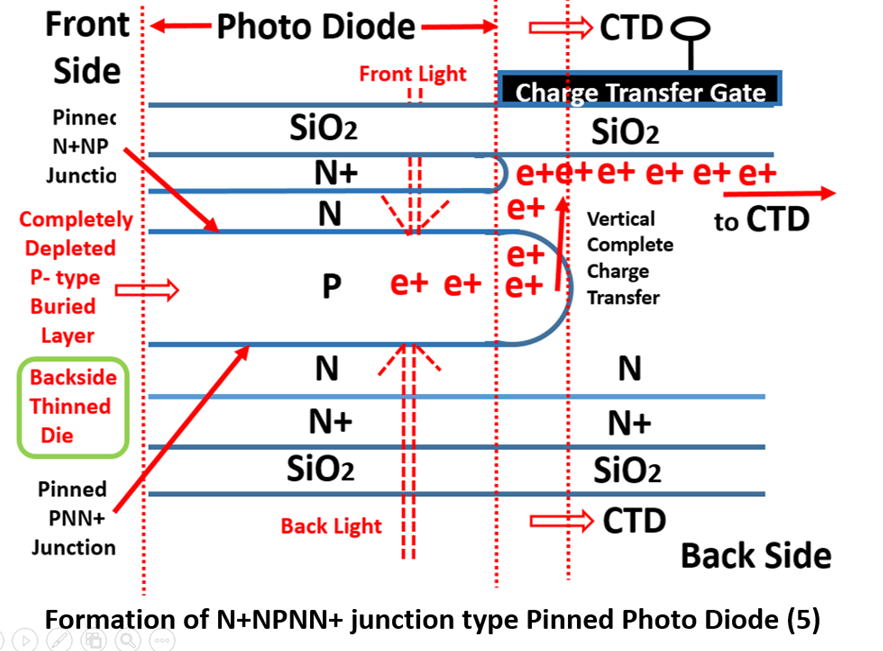

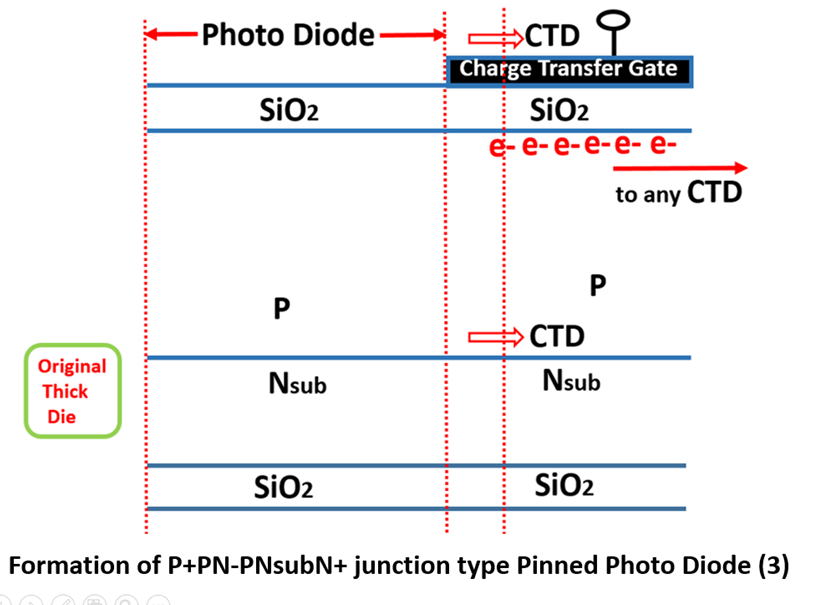

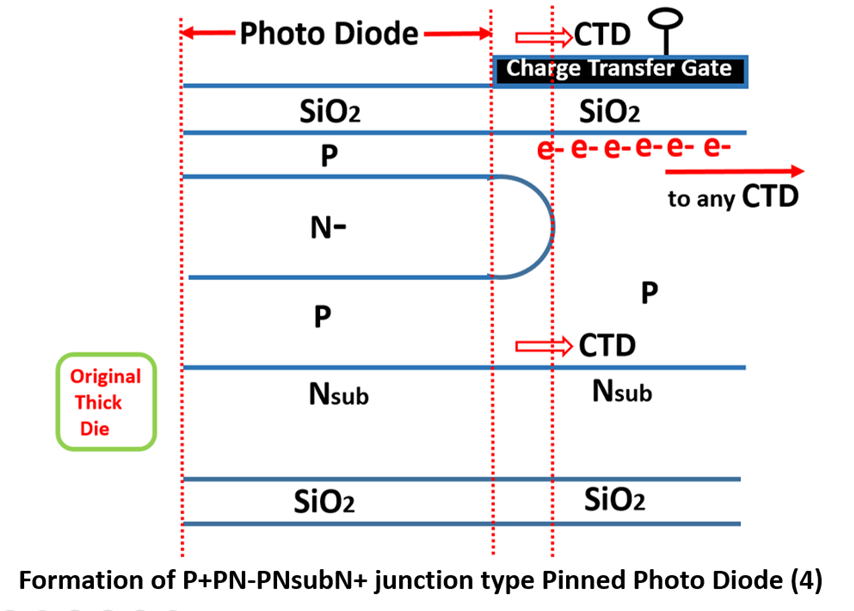

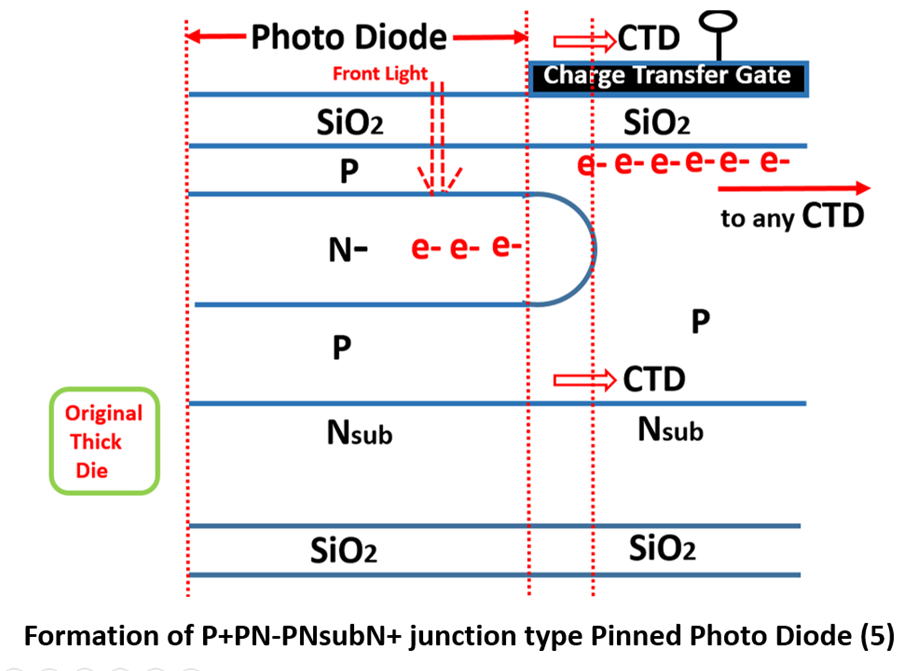

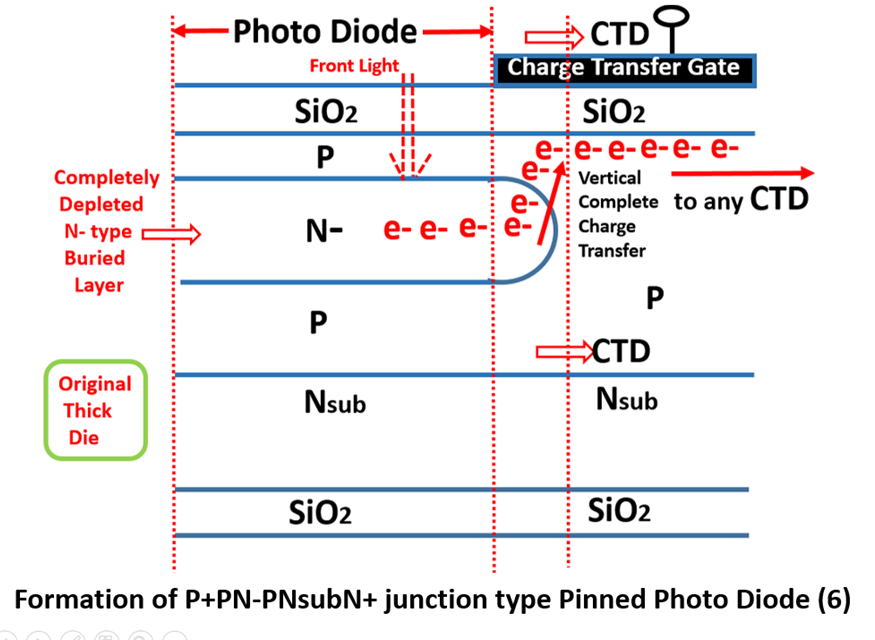

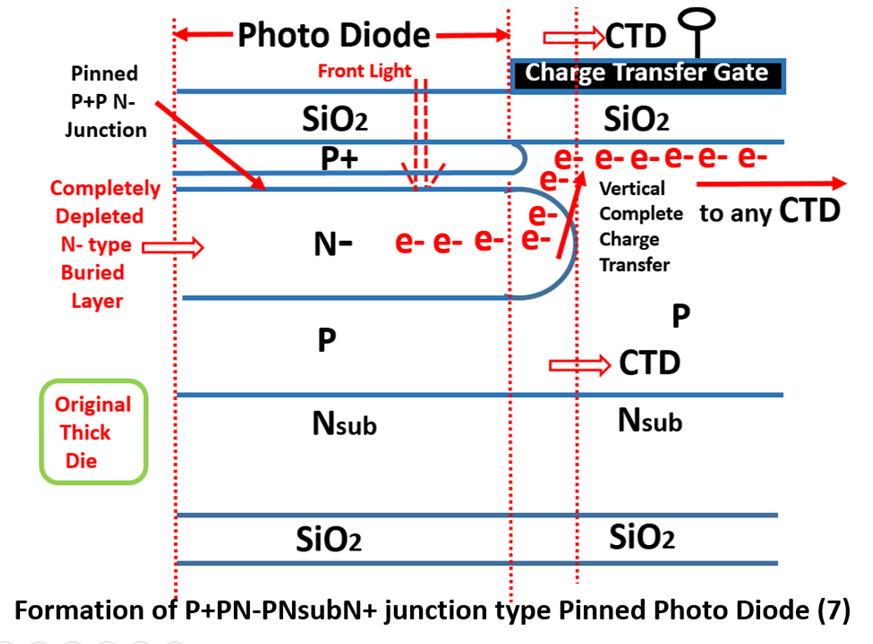

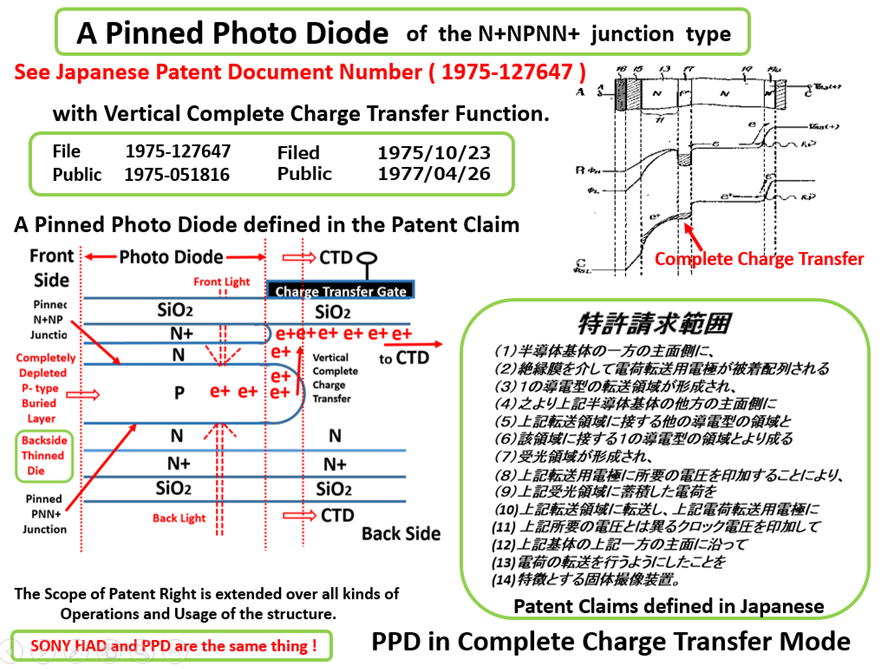

Hagiwara invented the Pinned Photo Diode as shown below.

**************************************************************************

Evidence that Hagiwara at Sony is the true inventor of the Pinned Photo Diode

**************************************************************************

Evidence that Hagiwara at Sony is the true inventor of the Pinned Photo Diode

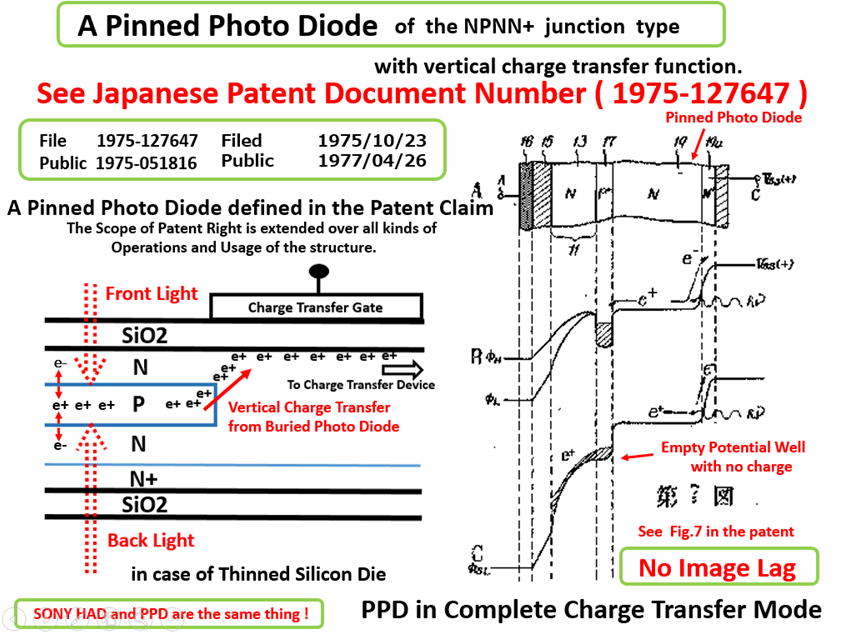

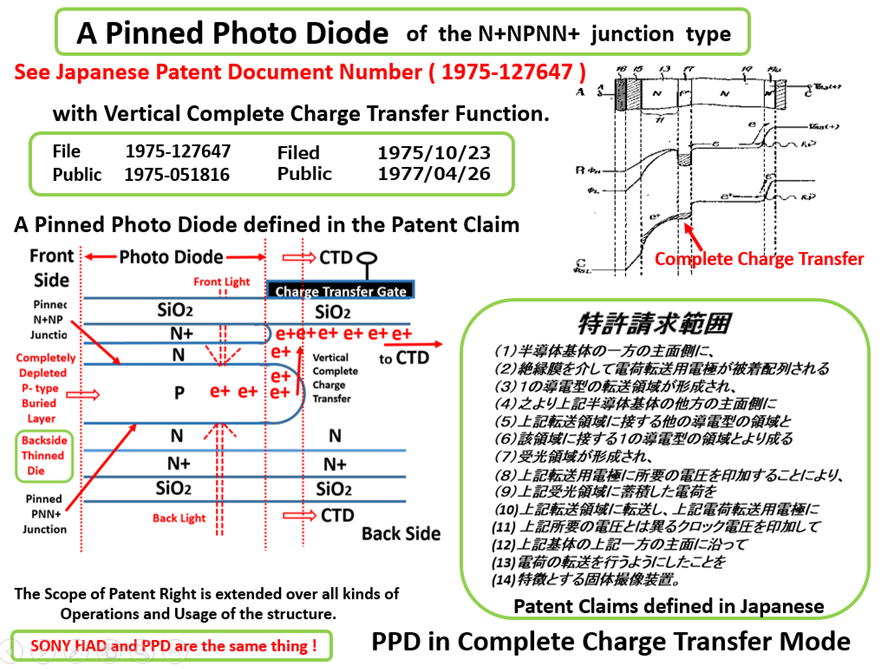

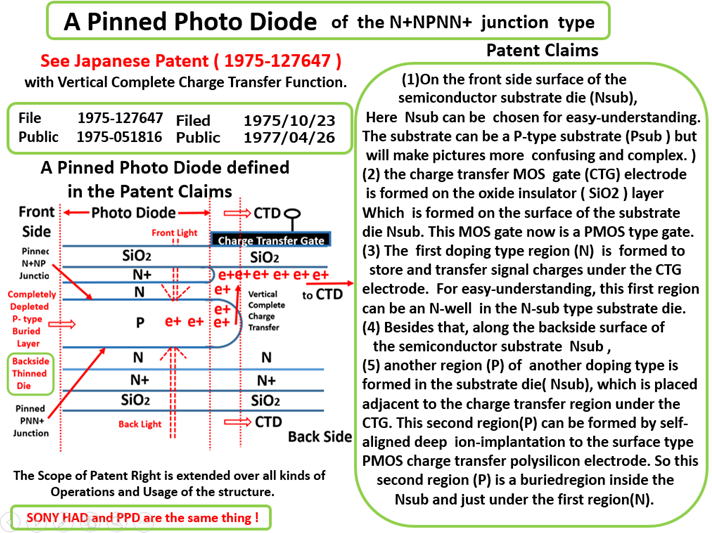

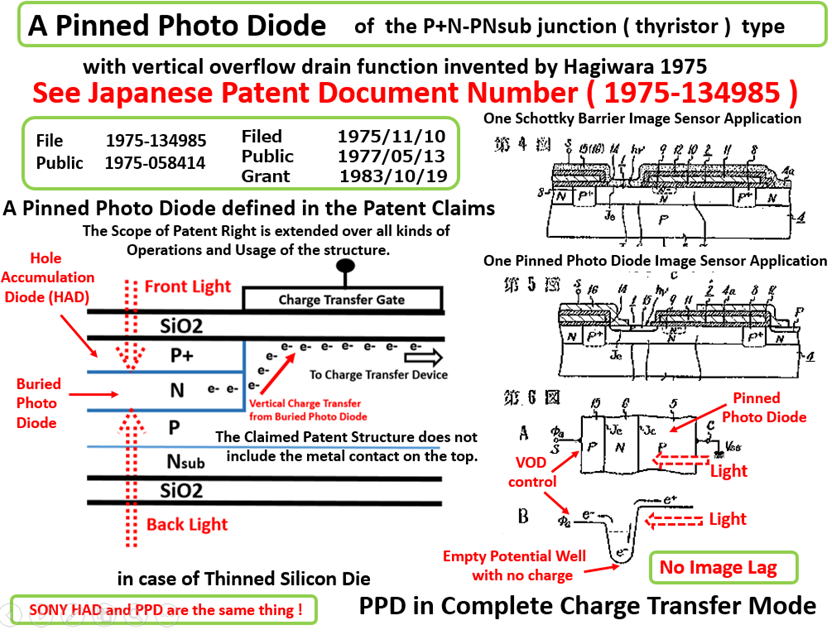

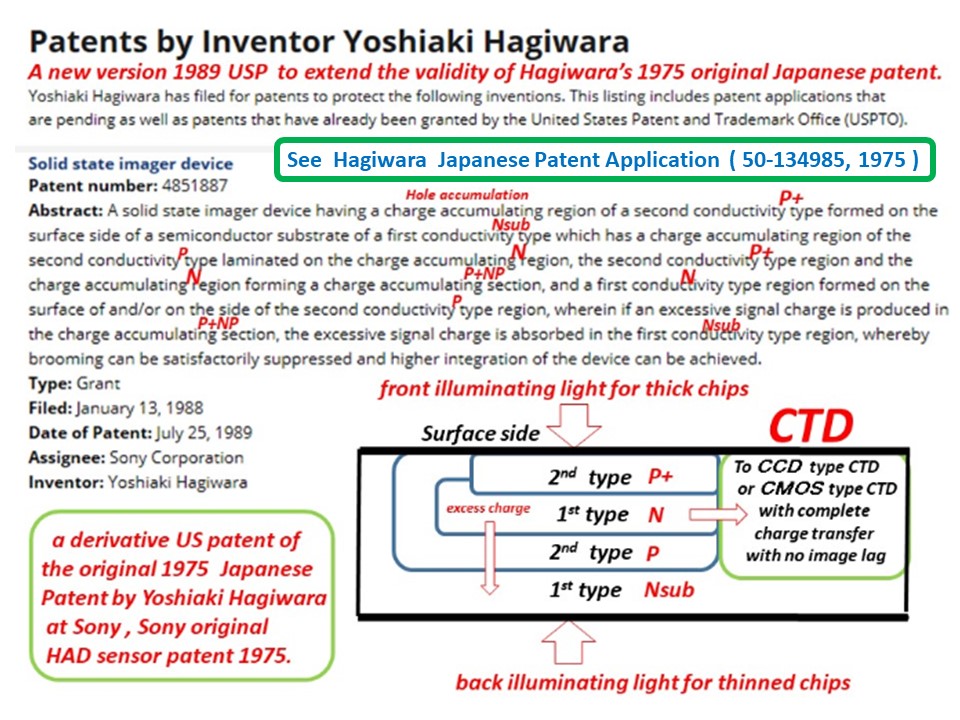

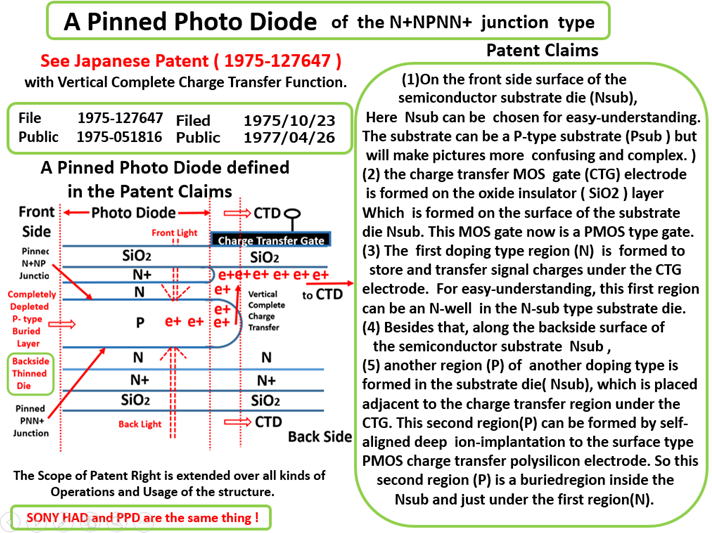

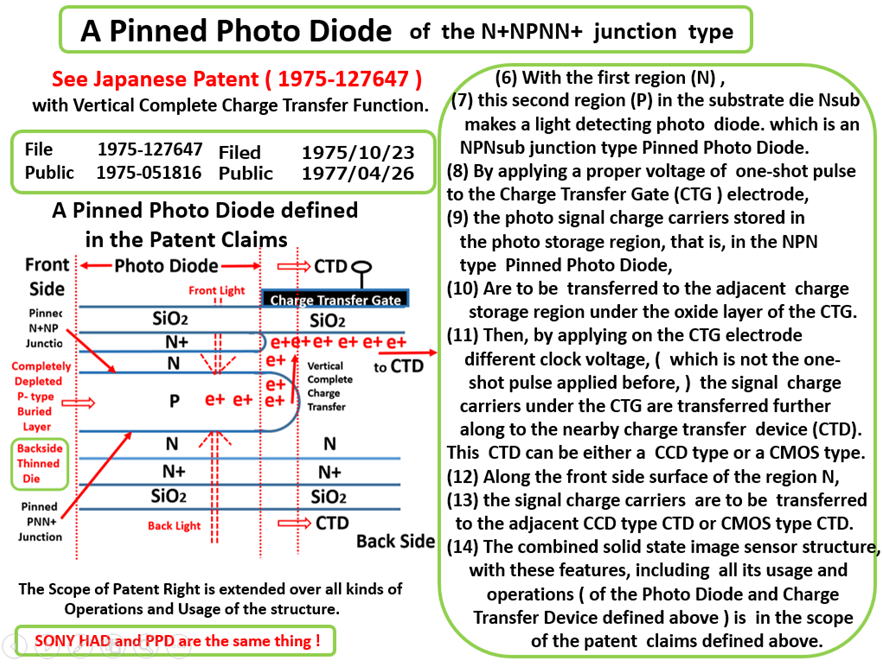

is given by the two Japanese patents Hagiwara filed in 1975 at Sony. They are,

Japanese Patent (1975-127647) and (1975-134985). The evidence is described in

details in these two Hagiwara 1975 Japanese patents.

In 1978 Sony announced a new video camera in Tokyo and New York Press

Conferences at the same date, held by Sony Chairman Akio Morita in New York

and Sony President Kazuo Iwama in Tokyo at the same date in 1978.

The video camera announced in the two Press Conference was built with the

Frame Transfer CCD image sensor with the Pinned Photo Diode light detecting

photo sensing picture cell structure that Hagiwara invented in 1975, which has

a very light sensitivity, a very low noise and a very low image lag features.

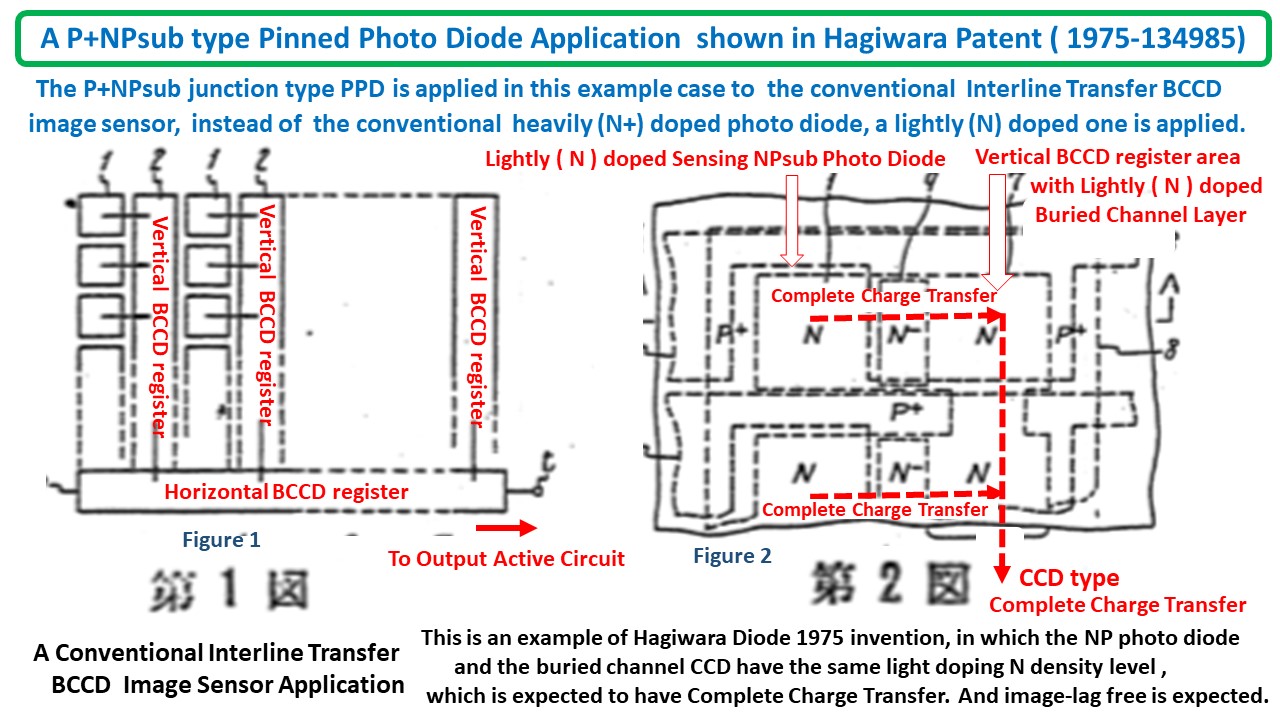

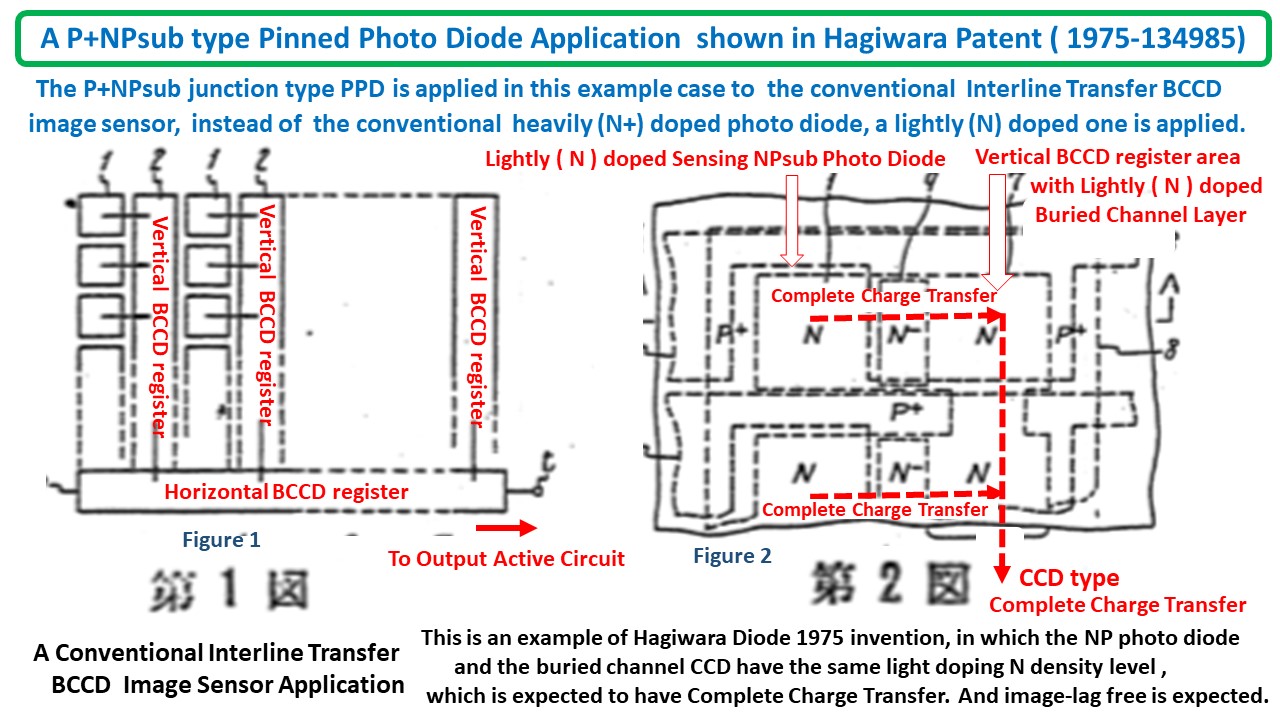

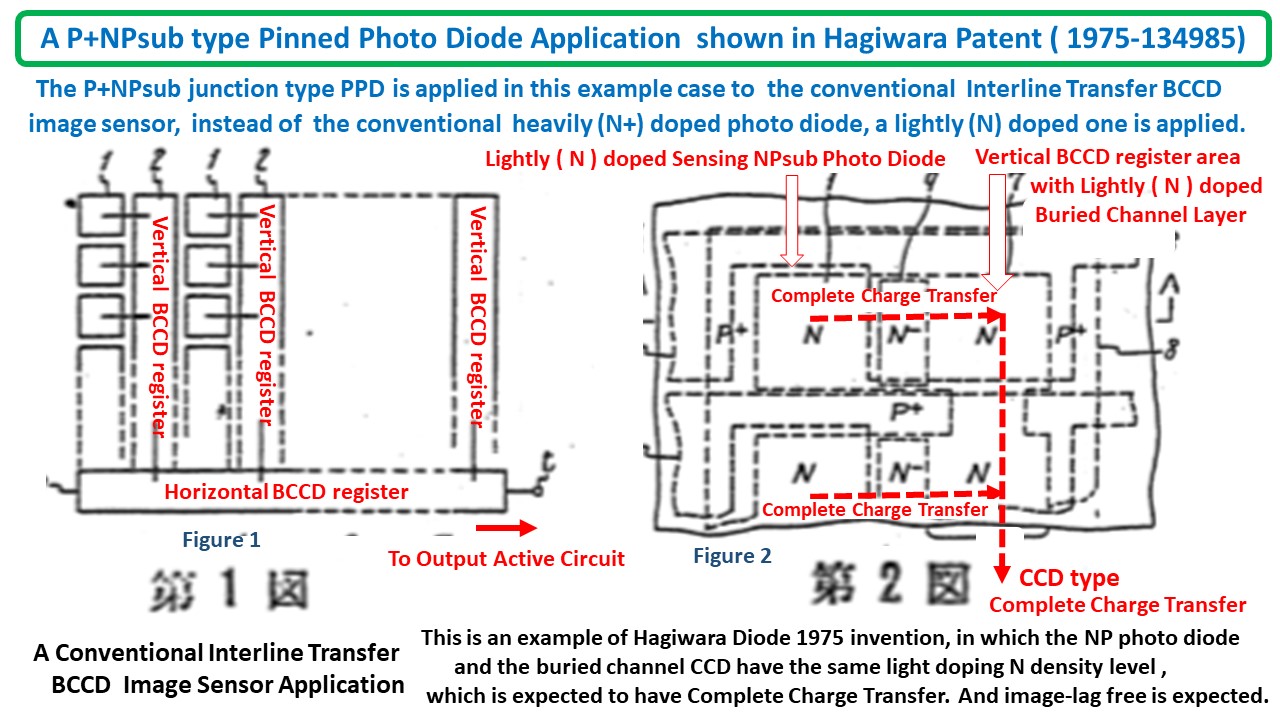

The figures N0.1 thru No.5 in Hagiwara Japanese patent (1975-134985)

explained in details an example of the interline transfer CCD image

sensor application with the Hagiwara invented Pinned Photo Diode.

Sony engineers, after the 1978 Press Conferences in Tokyo and New

York, worked hard for, and succeeded to acquire, the production

and the reliability technolgy of the CCD video camera of the interline

transfer CCD image sensor application with the Pinned Photo Diode

light detecting picture cell structure with the vertical overflow function.

With the diligent SONY engineers efforts, SONY could produce the

portable Passport size Compact CCD image sensor video camera, with

the Pinned Photo Diode that Hagiwara invented in 1975.

And at the same time, Sony filed a trading name officially, which

is the SONY Brand Name of " Sony original HAD sensor " .

With the help of the Hagiwara invented Pinned Photo Diode, which

was now called as " Sony original HAD sensor " with the strong

SONY original sales features of high light sensitivity, low noise and

no image lag characteristics, Sony could become soon very dominant

and strong over the world consumer video camera markets.

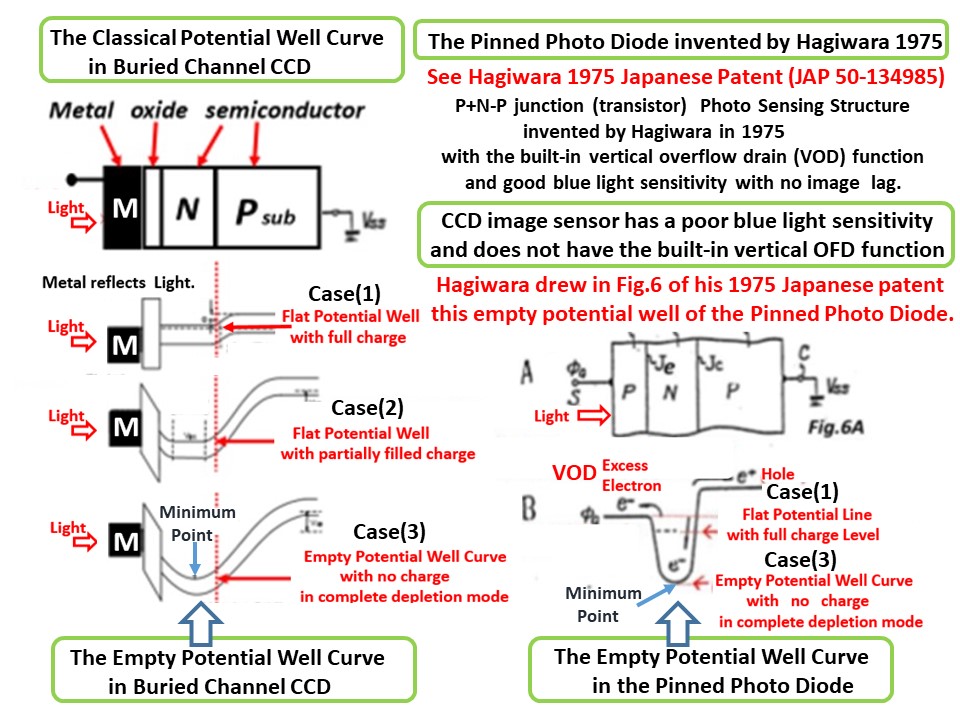

The feature of no image lag characteristics in the Hagiwara invented

Pinned Photo Diode is explained and shown in details, as an example

application case, in the figure No.6 of Hagiwara 1975 Japanese Patent

( 1975-134985 ) and also in the figure No.7 of Hagiwara 1975 Japanese

Patent ( 1975-127647 ) in details.

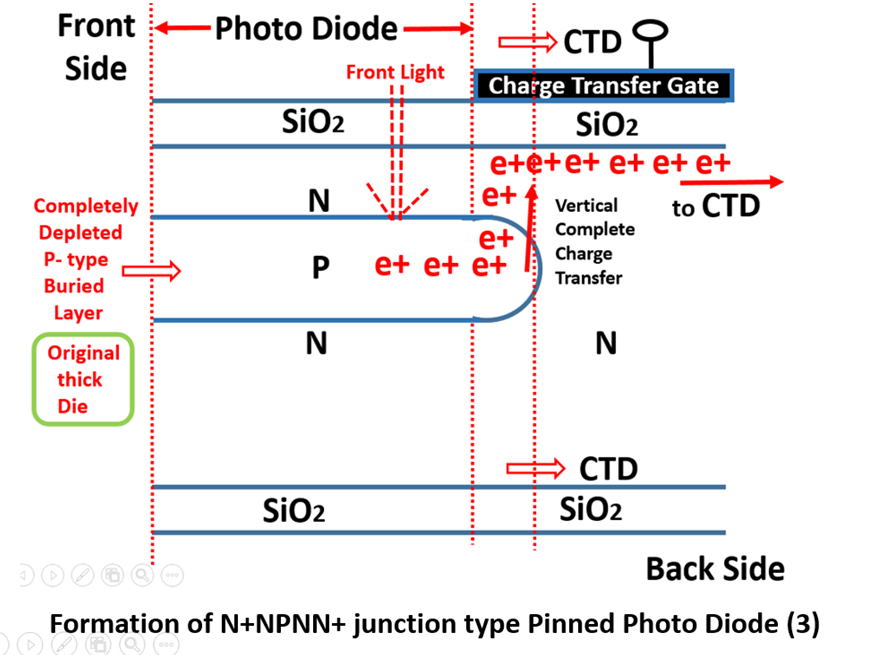

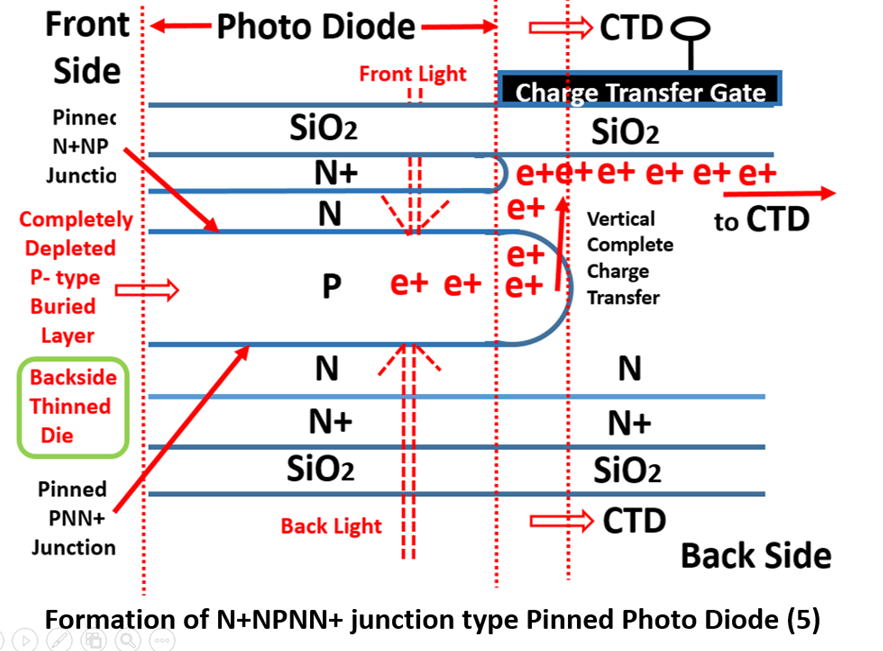

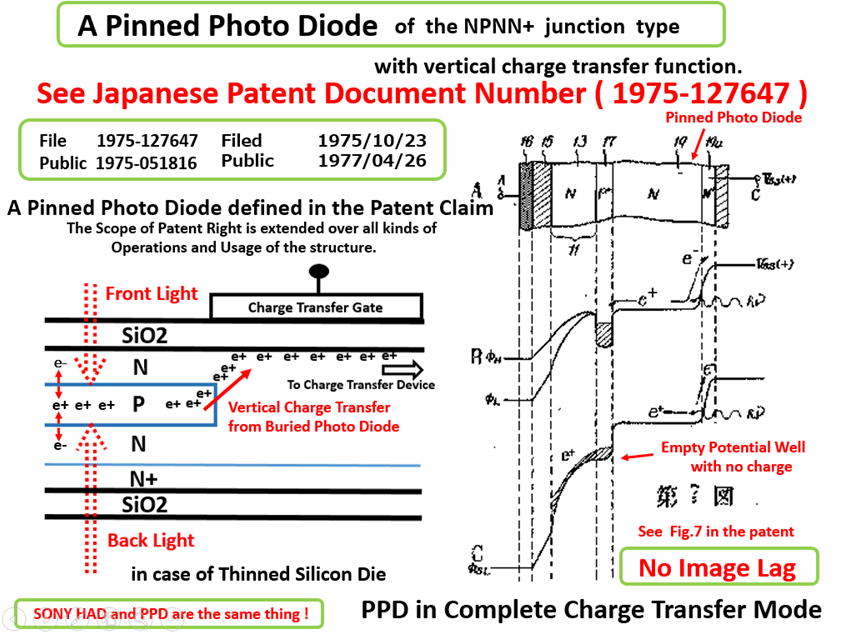

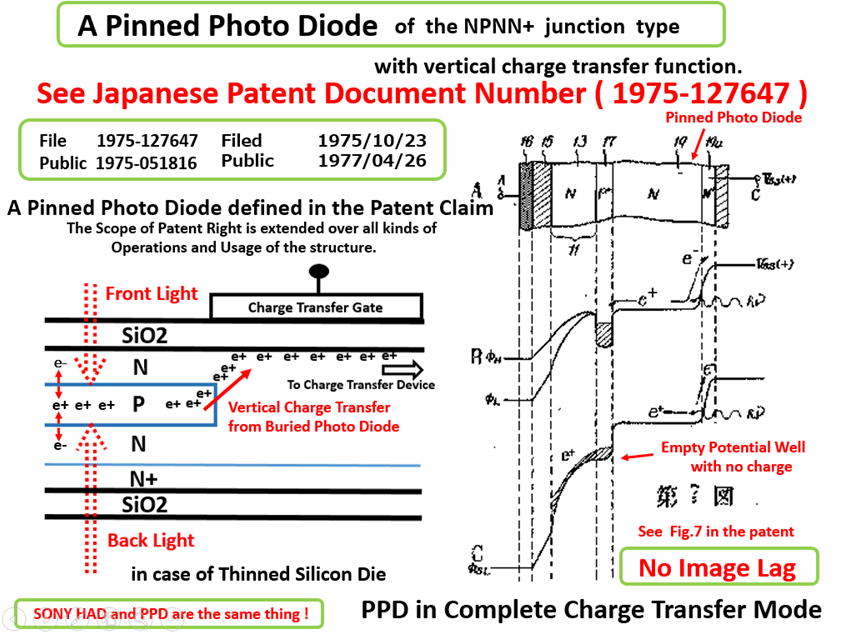

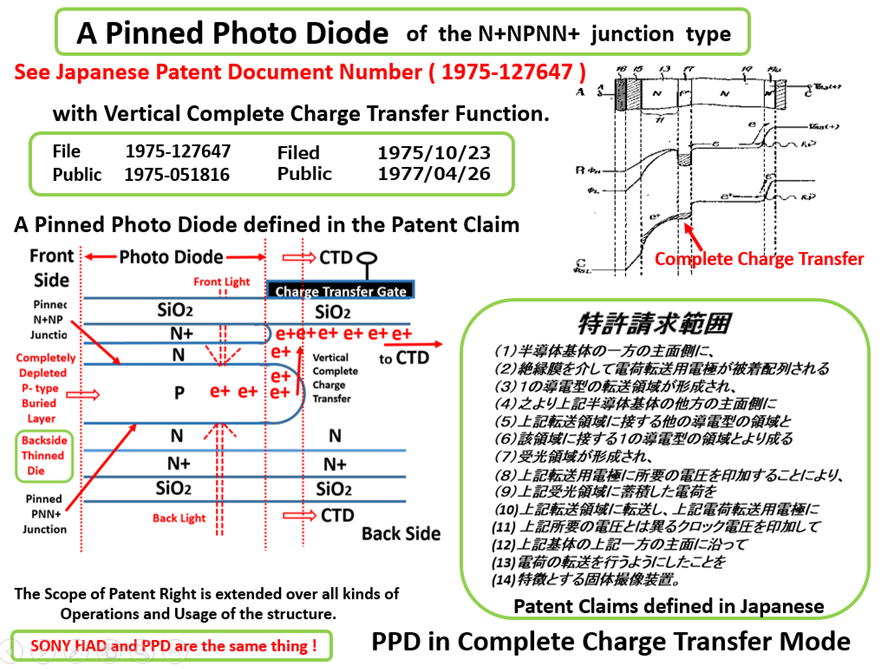

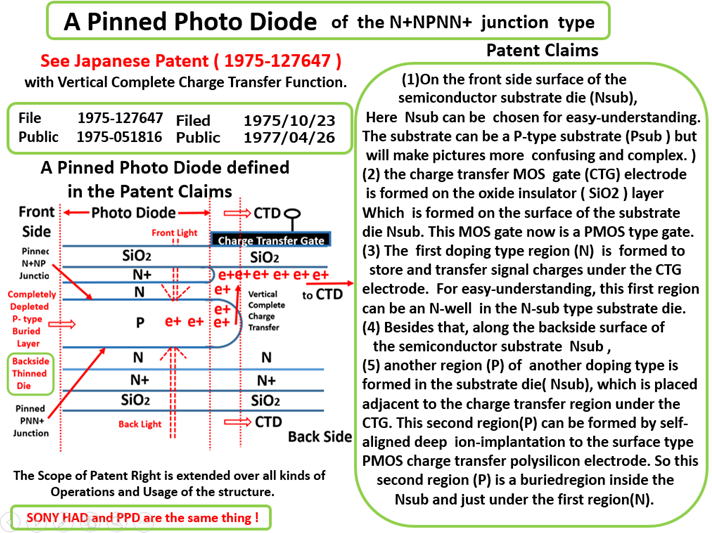

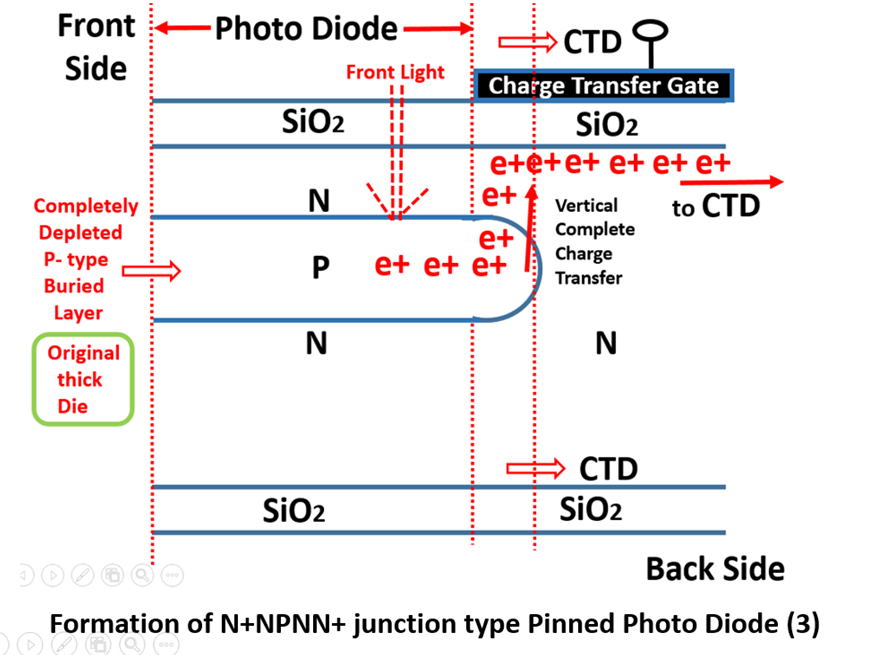

Hagiwara 1975 Japanese Patent ( 1975-127647 ) proposed a Back Light

illumiantion type light detecting photo sensing picture cell structure

with the buried layer type photo signal charge storage. And in the

figure No.7 of Hagiwara 1975 Japanese Patent ( 1975-127647 ) was

shown clearly how the signal charge in the buried storage layer are

trasfered completely to the region under the charge transfer gate

formed on the front side of the silicon wafer. This means clearly

the light sensing picture cell structure, which is now worldly called

as the Pinned Photo Diode, has the very important feature of no

image lag characteristics.

All of these Patent Claim descriptions and Patent figures for possible

patent application examples given in details in the two Hagiwara 1975

Japanese Patents ( 1975-127647 ) and ( 1975-134985 ) support the fact

that Hagiwara is the true inventor of the Pinned Photo Diode.

In conclusion, it is a clear cool fact that Hagiwara at Sony is the true

inventor of the Pinned Photo Diode. The Haiwara patents claims that

the light detecting picture cell structure ( now called as the Pinned

Photo Diode ) can be applied to any kind of charge transfer device(CTD)

which includes the BBD type, the classical MOS type, the CCD type and

the modern CMOS image sensor type charge transfer devices.

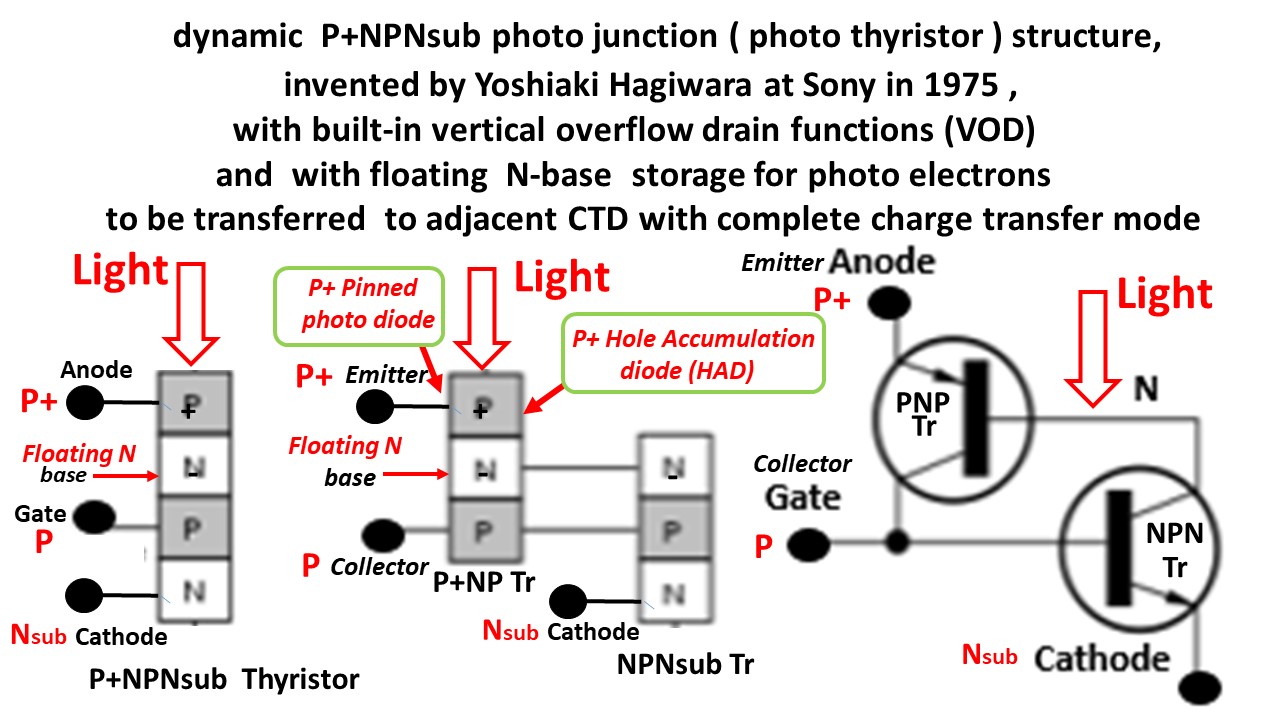

Hagiwara proposed the Pinned Photo Diode with the P+NPNsub junction

(thyrisor) type Light detecting picture cell structure with the vertical

over flow drain for the first time in the world.

Moreoever, Hagiwara proposed in the Japanese patent application example

of figure No.7 of Japanse patent (1975-126747) the Back Light illumination

Pinned Photo Diode type Light Detecting Picture Cell Structure for the

first time in the world.

Moreoever, Hagiwara proposed in the Japanese patent application example

of figure No.4 of Japanse patent (1975-134985) the Schottky Barrier type

Light Detecting Picture Cell structure in the Interline transfer type

CCD image sensor applicaiton for the first time in the world.

**************************************************************************

However last year Hagiwara learned a very surprising news:

**************************************************************

2017 Queen Elizabeth Prize for Engineering Foundation.

**************************************************************

The winners of the 2017 Queen Elizabeth Prize for Engineering Foundation

were :

(1) George E. Smith for the CCD image sensor invention

(2) Michael Tompsett for the CCD image sensor development.

(3) Nobukazu Teranishi for the invention of the pinned photodiode (PPD)

and

(4) Eric Fossum for developing the CMOS image sensor.

**************************************************************

Hagiwara, the true inventor of the Pinned Photo Diode, got really

surprized at the announcement that Teranishi was awarded for the

invention of the pinned photodiode(PPD), and many SONY dilligent

engineers working for the compact digital CMOS image sensors

got really surprized at the announcement that Fossum was awarded

for developing the CMOS image sensor. The truth is that Teranish

did not invent the PPD. Teranish only developped in 1982 the image

lag free interline CCD image sensor with the PPD light detecting

photo sensor structure that was invented by Hagiwara in 1975.

Hagiwara 1975 patents clearly defined the image lag free interline

transfer CCD image sensor as an application example of his 1975

patent claims.

Fossum wrote a paper on "Active Pixel Sensors: Are CCD's

dinosaurs ?" , in Proc. SPIE, Vol.1900, pp.2-14, 1993. However,

the three transistor type active circuit was already invented by

Bill Regitz of Honeywell in 1969. This active pixel sensors was

not Fossum invention. Fossum actually did not develop the

active pixel sensors either. Sony dilligent engineerings did.

Fossum is not the inventor of the active image sensor picture element

at all.

Peter Noble is the true inventor of the active image sensor picture element.

http://www.pjwn.co.uk/

Hitachi MOS Image Sensor Engineers and Intel MOS Process

Engineers all knew that eventually scaled down MOS Process

Technology will conquer all other kinds of Process Technologies

including CCD image sensor technology because of the power

consideration and scaled down dimensional advantage of CMOS

process technology. The three transistor CMOS active picture

cell was already invented as, since the three-transistor circuit

is identical to, the three-transitor circuit of the DRAM cell with

the active source follower type current amplification. Fossum

was just a commentator in his SPIE 1993 paper above. Fossum

was just emphasizing the well understood fact and speculations

that the original image sensor experts all knew in 1970s. This

active pixel sensors was not Fossum invention.Fossum actually

did not develop the active pixel sensors either.

Sony dilligent engineerings developped the active pixel Pinned

Photo Diode type Light detecting photo sensors for compact

digital CMOS image sensors with the Back Light Illumination.

**************************************************************

***********************************************

Queston (1)

Why was the CCD image sensor

the super star in the past ?

***********************************************

Question (2)

Why is the CCD image sensor now obsolete

in the modern digital high vision TV era ?

***********************************************

Question(3)

Why is now the CMOS image sensor dominant

over the CCD image sensor ?

***********************************************

***********************************************

Queston (1)

Why was the CCD image sensor

the super star in the past ?

***********************************************

Answer :

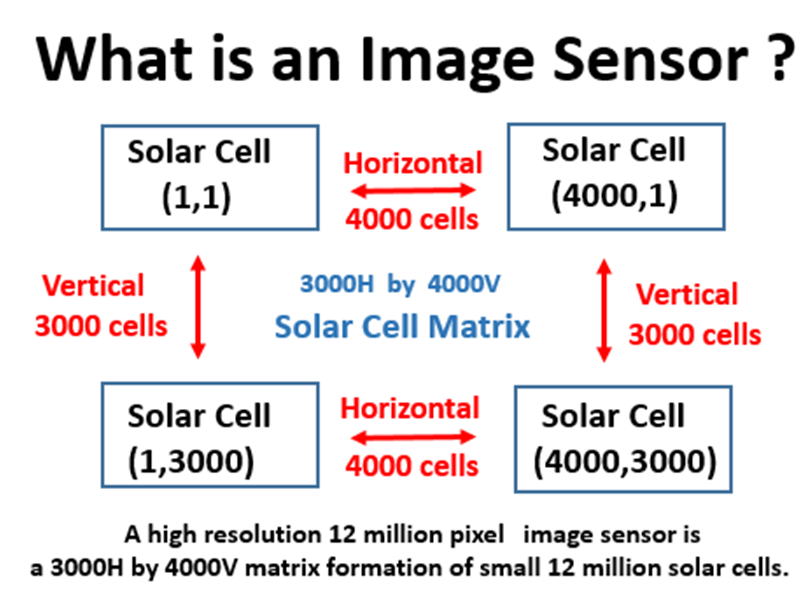

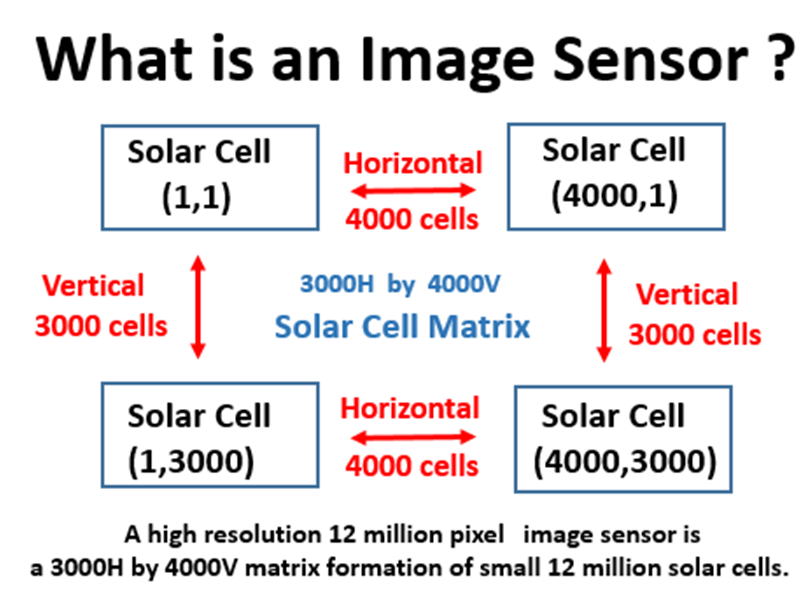

The buried channel type CCD has a very high charge

transfer efficiency of 99.999% with very low CkT noise.

In the past TV system of the 720 H x 512 V picture

resolution, we only needed the total of 1232 charge

transfers at most to transfer the signal charge from

the light detecting storage area ( the pinned photo

diode ) to the final chip output buffer circuits.

Therefore, the incomplete charge transfer of

0.001 % x 1232 charge transfer gives 1.232 % of

the total incomplete charge transfer which means

only the 1.232% of image lag and color picture

contamination, which was tolerable in the past

video camera system.

Besides, CCD image sensor has a very low CkT noise,

which is much lower than that of MOS image sensor.

***********************************************

Queston (2)

Why is the CCD image sensor now obselete

in the modern digital high vision TV era ?

***********************************************

Answer :

The buried channel type CCD has very low CkT noise,

but has only a limited charge transfer efficiency of

99.999%, which is now not good enough.

In the modern high resolution TV system, such as in the

4K TV system of the 3840H×2160V picture resolution,

we need the total of 6000 charge transfers at most to

transfer the signal charge from the light detecting storage

area ( the pinned photo diode ) to the final chip output

buffer circuits.

Therefore, the incomplete charge transfer of

0.001 % x 6000 charge transfer gives 6 % of

the total incomplete charge transfer which

means the 6 % of image lag and color picture

contamination, which was not tolerable at all.

Besides, the CCD image sensor consumes

a lot of electric power compared to the

very low power CMOS image sensor.

***********************************************

***********************************************

Question(3)

Why is now the CMOS image sensor dominant

over the CCD image sensor ?

***********************************************

Answer

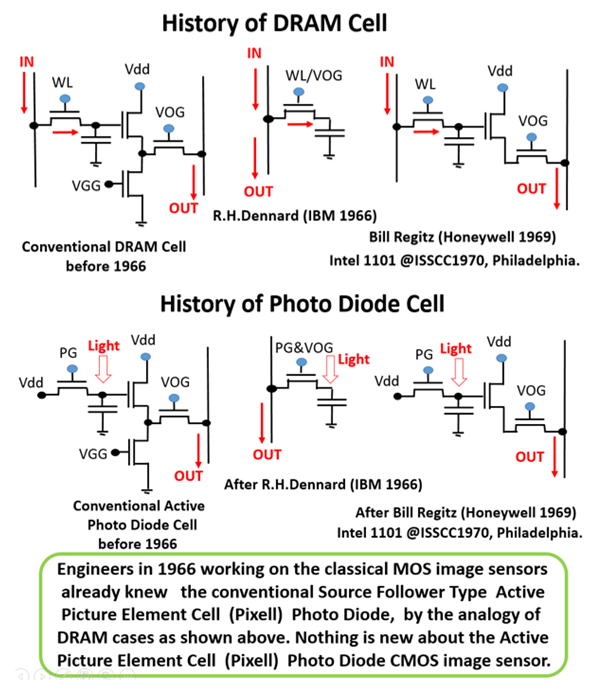

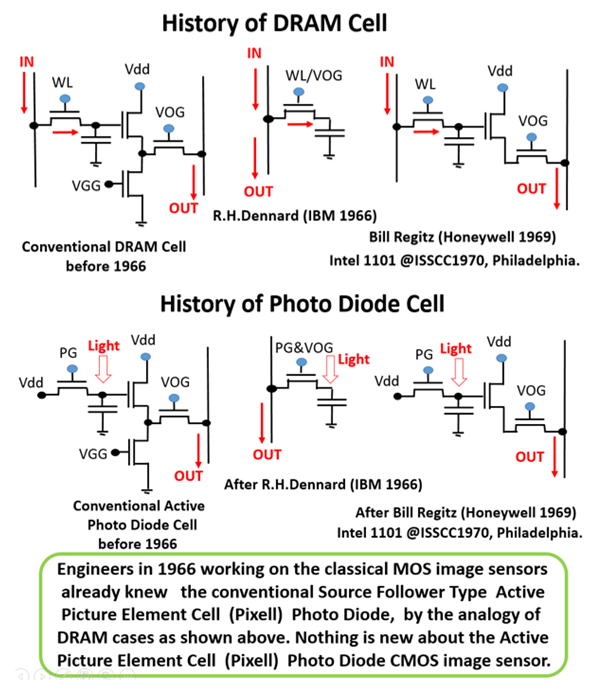

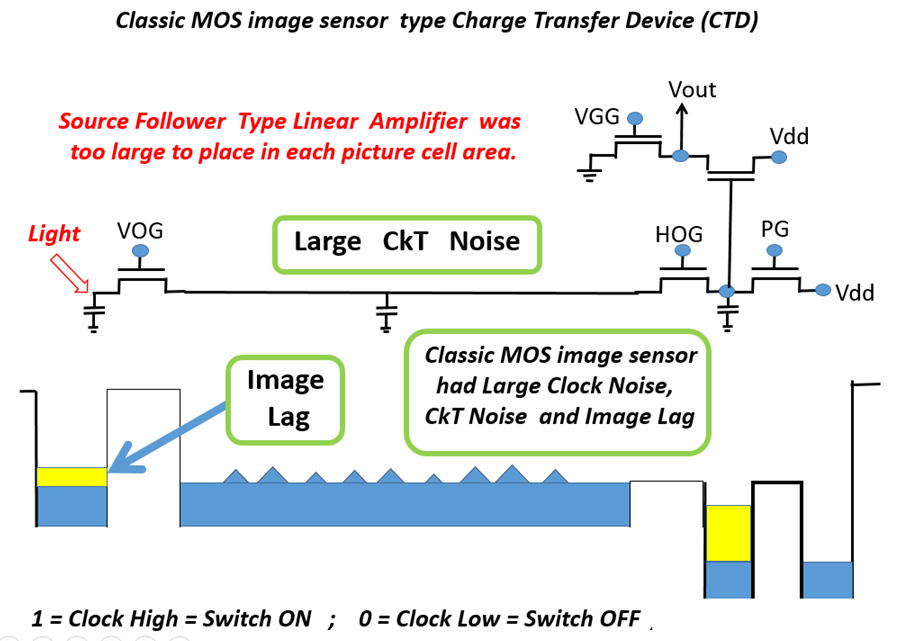

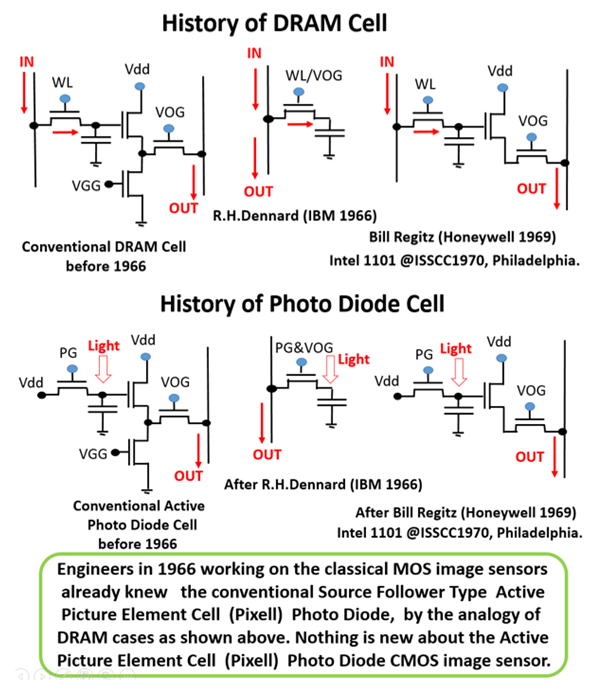

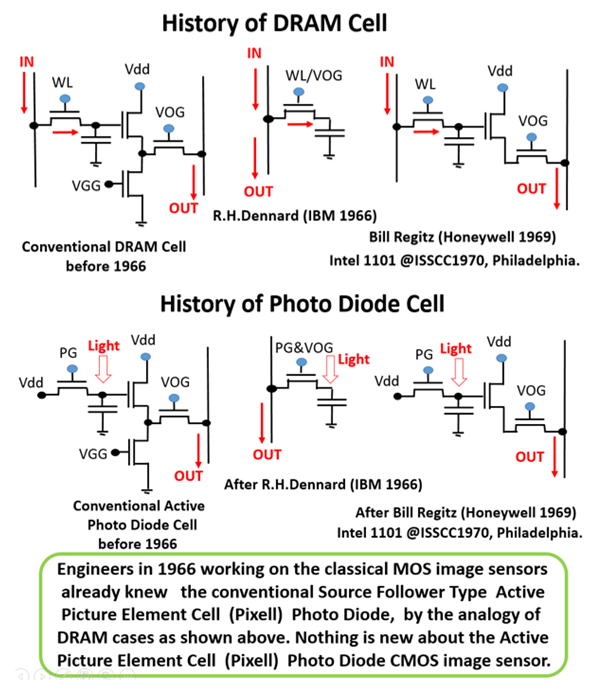

The classical MOS image sensor was one transistor type which

was identical to the one transistor DRAM cell invented by R. H.

Dennard (IBM1966), which did not have any signal preamplifier

circuits, which was proposed by Bill Regits (Honeywell1969).

And this one transistor DRAM cell was connected directly

to the long output signal line of a very large wire capacitance,

which gave a large CkT noise. So the classical MOS image sensor

was not attractive.

DRAM cell and MOS image sensor cell are identical.

The history of the MOS type Image sensor followed closely

the history of the DRAM developments in the past.

As the CMOS process scaling down technology advanced, the wire

capacitance was minimized. And also the MOS transistor size

became so small that the area occupied by the three MOS transistor

type preamplifier circuits, invented by Bill Regits ( Honeywell 1969),

could be placed at each light detecting storage area, namely at each

Pinned Photo Diode type light detecting storage area.

The result is, we no longer suffer the CkT noise because the

preamplifier circuits can convert the small signal charge (voltage)

into a very large signal current、much larger than the CkT noise.

Fossum did not invented the three transitor type active CMOS image sensor.

Bill Regits (Honeywell 1969) invented the three transitor type active CMOS

image sensor. Young engineers and students in MOS image sensors in 1970s

all knew this fact, including myself as a CalTech PhD graduate student

in 1973.

,

DRAM cell and MOS image senser cell are identical.

Many MOS image sensor engineers knew the Rigitz three

transitor DRAM cell that Intel applied for Intel 1101 DRAM

chip in 1970. The active three transistor circuit for the

CMOS image sensor is the same one Rigits invented in 1969.

Fossum did not invent the active CMOS image sensor.

Hagiwara also knew the active MOS image sensor in 1975

as many other MOS image sensor and DRAM engineers did.

*******************************************************************

Teranishi did not invent the Pinned Photo Diode.

Hagiwara invented the Pinned Photo Diode as shown below.

SONY original HAD and Pinned Photo Diode are the same thing,

both invented and defined in the two Japanese Patents

Please visit the oficial Japanese Patent Search Web Site,

https://www4.j-platpat.inpit.go.jp/eng/tokujitsu/tkbs_en/TKBS_EN_GM101_Top.action

to search Hagiwara's original Japanese Patent and put the following two document number,

Document No. ( 1975-134985 ) on the P+NPNsub junction type PPD Patent

Invention

And

Please visit the oficial Japanese Patent Search Web Site,

https://www4.j-platpat.inpit.go.jp/eng/tokujitsu/tkbs_en/TKBS_EN_GM101_Top.action

to search Hagiwara's original Japanese Patent and put the following two document number,

Document No. ( 1975-127647 ) on the NPNN+ junction type PPD Patent Invention

、

Both were filed by Yoshiaki Hagiwara in 1975 at Sony.

See the original Pinned Photo Diode Patent 1975

The picture shown below gives the image of the large CkT noise generated

in

the long and large-capacitance signal output line.

The CkT noise is just the small movements of water molecules when heated.

The small movements of water molecules is just proportional to the ambient

temperature. And the the total movement energy ( CkT noise ) is proportional

to the capacity ( capacitance ) of the container ( pool ) of the water

molecules.

In 1970s, we all knew that we could have a much larger signal output current

if we could place the source follower type preamlifier at each light detecting

picture cell element ( the Pinned Photo Diode ), but we did not do so simply

because the three transistor type source follower preamlifier circuits

was

too large compared to the picture cell light detecting window area. But

now

thans to the drastic scaling down of the MOS transistor dimensions, the

area occupied by the three transistor type source follower preamlifier circuits

became negligible compared to the total area of the picture cell light detecting

window area. Besides, the backlight illumination of the Pinned Photo Diode

which was invented by Hagiwara in 1975 ( see Japanese Patent 1975-127647

)

gave the full backside chip area for the Pinned Photo Diode and the full

frontside chip area for the active preamlifier and ADC circuits for each

light detecting picture cell element ( the Pinned Photo Diode ).

Hagiwara 1975 invention ( Japanese Patent 1975-127647 ) made possible to

place the three transistor source-follower circuit type current preamlifier

at each light detecting picture cell element ( the Pinned Photo Diode ).

The three transistor source-follower circuit type current preamlifier was invented

by Bill Rigits of Honeywell in 1969. Fossum did not invent the three transistor

active current preamplier circuit.

In early 1970s, image sensor engineers all knew this active circuit scheme

could

be applied also for MOS image sensor, but the MOS active circuits occupied

a relatively large area. And placing the MOS active source follower circuits

in each small light detecting picture area was not considered practical since

this would minimize the light detecting window area.

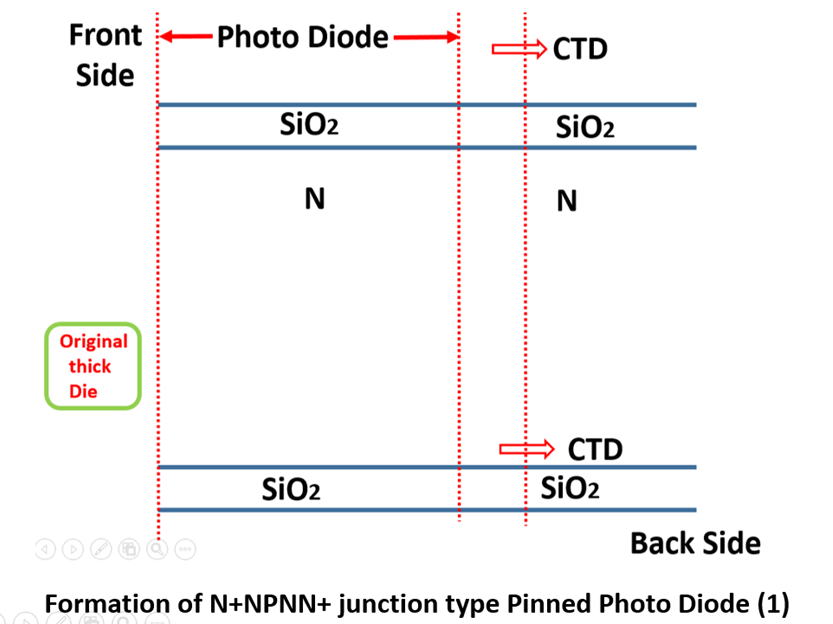

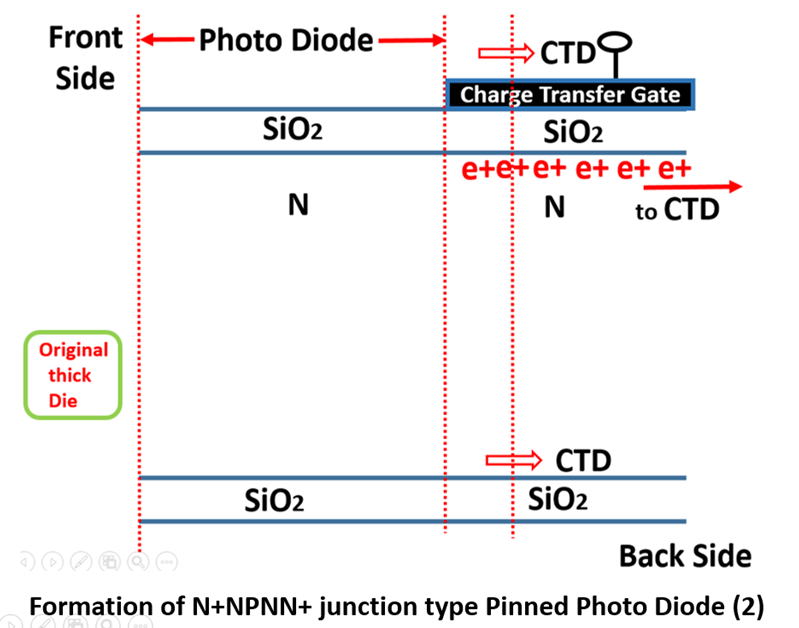

Hagiwara thought that if the back light illumination is possible, one side

of

the wafer can be used fully for light sensing area and the other side of

the

wafer can be fully used for active circuits. This was the motivation of

Hagiwara invention of Japanese Patent ( 1975-127647 ) as shown below.

Fossum did not invented the active CMOS image sensor.

Hagiwara already knew the active CMOS image sensor

in 1975 as many other MOS image sensor engineers did.

They knew they have to wait till MOS process technology

scale down much further. Hagiwara did not want to wait.

So he invented the Back Lihgt illumination Pinned Photo

Diode. See the Japanese Patent (1975-127647) below.

See ElectronicsStackExchangeSite on What is Pinned Photo Diode ?

The following three papers were published much later than Hagiwara

1975 inventions of the Pinned Photo Diode shown above. But these

papers did not quote Hagiwara 1975 patents and publications in 1978.

These three papers are NOT fair.

(1) N. Teranishi et al, " No image lag photo diode structure in the

interline CCD image sensor", IEDM Tech. Dig. pp.113-116, Dec 1982.

(2) P.P.K.Lee et al, "An active pixel sensor fabricated using CMOS/CCD

technology", IEEE Workshop on Charge-Coupled Devices and Advanced

Image Sensors, April 1995.

(3)R.M.Guidash et al, "0.6 um CMOS pinned photo diode color image

Technology, IEDM Tech. Dig. pp.927-927, Dec 1997.

Hagiwara 1975 Patent invention ( JA 1975-134985) was in public in 1977.

And Teranish and his NEC engineers must have seen this Hagiwara Patent

which describes as an patent application example of the interline CCD

image sensor structure with the Pinned Photo Diode as shown in the

Fig. 1 , Fig. 2 and Fig.5 in Hagiwara 1975 Patent ( JA 1975-134985).

SONY was focusing their total efforts to establish device-fabrication and

reliablity technology for the final Interline CCD image sensor productions.

The following three papers were published much later than Hagiwara

1975 inventions of the Pinned Photo Diode shown above. But these

papers did not quote Hagiwara 1975 patents and publications in 1978.

These three papers are NOT fair.

(1) N. Teranishi et al, " No image lag photo diode structure in the

interline CCD image sensor", IEDM Tech. Dig. pp.113-116, Dec 1982.

(2) P.P.K.Lee et al, "An active pixel sensor fabricated using CMOS/CCD

technology", IEEE Workshop on Charge-Coupled Devices and Advanced

Image Sensors, April 1995.

(3)R.M.Guidash et al, "0.6 um CMOS pinned photo diode color image

Technology, IEDM Tech. Dig. pp.927-927, Dec 1997.

When Hagiwara was a CalTech student, CCD was invented in Bell Lab.

CCD is a series of signal charge storage regions under the MOS charge

transfer gates which are placed closely, adjacent to each other. CCD

has a very low wire capacitance induced thermal noise ( CkT ) and has

no clocking noise. And CCD was considered as a super star of the future.

Walter Kosonoky at RCA invented the active source follower type output

circuit for an N-bit CCD analog shift register.

The classical MOS image sensor has only one single charge transfer gate

and the long metal or diffusion analog signal read-out line before the

active

source follower circuit.

In case of the calssical MOS imagers, this long metal or diffusion analog

signal read-out line has a large capacitance which generates the wire

capacitance ( CkT ) oriented thermal noise and also the adjacent clock

wires coupling the signal read-out line generate the clock noise in the

signal read-out line. So, CCD was considered as a super star.

Clearly one bit CCD delay line is also very easily conceivable, which is

just an analog signal charge transfer gate, that is also used as the charge

transfer MOS gate in the classical MOS image senser.

The modern CMOS digital image sensor has the active source-follower

circuit for each pixel. In 1970s, engineers knew these active circuits

could be placed in each pixcel, but the light detecting window area

would be much smaller, resulting in poor light sensitive image sensor.

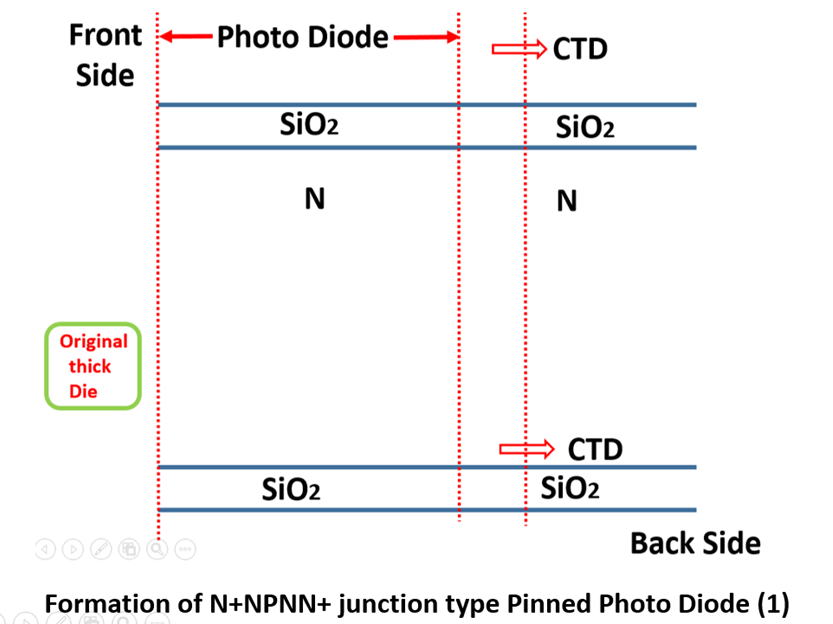

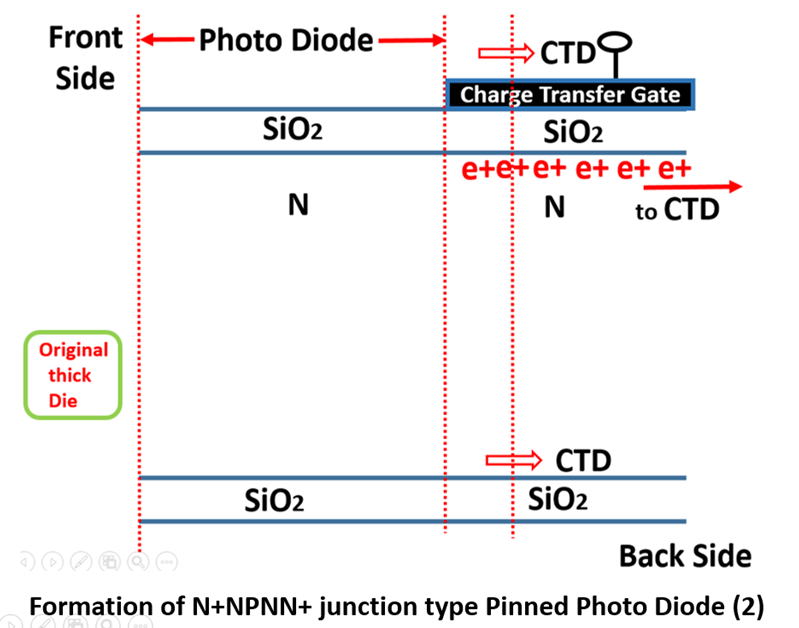

Hagiwara thought that this can be solved if the backside surface of

the silicon chip can be utilized for the light detecting windows so

that the front side of the wafer can be used for other purposes.

The only way to solve this problem was a thinned silicon wafer with

back lihgt illumination. In this way, the bottom surface can be fully

used for photo detecting windows while the top surface can be

implimented with many MOS signal processing circuits including

conventional CCD and/or MOS image sensor circuitries. This was

the original intention of Hagiwara 1975 patent ( JA 1975-127647).

But these three papers did not have any quotations about Hagiwara 1975

inventions of the Pinned Photo Diode. They did not make any reference of

SONY 1978 Press Conferences and Hagiwara Pinned Photo Diode papers

published in the Interenational Solid State Device Conference 1978 in Tokyo

and the international CCD79 conference in Edinburgh, Scotland UK.

These three paper are not fair.

These papers, without any reference to any of

Hagiwara 1975 patents and Hagiwara 1978 and

1979 Pinned Photo Diode paper publications,

were misleading the readers and the world.

*************************************************************************************

http://qeprize.org/winner-2017/

https://en.wikipedia.org/wiki/Queen_Elizabeth_Prize_for_Engineering

*************************************************************************************

On 1 February 2017, it was announced that the 2017 prize would be awarded

to the four engineers responsible for the creation of digital imaging sensors.

The announcement was made by Lord Browne of Madingley at the Royal Academy

of Engineering, in the presence of HRH The Princess Royal.

The winners of the 2017 prize were:

(1) George E. Smith of United States for the invention of the charge-coupled

device (CCD) principle

(2) Michael Tompsett of UK for the development of the CCD image sensor,

including the invention of the imaging semi-conductor circuit and the analogue-to-digital converter

(3) Nobukazu Teranishi of Japan for the invention of the pinned photodiode

(PPD)

(4) Eric Fossum of United States for developing the CMOS image sensor

Together, their innovations allowed for advancements in medical treatments,

science,

personal communications and entertainment.

The winners will receive their award in a ceremony at Buckingham Palace later in 2017.

**************************************************************************************************

******************

Queen Elizabeth of the United Kingdom

and the Emperor of Japan Gave Awards

to WRONG and FAKE PEOPLE ??

******************

Based on the dilligent works of SONY

people, Hagiwara now is going to explain

why Hagiwara believes that Fossum and

Teranishi-san are the WRONG and FAKE

PEOPLE . Yes, they also did good works.

But they are liars and crooks. They are

politically-working dishonest people, now

governing honest image sensor community.

******************

******************

How could Teranishi-san at NEC be the

inventor of the Pinned Photo Diode ?

******************

Hagiwara invented the Pinned Photo Diode

in 1975, and SONY intorduced to the world

the highly light sensitive Pinned Photo Diode

in the FT CCD image sensor in Tokyo by

SONY President Iwama Kazuo and in New

York by SONY chairman at the same time

in 1978.

Then, Hagiwara was invited in the CCD79

international conference in Edinburgh, UK

for his contributions to the image sensor

community. SONY was focusing their total

efforts for mass production and reliability

technology for image sensors. SONY was

the only company working seriously for the

consumer video cameras using the poor light

sensitive CCD image sensors. Everyone at

that time already gave up of using the poor

CCD image sensors.

But Hagiwara 1975 inventions on the Pinned

Photo Diode SAVED CCD image sensors for

consumer video camera applications.

Unfortunately, the world then made a serious

misunderstanding about CCD image sensors.

The world believed then and even now believes

that the CCD image sensor was the one with

the super light sensitive features.

But the truth is that the Pinned Photo Diode

was and still is the one with the very important

features of High Photo Sentitivity and Low Dark

Current.

As well understood, CCD is an analog signal

shift registger with many charge transfering

metal electrodes, placed adjacent to each

other in series forming a line. CCD has the

metal electrodes inherently which does not

pass light. So the simple logical observation

would conclude that CCD cannot be a highly

sensitive light detecting device. But the

world now forgot completely this simple truth.

The truth is that the Pinned Photo Diode itself

was and still is the one with the very important

features of High Photo Sentitivity and Low Dark

Current.

The world did not know the truth behind the

SONY 1978 Press Conference, introducing

the Super light sensitive CCD image sensor

video camera with very low dark current and

with no trap-noise.

The poor CCD-type light detecting MOS

capacitor structures do not have these two

imprtant features of High Light sensitivity and

LOW DARK current.

Hagiwara 1975 inventions give these important

features. This invention on the Pinned Photo

Diode was and still is the one with the super

light sensitive structure, that is, the super light

detecting photo diode structure, the Pinned

Photo Diode with very low dark current.

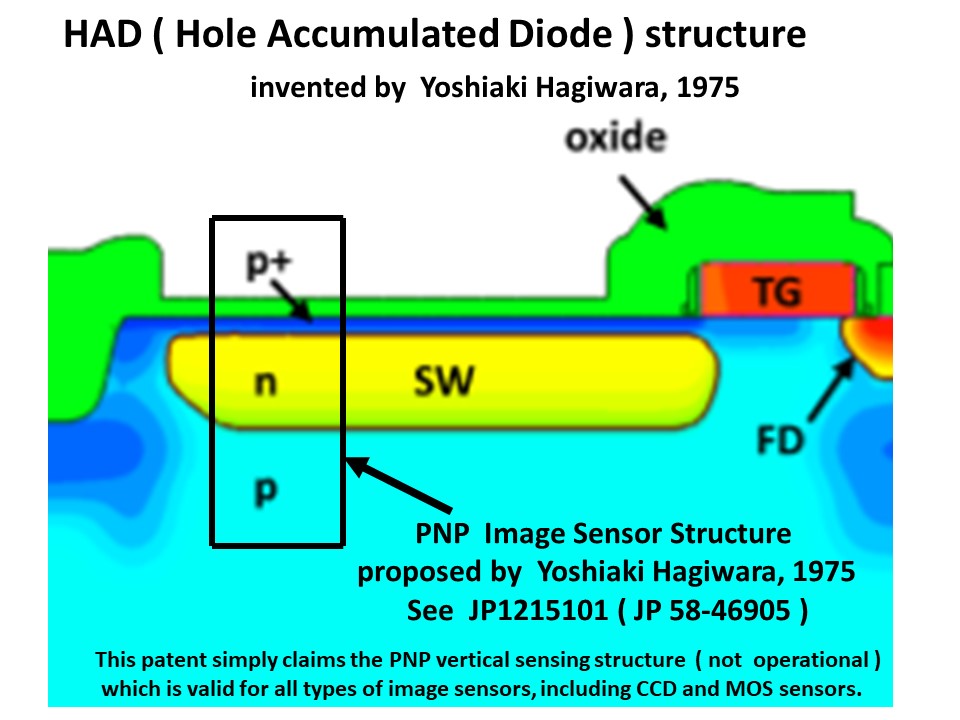

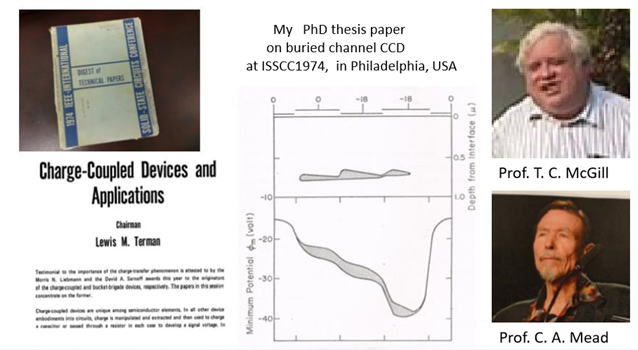

The P+ ( Hole Accumulatio ) top layer has

the stable fixed ( Pinned ) voltage, quenching

Silicon-SiO2 interface trappig noise and the

surface-recombination-center induced dark

current.

These device physics effects are explained

in details in the Hagiwara 1975 PhD thesis

which was written by Hagiwara as a CalTech

graduate student with the guidance of Prof.

C.A.Mead, Prof.T.C.McGill and Prof.James

McCaldin in Gordon Moore Lab at CalTech,

Pasadena California, USA in 1972 to 1975.

******************

See the two basic Japanese patents Hagiwara

filed at SONY ( JA 1975-127647 ) for the

NPNN+ junction type Pinned Photo Diode with

thinned silicon BACK LIGHT illumination and

( JA-134985 ) for the P+N-PNsub junction

(thyristor) type Pinned Photo Diode with

the vertical overflow drain (VOD) function mode

as shown below.

******************

How could Fossumu be the developper of

the modern CMOS digital image sensor ?

******************

Based on the dilligent works of SONY

people, Hagiwara now is going to explain

why Hagiwara believes that Fossum and

Teranishi-san are the WRONG and FAKE

PEOPLE . They are liars and crooks. They

are politically-working dishonest people

now governing the image sensor comunity.

Fossum did not know the basic patent

on the Back Light illuminated Pinned

Photo Diode ( JA 1975-127647 ) which

is the basic light detection structure of

the modern CMOS digital image sensor

with Back Light Illumination. Hagiwara

at SONY invented this structure at SONY.

Fossum did not develop any built-in A/D

converters which is needed INSIDE of the

CMOS digital image sensor chips. Asano,

Yamada and Fukushima did the pioneering

works in SONY. Their dilligent works at

SONY made SONY possible to introduce

the compact CMOS digital image sensor on

the market for the first time in the world.

The Snap Shot digital circuits needed in

CMOS image sensors was developped by

Pain and his coworkers in JPL ,CalTech.

Active circuits in CMOS image sensors

were developpped by Phyllips people.

Fossum did not develop any Fast Cache

SRAM needed for digital camera systems

for quick digital image data aquisition.

The pioneering Fast Cache SRAM works for

the real time digital TV broadcast systems

were developed by Miyaji and Hagiwara in

SONY in 1989 . Later this technique helped

to realize the SONY compact digital camera.

Fossum did not do anything to develop any

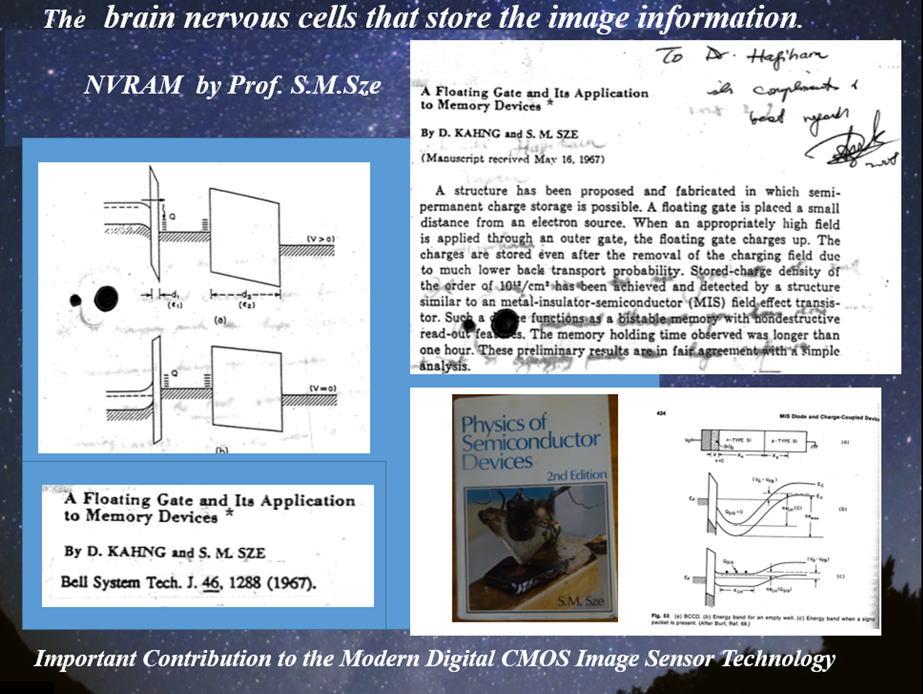

nonvolatile memory chip, NVRAM chips with

the floating gate MOS memory device, which

was invented by Prof. S. Sze and his coworker

in Bell Lab and later developped in the form

of the NAND Flash memory at Toshiba by

Prof. Tonooka in Tohoku University.

With all of these technologies, SONY young

engineers developped for the first time in

the world the thinned wafer BACK LIGHT

illumination CMOS digital image sensor with

the SONY original HAD sensor, which is the

same thing as the one the world is calling

commonly as the Pinned Photo Diode now.

This Pinned Photo Diode with BACK LIGHT

illumination is the very invention of Hagiwara

as shown below.

******************

**********************************************************************

In June 2018, Hagiwara was not very happy

when Hagiwara learned that Teranishi-san ( ex-NEC )

was awarded with Queen Elizabeth Award 2017

as the inventor of Pinned Photo Diode, which was

based on his 1982 IEDM paper on the Buried Photo Diode

in the Interline Transfer CCD image with no image lag.

The decison was obvioously made by the 2014 Fossum Fake Paper

that made also the world to belive that Fossum was the developer

of the Modern CMOS digital camera. The truth is that SONY young

dilligent silent engineers worked hard to realize the Modern Highly

l

Light sensitive and LOW DARK CURRENT CMOS digital Camera

with BACK LIGHT illumination.... NOT FOSSUM ... NOT Teranish ....

Hagiwara is not very happy.

The world has the right to know what is the truth.

******************************************************************

http://qeprize.org/winner-2017/

https://en.wikipedia.org/wiki/Queen_Elizabeth_Prize_for_Engineering

******************************************************************

On 1 February 2017, it was announced that the 2017 prize would be awarded

to the four engineers responsible for the creation of digital imaging sensors.

The announcement was made by Lord Browne of Madingley at the Royal Academy

of Engineering, in the presence of HRH The Princess Royal.

The winners of the 2017 prize were:

(1) George E. Smith of United States for the invention of the charge-coupled

device (CCD) principle

(2) Michael Tompsett of UK for the development of the CCD image sensor,

including the invention of the imaging semi-conductor circuit and the analogue-to-digital converter

(3) Nobukazu Teranishi of Japan for the invention of the pinned photodiode

(PPD)

(4) Eric Fossum of United States for developing the CMOS image sensor

Together, their innovations allowed for advancements in medical treatments,

science,

personal communications and entertainment.

The winners will receive their award in a ceremony at Buckingham Palace later in 2017.

******************************************************************************

However, from the evidence shown below, it is clear that Hagiwara is the

true inventor

of Pinned Photo Diode. Hagiwara is not very happy now by the bad news above.

************************************************************

Fossum 2014 Fake Paper

************************************************************

It all started from the Fossum 2014 fake paper on Origin of Pinned Photo Diode.

************************************************************

Prof. Albert Theuwissen said that Fossum 2014 paper is doutful.

Prof. Akira Matsuzawa said that Fossum 2014 paper is fake.

Prof. Shingo Kagami said that SONY HAD ( which was invented by

Hagiwara in 1975 ) and the Pinned Photo Diode are the same thing.

The details of Hagiwara 1975 patents prove that Fossum is a big liar,

telling a big lie on the origin of Pinned Photo Diode.

Fossum said in his 2014 fake paper that Hagiwara 1975 Patent

invention did not describe any charge transfer operations,

which is a very, very big lie , deceiving the entire world,

including Queen Elizabeth of United Kingdom and also

the Emperor of Japan !!!!!!

The following two patents filed by Hagiwara at SONY

in 1975 clears shows that the two Hagiwara Patents

clearly define the Pinned Photo Diode structure with

the complete charge transfer operation mode.

*****************************************************

Fundementals and Brief History of Solid State Image Sensors

*****************************************************

(1) What is CCD ?

A charge-coupled device (CCD) is a device for the movement of electrical charge,

usually from within the device to an area where the charge can be manipulated,

for example conversion into a digital value.

CCD is a simple structure of many MOS type charge transfer electrodes,

next to each other in series, placed on the oxide semiconductor surface.

These MOS type capacitors of CCD are biased above the threshold

for inversion when image acquisition begins, allowing the conversion

of incoming photons into electron charges at the semiconductor-oxide interface

in case of the original surface type CCD invention in 1969.

See https://en.wikipedia.org/wiki/Charge-coupled_device

(2) What are the two important functions of CCD ?

In the CCD image sensor pixels for light detection are represented

by metal-oxide-semiconductors (MOS) capacitors. The CCD is then

also used to read out out these charges as an analog shift register.

CCD moves signal charge between capacitive bins in the device,

with the shift allowing for the transfer of charge between bins.

CCD works as a photo detection structure and also as an analog shift register.

This is achieved by "shifting" the analog signal packets between stages within

the device one at a time. Charge Coupled Device is an analog shift register.

Charge Coupled Device works as an analog signal packet transmission line.

(3) What is wrong with the original surface channel type CCD ?

The original surface channel type CCD had two problems.

One of the two problems is the poor charge transfer efficency of 99.9 %.

However, the original surface channel type CCD invented in 1969 have only 99.9 %

of charge transfer efficiency. It means that, after less than 1000 times of charge

transfer shift-operations, the original analog signal charge is degraded completely.

There the surface type CCD had no practical value. Intel and other companys

gave up of using CCD as digital memory device due to this poor charge transfer

efficiency and also due to the large power needed to clock the large MOS capacitors

of the charge transfering metal gates of the CCD analog shift register.

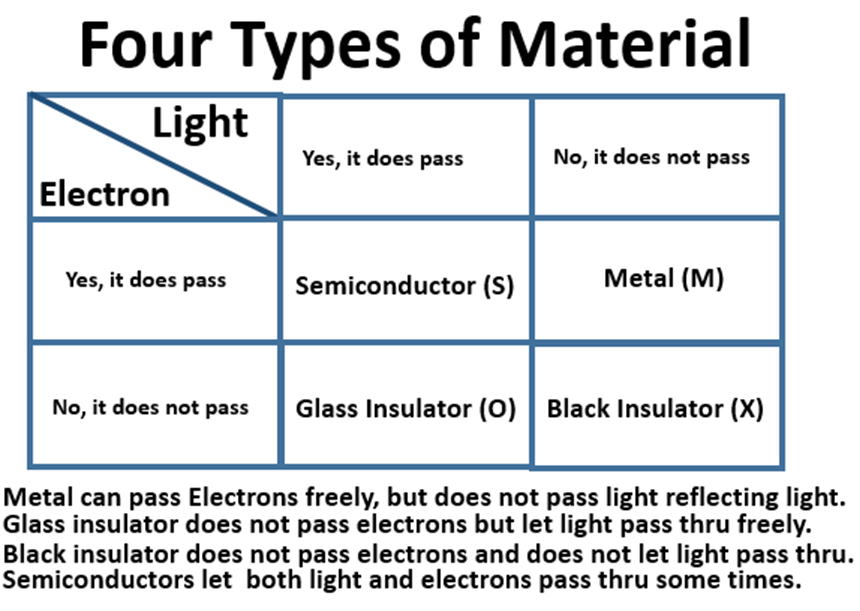

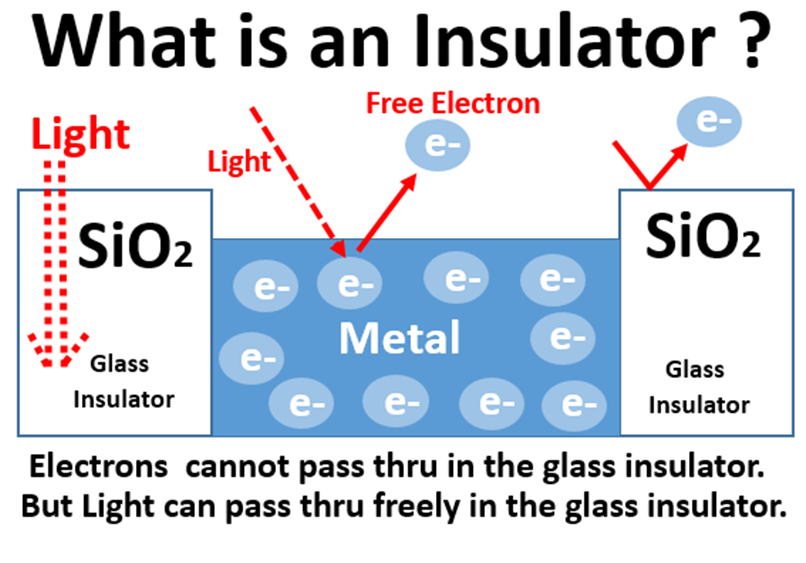

The other one of the two problems is the poor blue light sensitivity.

Beside the poor charge transfer efficiency of 99.9 %, because CCD is made of a series

of dynamic charge tansfer MOS gates. The metal electrode does not pass the light

efficently. The meal reflects light like a mirror.

Inherently CCD is not really a good light sensitive detector. CCD has a very poor light

detection capability, specially in the blue and ultra violet lights of short wave length.

Hagiwara working at SONY in 1975 had many video camera engineers. They did not

like CCD video cameras because of the poor color reproduction problem. They liked

the classical MOS image sensor camera of the N+P type photo diode instead of the

CCD type MOS capacitor photo detecting structure. Hitachi and other companys

did not like CCD image sensor cameras and they were focused on developping

the classical video camera of N+P type photo diode type light detecting structure.

(4) What is the buried channel type CCD ?

However, the buried channel type CCD invented in 1971 have 99.999% of

charge transfer efficiency. It means that, even after 1000 times of charge

transfer shift-operations, the 99% of the original analog signal charge is

saved. This analog buried channel type CCD shift register of 99.999% charge

trasfer efficincy worked fairly well for the past NTSC TV picture applications

in the past century.

See https://patents.google.com/patent/US3792322A/en

See https://patentimages.storage.googleapis.com/90/6e/28/e1f0a9b89d5110/US3792322.pdf

(5) What is wrong with the buried channel CCD ?

The buried channel CCD was working well for the NTSC TV picture resolution

cameras in the past. But now the high resolution digital TV era came and we

have now 4K and more high resolution pictures. If we use this CCD analog shift

register of only 99.999% charge transfer, since we need to transfer charge packets

more than 7000 charge transfer operations, that is, since "4000H + 3000V" means

7000 charge transfers, we lose now 7 % of the original signal charge at the end of

the 7000 bit CCD analog shift register of only 99.999% charge transfer efficiency.

And the reproduced image quality would be very poor.

Besides, the large power needed to clock the large MOS capacitors of the charge

transfering metal gates of the CCD analog shift register is no longer welcomed.

So CCD was a short-lived and we don't need this technology any longer.

The scaling of CMOS process technology tend encouraged and helped very much

the many delligent digital circuit engineers of CMOS image sensor applications.

The total CMOS digital circuit technology now, including the light-detecting Pinned

Photo Diode ( invented by Hagiwara at SONY) , one charge transfer gate of conventional

MOS switching electrode, fast A/D converter digital circuit technology ( developped by

Yamada and Asano at SONY ) , digital data transmission line , fast Cache SRAM of dynamic

floating read-out bit line technolgy ( invented Miyaji and Hagiwara at SONY ) and slow

NVRAM of the floating gate technolgy ( invented by Prof.S.Sze ) all together as a big digital

circuit system technology, finally replaced the Giant Super Star the CCD, the analog shift

register techology.

Beside the poor charge transfer efficiency of 99.9 %, because CCD is made of a series

of dynamic charge tansfer MOS gates. The metal electrode does not pass the light

efficently. The meal reflects light like a mirror.

Inherently CCD is not really a good light sensitive detector. CCD has a very poor light

detection capability, specially in the blue and ultra violet lights of short wave length.

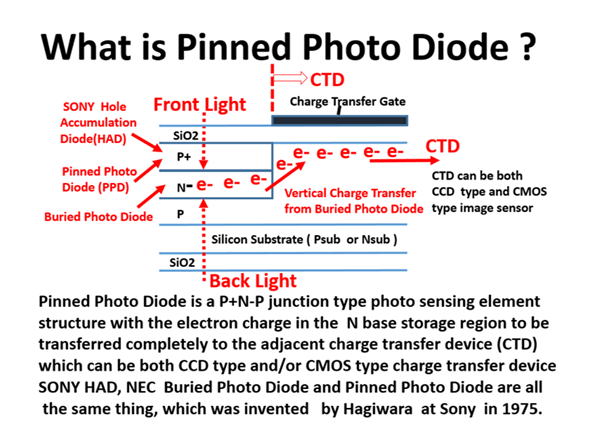

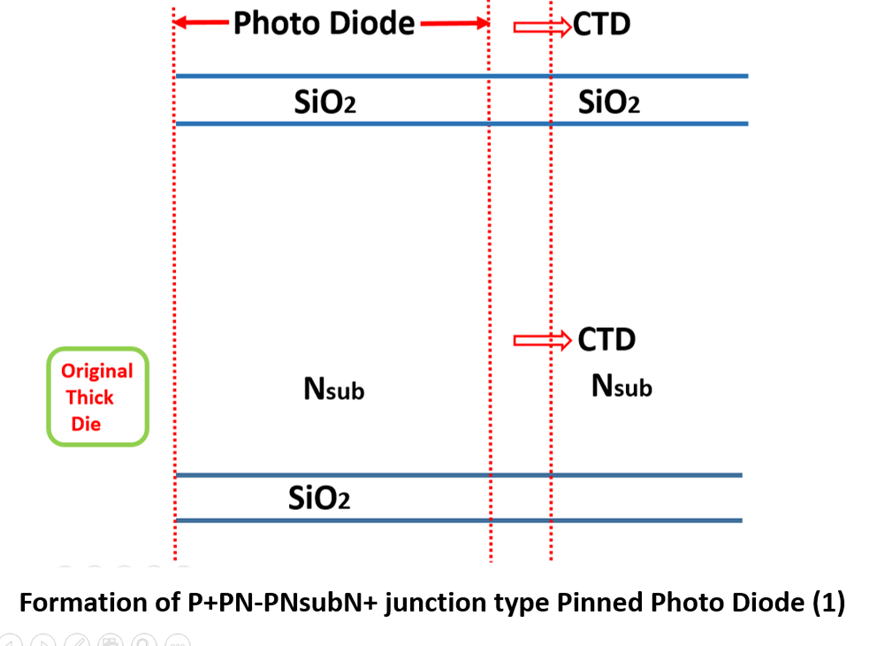

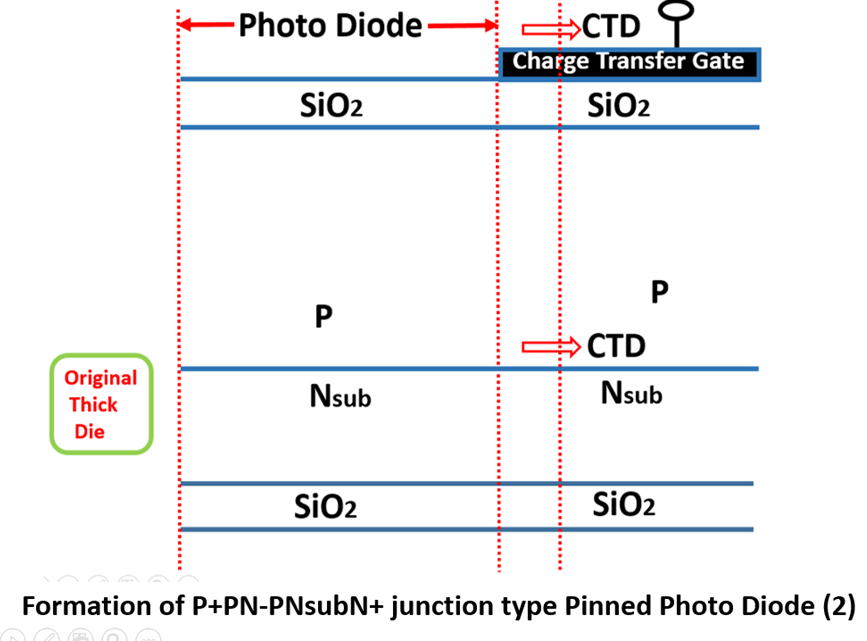

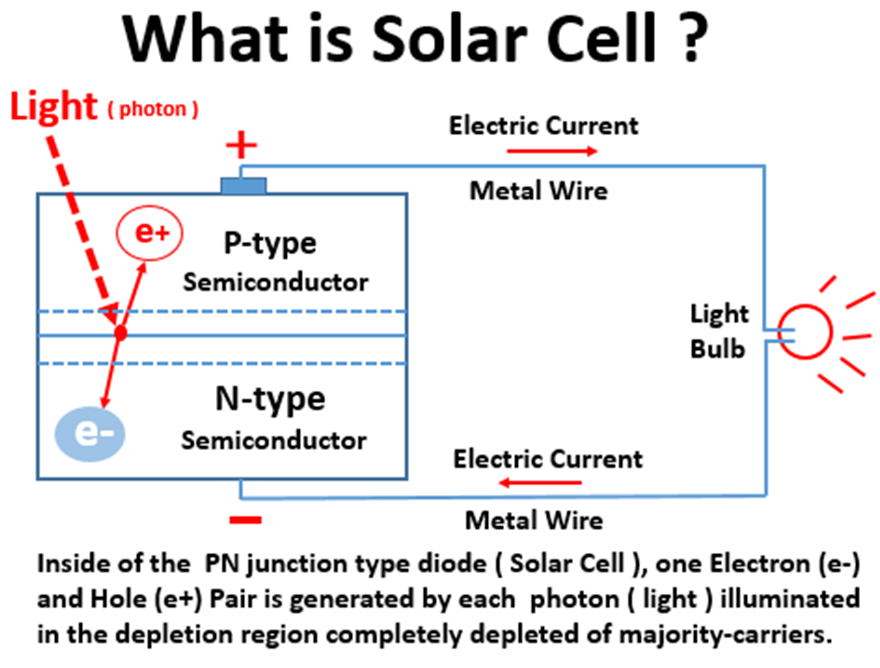

(6) What replaced the CCD-type MOS capacitance photo detecting structure ?

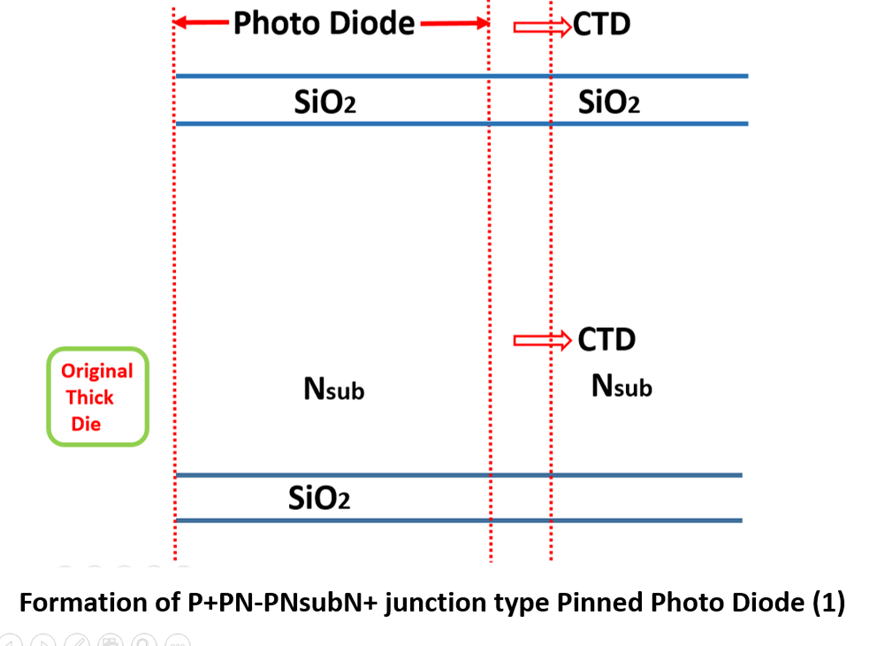

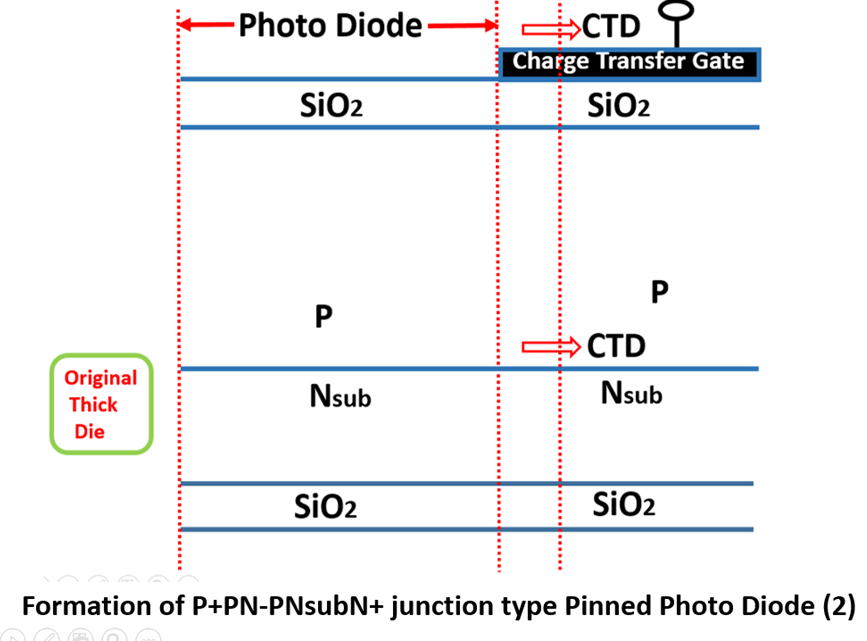

In 1975 Hagiwara replaced the CCD-type MOS capacitance photo detecting structure

with the light detecting structure of the P+N-PNsub junction ( PNP transitor in

N-type substrate ) type , which is now called a Pinned Photo Diode.

He filed two Japanese patents, one for the P+N-PNsub junction type Pinned

Photo Diode with the vertical overflow drain (VOD) function ( JA 1975-134985 )

and the other one for the NPNN+ junction type Pinned Photo Diode with the

thinned silicon die with back light illuminati ( JA 1975-127647 ) which is now

the basic light detection structure of the modern digital CMOS image sensor.

Hagiwara studied the buried channel CCD in his PhD work in CalTech. Hagiwara

understood both the strong and the weak points of the buried channel CCD.

Hagiwara gave up of using CCD as the light detecting structure. Instead Hagiwara

focused to use the N+P photo diode for the light detecting structure.

Hagiwara was trained in SONY bipolar fabrication lines at Sony Atsugi Technoogy

Center in Japan in 1971 and 1972. And Hagiwara understood very well the P+NP

transisitor structures and reliability problems such as the P+NPNsub thyristor

puch-thru operation mode of the P+NP transitor formed in the N-type substrate

Nsub die.

He filed two Japanese patents, one for the P+N-PNsub junction type Pinned

Photo Diode with the vertical overflow drain (VOD) function ( JA 1975-134985 )

and the other one for the NPNN+ junction type Pinned Photo Diode with the

thinned silicon die with back light illuminati ( JA 1975-127647 ) which is now

the basic light detection structure of the modern digital CMOS image sensor.

The CCD-type MOS capacitance photo detecting structure is now replaced by

the Pinned Photo Diode invented by Yoshiaki Hagiwara at Sony in 1975.

The world did not know the truth.

The truth is that, CCD is not a very good light detecting structure,

The MOS-capacitance type CCD light detector has a very poor light

seisitivity and also has very bad trap noise and dark current at the

Oxide-Semiconductore inteface.

On the other hand, the P+NPNsub junction ( thyristor ) type light

detecting structure ( JA 1975-134985 ) invented by Hagiwara in SONY

in 1975 is a very good light detecting structure with very low trap noise

and dark current because the the Oxide-Semiconductore inteface states

are all quenched by the Hole Accumuation P+ region which is pinned at

stable voltage value. This is the reason why SONY called it as the SONY

original HAD sensor, and why the world called it as the Pinned Photo Diode.

The Pinned Photo Diode, invented by Hagiwara in 1975, replaced the

CCD-type MOS capacitance photo detecting structure. SONY annouced

in Tokyo by SONY President Kazuo Iwama and at the same time in New

York by SONY Chairman Akio Kazuo to the public widely in the world

SONY new video camera with excellent light detection capability and

with the very low trap and dark current features of high quality pictures.

These good features were owing to the Hagigiwara's new invention on

the P+NPNsub junction photo diode ( now called Pinned Photo Diode),

but the world misunderstood that CCD image sensor was so. But the

truth is that, CCD image senor was not. Hagiwara Photo Diode was !

In 1975 Hagiwara replaced the CCD-type MOS capacitance photo detecting

structure with the new light detecting structure of the P+N-PNsub junction

( PNP transistor structure in N-type substrate ) type light detecting photo

diode structure , which is now called a Pinned Photo Diode

So, the orignal CCD was expected to perform two important functins of

the light detction and the analog data transmission line.

In recent years CCD has become a major technology for digital imaging.

But the truth is that, CCD was saved by Hagiwara 1975 invention introduing

to the world a new light detecting photo diode structure in the SONY 1978

Press Conference in Tokyo and New York.

Although CCDs are not the only technology to allow for light detection,

CCD image sensors are widely used in professional, medical, and

scientific applications where high-quality image data are required

because the Hagiwara 1975 invention of the Pinned Photo Diode was

always in the behind back curtain helping CCD image sensors.

But the world did not know that CCD works only as an anlalog data

transimission line. The light detecting photo diode structure invented

by Hagiwara in 1975 gives the features of professional, medical, and

scientific applications where high-quality image data are required.

In applications with less exacting quality demands,

such as consumer and professional digital cameras,

the light detecting photo diode structure invented

by Hagiwara in 1975 was also used as active pixel sensors.

The world thought CCD is the one giving all the imortant

features of of professional, medical, and scientific applications

where high-quality image data. But the true hero was behind

the curtain. CCD was on the stage. Hagwara 1975 invention

helped CCD on the stage. Now CMOS digital circuit technology

took over the CCD analog technology, and CMOS image sensor

is now on the world stage. But still Hagiwara 1975 invention

behind the back curtain was helping CMOS digital image

sensor on stage. Hagiwara 1975 invention was alwasys helping

image sensors on the high lighted stage in the world.

Now Hagiwara, at age 70, should be happier if the world knew that

the Pinned Photo Diode was acturally invented by Hagiwara in 1975

when Hagiwara was just 26 years old, a young dreaming SONY engineer.

************************************

Hagiwara invented Pinned Photo Diode in 1975

Hagiwara developped Digiltal CCD and CMOS Image Sensors

Hagiwara Patent Pictures on Pinned Photo Diode

https://patents.justia.com/inventor/yoshiaki-hagiwara

************************************

Queen Elizabeth of the United Kingdom

and the Emperor of Japan Gave Awards

to WRONG and FAKE PEOPLE ??.

*************************************************************************************

In June 2018, Hagiwara was not very happy

when Hagiwara learned that Teranishi-san ( ex-NEC )

was awarded with Queen Elizabeth Award 2017

as the inventor of Pinned Photo Diode, which was

based on his 1982 IEDM paper on the Buried Photo Diode

in the Interline Transfer CCD image with no image lag.

The decison was obvioously made by the 2014 Fossum Fake Paper

that made also the world to belive that Fossum was the developer

of the Modern CMOS digital camera. The truth is that SONY young

dilligent silent engineers worked hard to realize the Modern Highly

l

Light sensitive and LOW DARK CURRENT CMOS digital Camera

with BACK LIGHT illumination.... NOT FOSSUM ... NOT Teranish ....

Hagiwara is not very happy.

The world has the right to know what is the truth.

*************************************************************************************

http://qeprize.org/winner-2017/

https://en.wikipedia.org/wiki/Queen_Elizabeth_Prize_for_Engineering

*************************************************************************************

On 1 February 2017, it was announced that the 2017 prize would be awarded

to the four engineers responsible for the creation of digital imaging sensors.

The announcement was made by Lord Browne of Madingley at the Royal Academy

of Engineering, in the presence of HRH The Princess Royal.

The winners of the 2017 prize were:

(1) George E. Smith of United States for the invention of the charge-coupled

device (CCD) principle

(2) Michael Tompsett of UK for the development of the CCD image sensor,

including the invention of the imaging semi-conductor circuit and the analogue-to-digital converter

(3) Nobukazu Teranishi of Japan for the invention of the pinned photodiode

(PPD)

(4) Eric Fossum of United States for developing the CMOS image sensor

Together, their innovations allowed for advancements in medical treatments,

science,

personal communications and entertainment.

The winners will receive their award in a ceremony at Buckingham Palace later in 2017.

**************************************************************************************************

However, from the evidence shown below, it is clear that Hagiwara is the

true inventor

of Pinned Photo Diode. Hagiwara is not very happy now by the bad news above.

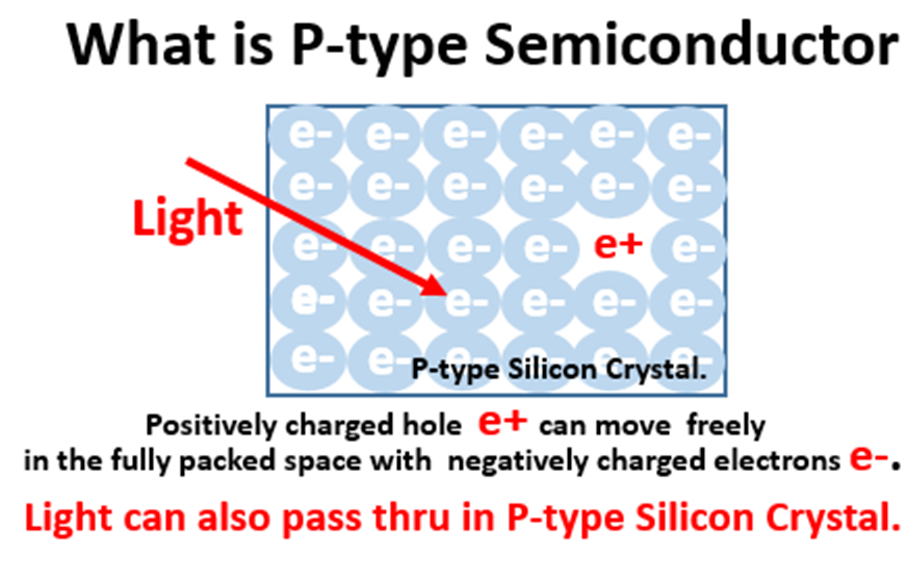

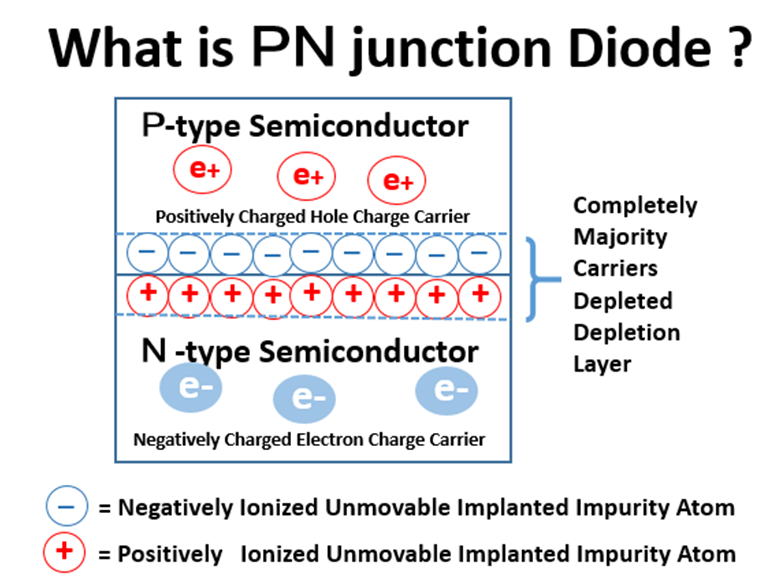

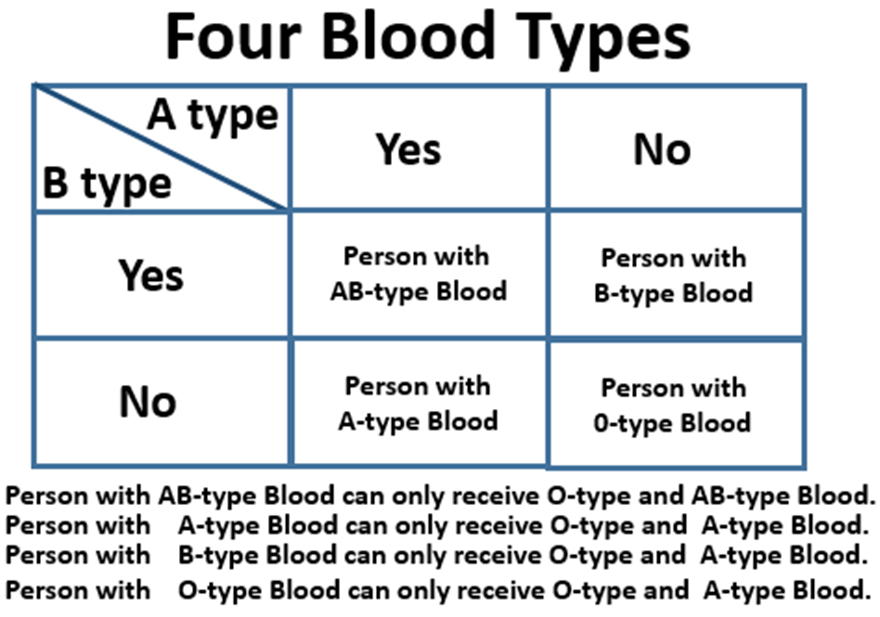

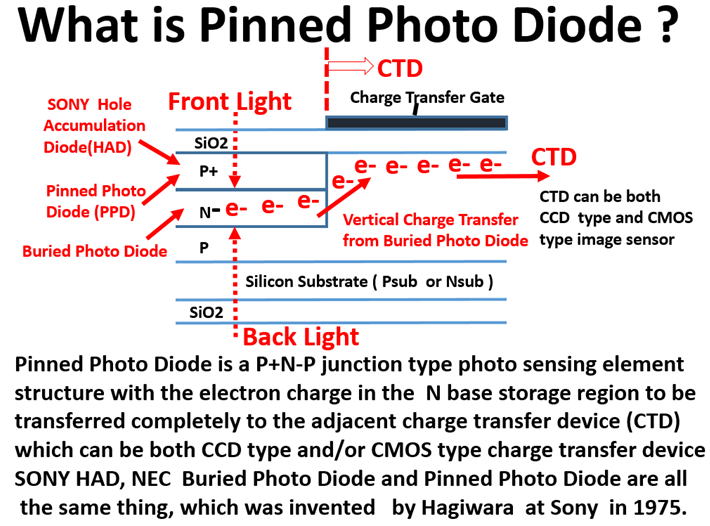

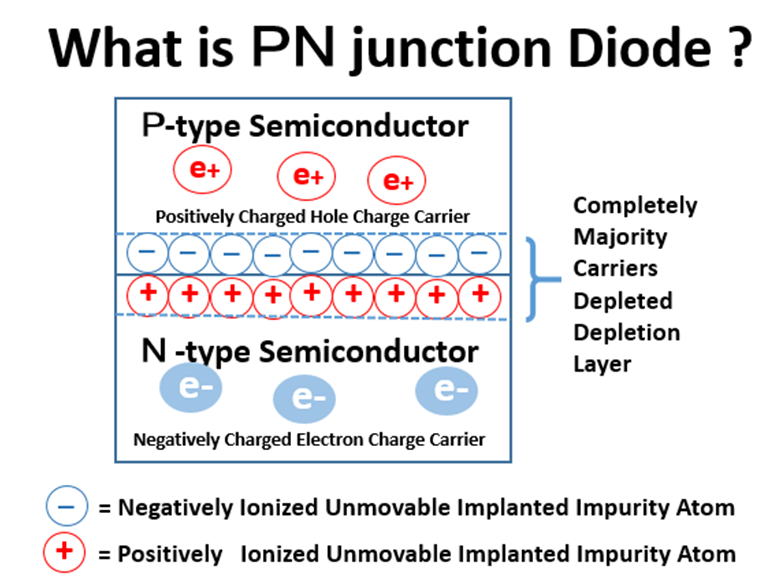

In the most simplest form of a Pinned Photo Diode is P+NP junction ( transistor ) type

photo diode with the emitter P+ region and the collector P region is connected (pinned)

to a stable fixed ( pinned ) voltage.

The base N region is shallowly doped, which is enabling the complete majority-carriers

charge-transfer, resulting an empty potential well of the completely majority-carrier

depletion mode in the base N storage region.

The signal majority carriers are completely transferred to an adjacent Charge Transfer

Device (CTD) which can be a classical simple NMOS type, a FT CCD type, an ILT CCD

type and the modern CMOS type active Charge Transfer Devices (CTDs).

In 1978, SONY announced a CCD image sensor video camera with this highly light sensitive

and very low dark current P+NP junction type Pinned Photo Diode in Tokyo by SONY

President Kazuo Iwama and in New York by Sony Chairman Akio Morita at the same time.

The world misunderstood that the CCD image sensor is highly light sensitive and of very

low dark current. But the truth is, the P+NP type Pinned Photo Diode sensor which was

invented by Hagiwara in 1975 was highly light sensitive and of very Low dark current.

The surface type CCD had only 99.9 Charge Transfer Efficiency and was no use for the

Consumer Video Camera applications. But the buried channel type CCD had 99.999%

Charge Transfer Efficiency which was good enough for NTSC TV picture quality.

But CCD is not enough for the modern High Resolution Digital TV.

CCD is an analog shift register, which is a kind of an analog signal transmission line.

The analog technolgy is all now to be replaced by the new modern digital technology.

We now use a digital shift register with A/D converter CMOS digital circuits,

which is a kind of a digital signal transimission line.

So CCD was a short-lived analog technology. We do not need CCD any more.

Now we have CMOS type Charge Transfer Device which is a digital data transmission line.

All of this became possible owing to the advance of scaling down of CMOS fabrication

technology which minituarized the CMOS gate electrode size, the wiring meal line

dimensions, the metal contact size and the size of diffusion area and depth. All of them

now contibute for minimizing the CkT noise and Clock noise in CMOS image sensors.

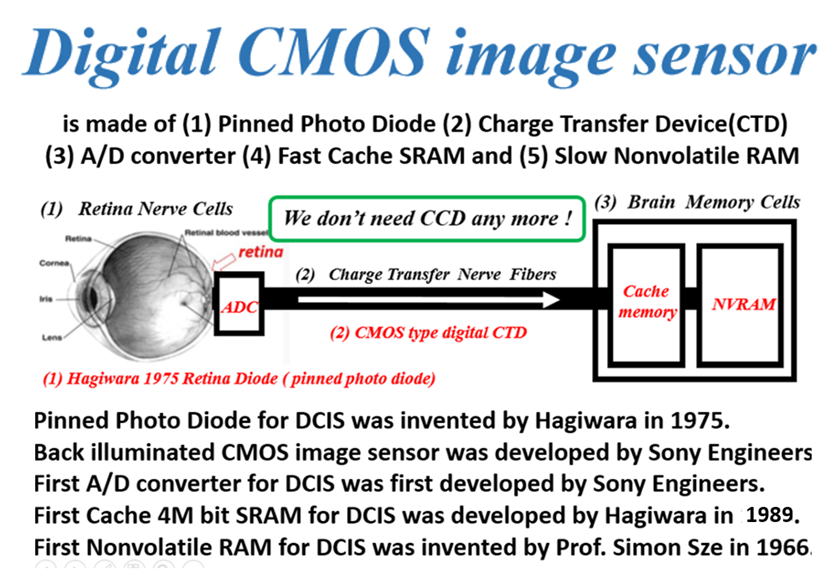

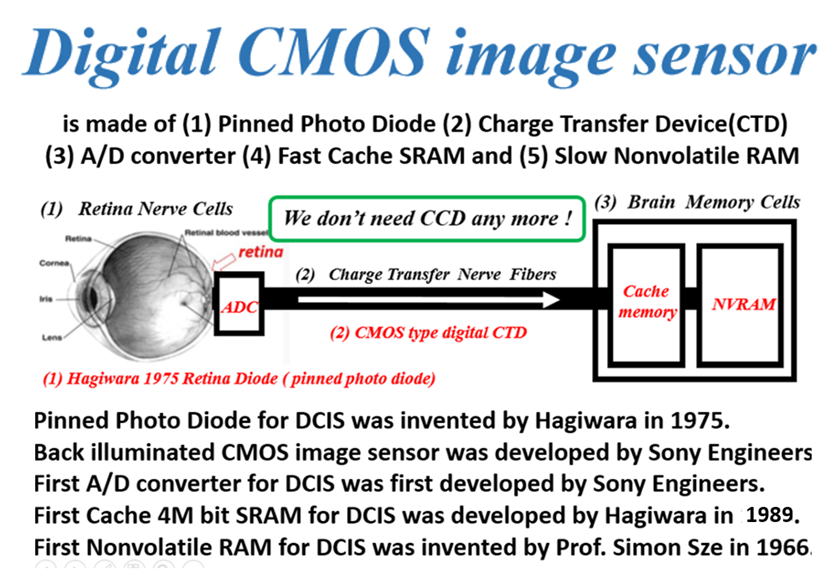

We now have (1) Pinned Photo Diode (2) One Charge Transfer Gate (CTD) (3) A/D converter

(4) Digital Signal Transmission Line ( just digital circuits ) (5) Fast Cache SRAM for qick

digital picture data aquision, and finally (6) Nonvolatile Memory (NVRAM) in the modern

small conpact CMOS digital image sensor camera.

Compact and Handy Consumer Digital Camera must be by definition small and compact.

SONY enginners worked very hard to realize SONY original HAD CCD and CMOS degital

cameras. Howerver, outside SONY, the SONY brand name, SONY original HAD, is not used.

Instead, it is called worldwide the Pinned Photo Sensor. The truth is, the Pinned Photo

Diode and SONY original HAD sensor are the same thing that Hagiwara invented in 1975.

*******************************************************************

See also three invited talks related to SONY HAD sensor now called also

as Pinned Photo Diode.

(1) International Conference CCD79 in Edinburgh, Scotland UK

(2) International Conference ESSCIRC2001 in Vilach, Austria.

(3) International Conference ESSCIRC2008 in Edinburgh, Scotland UK

*******************************************************************

As seen above from the two original Japanese Patents filed by Yoshiaki

Hagiwara at SONY in 1975,

it is very clear that Hagiwara is the true inventor of the Pinned Photo

Diode.

But Hagiwara is not happy now because the world does not understand this

fact.

The details are explained below.

*************************************************************************************

In June 2018, Hagiwara was not very happy

when Hagiwara learned that Teranishi-san ( ex-NEC )

was awarded with Queen Elizabeth Award 2017

as the inventor of Pinned Photo Diode, which was

based on his 1982 IEDM paper on the Buried Photo Diode

in the Interline Transfer CCD image with no image lag.

*************************************************************************************

http://qeprize.org/winner-2017/

https://en.wikipedia.org/wiki/Queen_Elizabeth_Prize_for_Engineering

*************************************************************************************

On 1 February 2017, it was announced that the 2017 prize would be awarded

to the four engineers responsible for the creation of digital imaging sensors.

The announcement was made by Lord Browne of Madingley at the Royal Academy

of Engineering, in the presence of HRH The Princess Royal.

The winners of the 2017 prize were:

(1) George E. Smith of United States for the invention of the charge-coupled

device (CCD) principle

(2) Michael Tompsett of UK for the development of the CCD image sensor,

including the invention of the imaging semi-conductor circuit and the analogue-to-digital converter

(3) Nobukazu Teranishi of Japan for the invention of the pinned photodiode

(PPD)

(4) Eric Fossum of United States for developing the CMOS image sensor

Together, their innovations allowed for advancements in medical treatments,

science,

personal communications and entertainment.

The winners will receive their award in a ceremony at Buckingham Palace later in 2017.

**************************************************************************************************

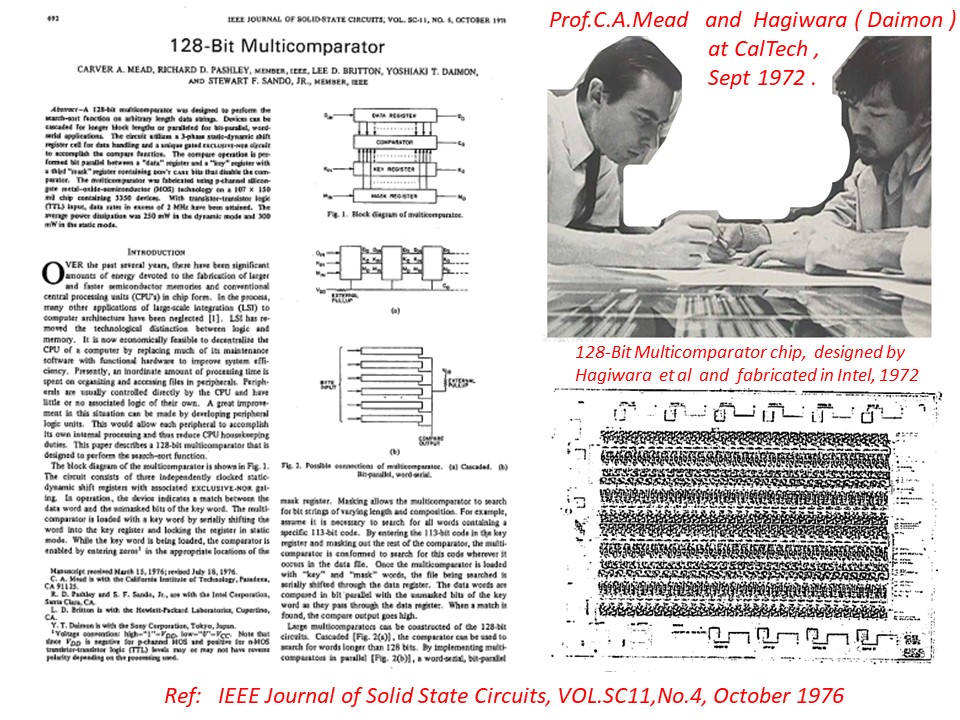

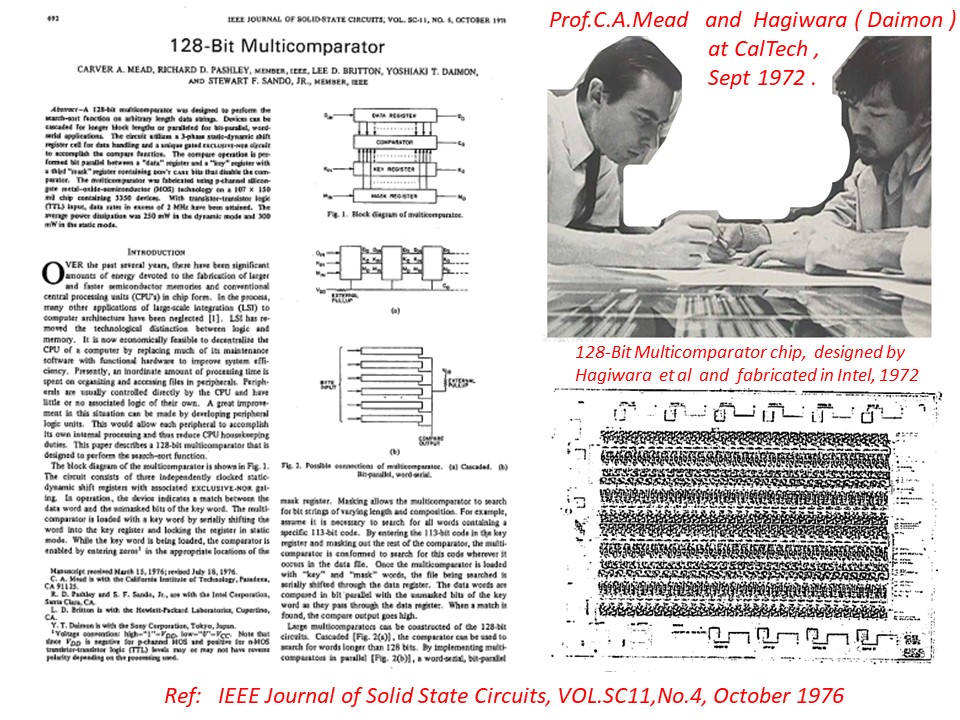

Before going into the details of the Pinned Photo Diode,

the background information about Hagiwara's early

engineering works are first explained briefly here.

Hagiwara also designed a MOS digital LSI chip,

a 128 bit Multicomarator silicon chip,

when he was a graduate student at CalTech.

Prof. C.A.Mead was one of his PhD thesis advisers.

Prof. C.A.Mead and Dr. Gordon Moore are also CalTech graduates.

They both are good friends, and they met each other frequently

in our reserch lab at CalTech. Our CalTech EE department lab

is now called as Gordon Moore Lab of Electrical Engineerings..

The 128 bit multicomparator chip was designed by Hagiwara

and other fellow students in 1972 with Prof. C. A. Mead's advice,

and was fabricated in the Intel MOS process line with helps of

many CalTech graduates in Intel.

The results were published later in 1976 in IEEE Journal of

Solid State Circuits, VOL.SC-11, No.4, October 1976.

By that time, Hagiwara had graduated from CalTech and was

working in SONY, Japan for making image sensors and video

camera system LSI chip set for consumer digital camera.

Haiwara is the true inventor of the Pinned Photo Diode and

many dilligent SONY engineers and Hagiwara worked together

very hard to build the first CCD digital camera.

And now many dilligent SONY engineers of younger generations

worked togerther to build the first CMOS digital camera with

the backside illumination and in the stacked digital chip formation

which includes A/D Converter , Memory and Processor Units.

CCD and CMOS digital cameras were both developed by SONY.

Hagiwara taught young SONY engineers about digital LSI circuit

design techniques, which Hagiwara himself studied in CalTech

with Intel , HP, IBM engineers. All of them including Hagiwara

were once students of Prof. C.A. Mead in CalTech.

In the PS3 project by SONY, Toshiba and IBM, Hagiwara later

learned that one senior PS3 design engineer Hagiwara worked

together was also a CalTech graduate who used to study and

work in the same Gordon Moore EE Lab in CalTech.

****************************************

Yoshiaki Hagiwara of SONY is the inventor of Pinned Photo Diode.

https://patents.justia.com/inventor/yoshiaki-hagiwara

Pictures of Pinned Photo Diode invented by Hagiwara in Patnet 1975

****************************************

*******************************************************

*******************************************************************

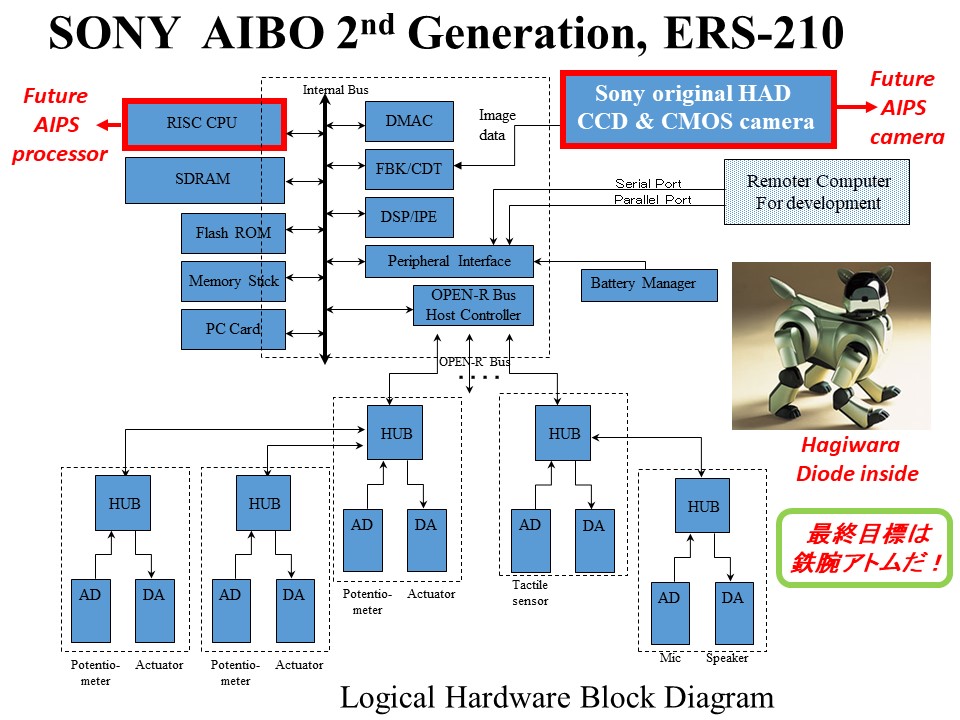

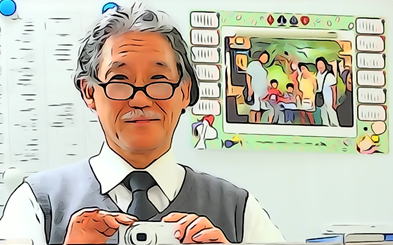

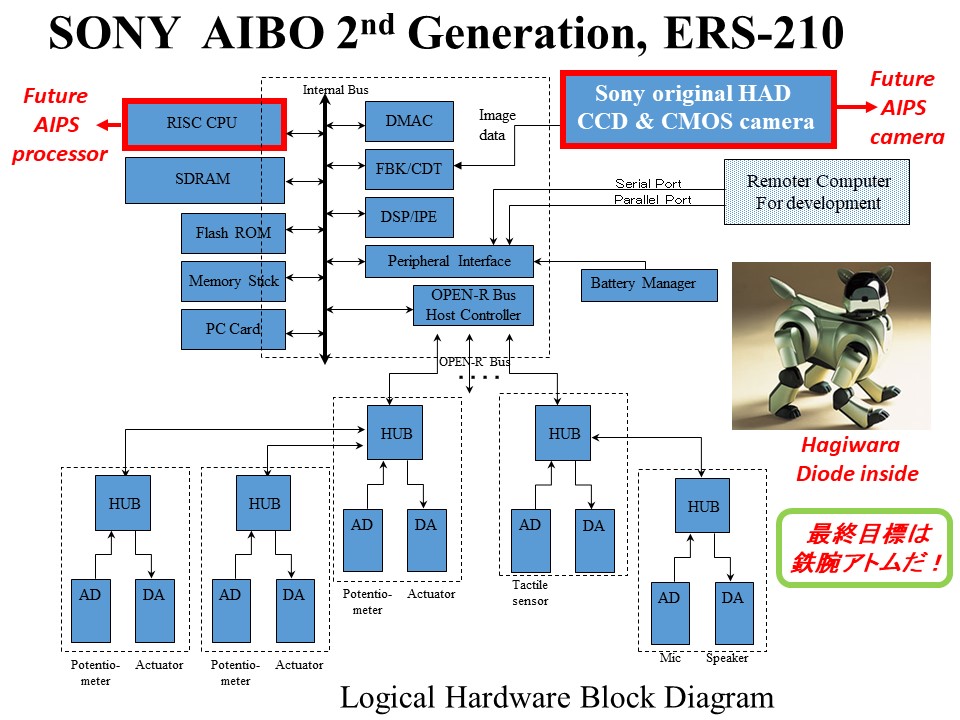

Digital CMOS Image Sensor is watching at its inventor, Yoshiaki Hagiwara.

Hagiwara is the Inventor of SONY HAD and Pinned Photo Diode Image Sensors.

*******************************************************************

**********************************

Please purchase and read

"The world of Digital Circuit Systems

that supports the artificial intelligent

partner systems (AIPS). " written in

Japanese by Yoshiaki Hagiwara in 2016.

ISBN 978-4-88359-339-2 C3055

Price 9000 Japanse Yen and TAX.

B5 size Hard Cover 475 pages

Publisher Seizansha_Inc

Tel +81-42-765-6460

https://www.seizansha.co.jp/ISBN/ISBN978-4-88359-339-2.html

*************************************

return to http://www.aiplab.com

**************************************

Hagiwara and his team worked together to build

a Fast 25 nanosec 4 M bit SRAM chip in 1989

to be used as the fast cache memory

for the digital data from digital cameras.

Fast SRAM is needed to store temporarily the digital image data.

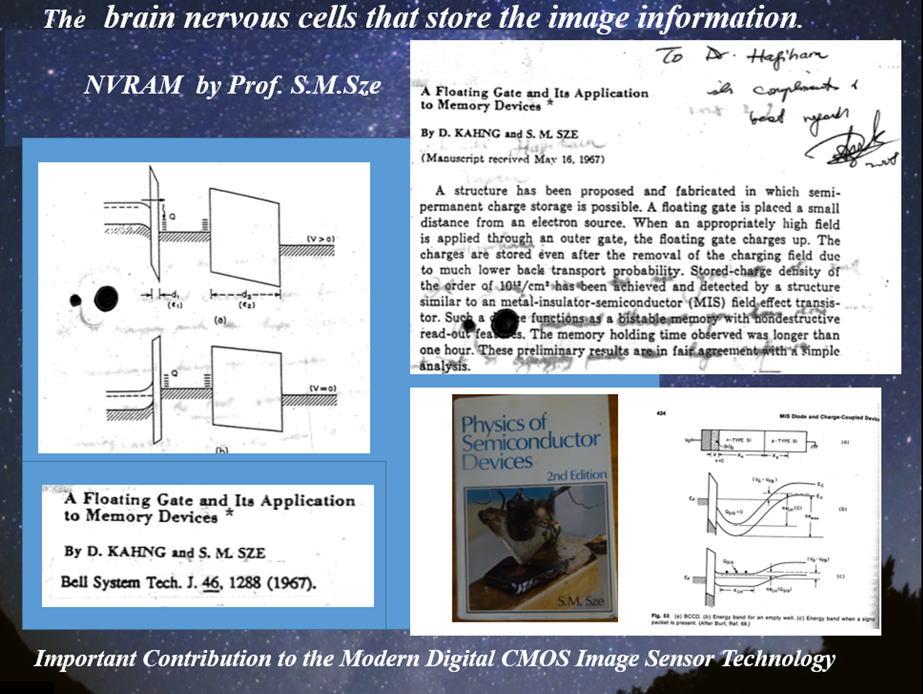

However, NVRAM is a very important media to store the data permanetly.

The polysilicon floatig electorode type NVRAM was invented

by Dr. D. Kahng and Prof. S.M. Sze in 1967

when I was a freshman in Caltech,

just about to learn about Feymann Physics.

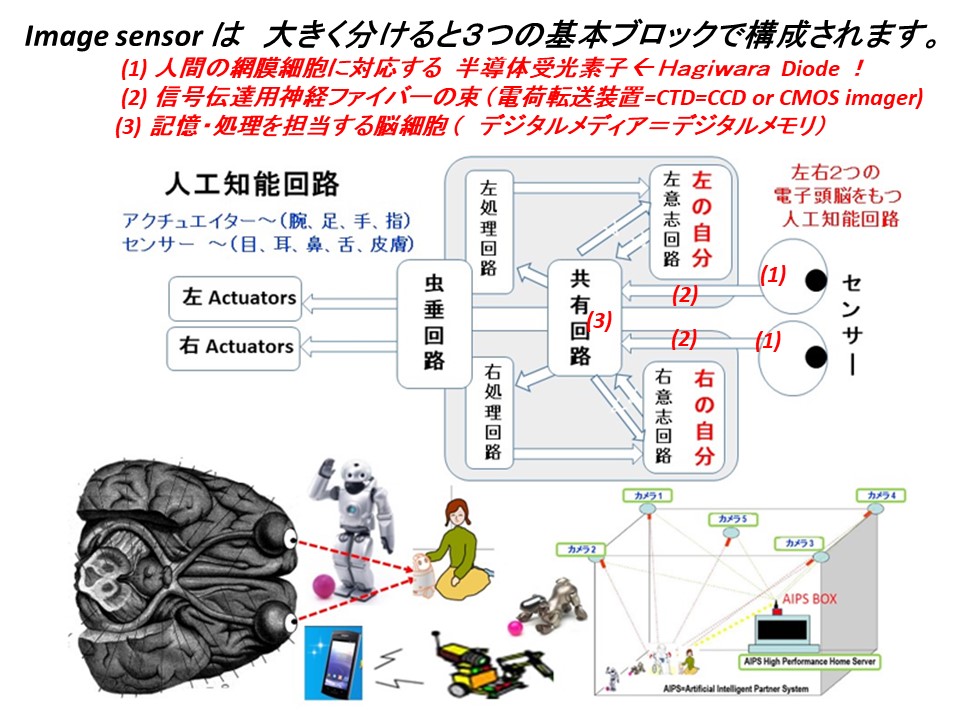

So, in order to build one digital camera,

we need at least the five basic parts,

(1) PPD (2) CTD (3) ADC (4) SRAM (5) NVRAM.

PPD stands for Pinned Photo Diode which is the same thing

as the SONY original HAD ( Hole Accumulation Diode )

which was invented by Yoshiaki Hagiwara at SONY in 1975.

This is a long story about Pinned Photo Diode.

The pinned photo diode can be applied not only for consumer video cameras

but also for artificailly intelligent (AI) robot vision systems for many

apllications.

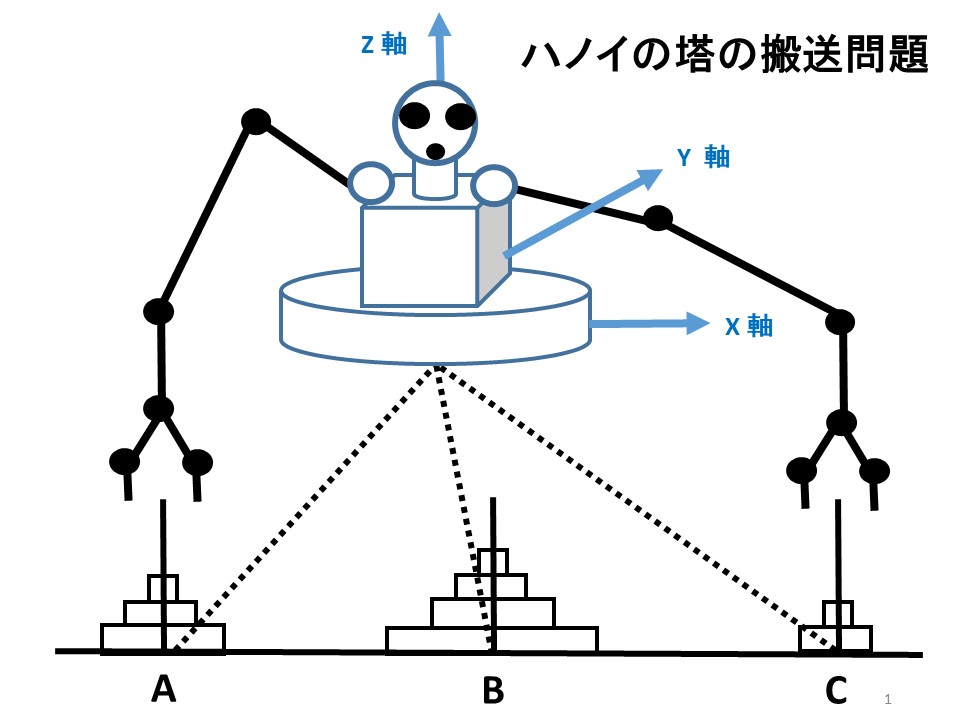

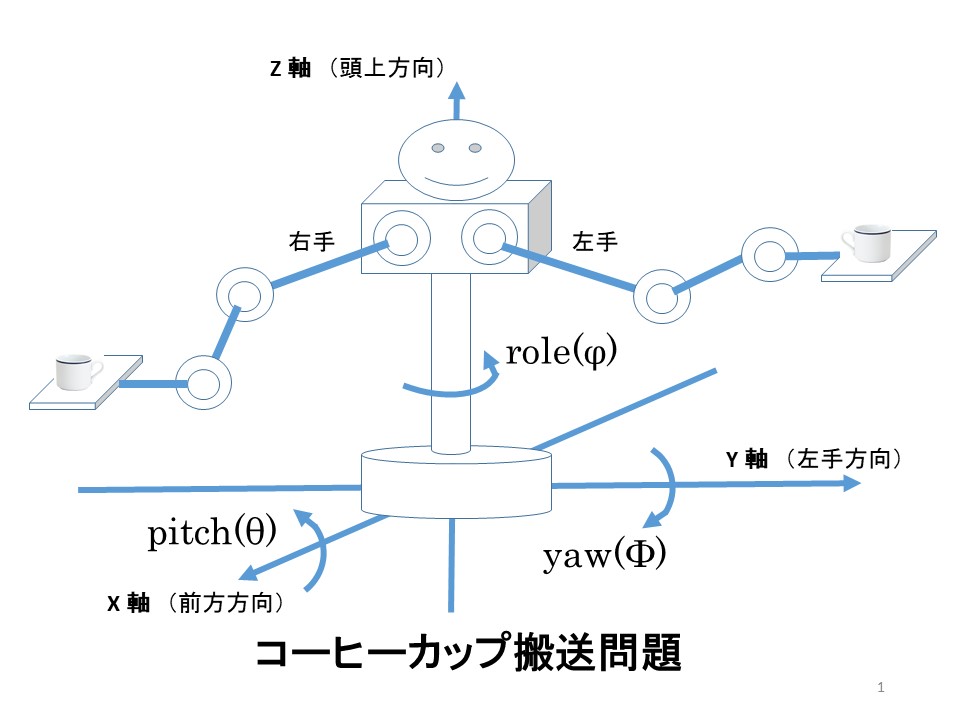

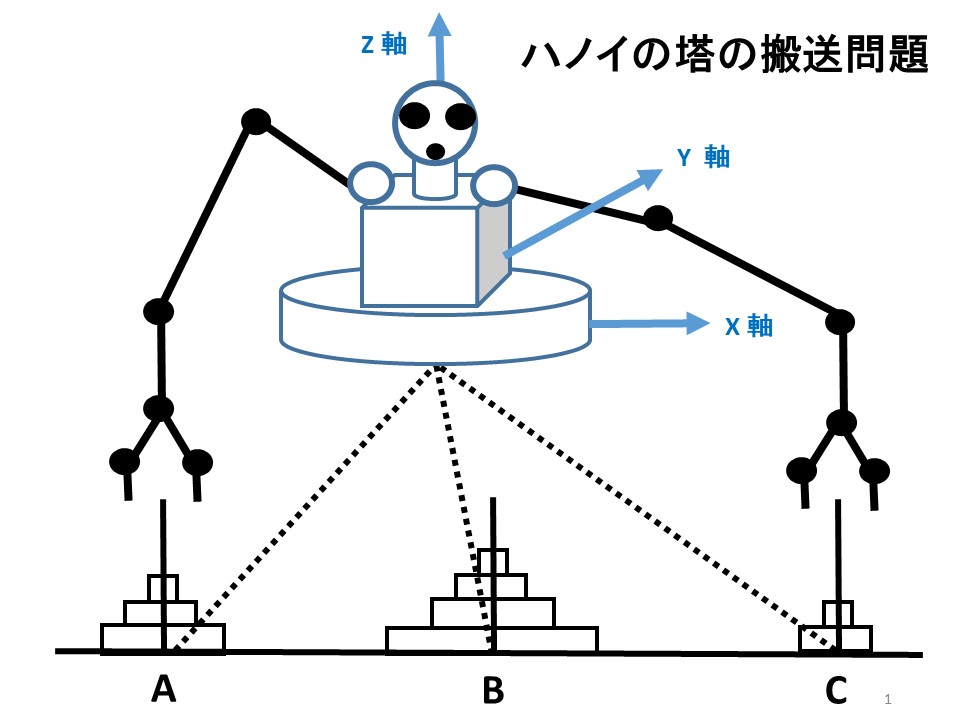

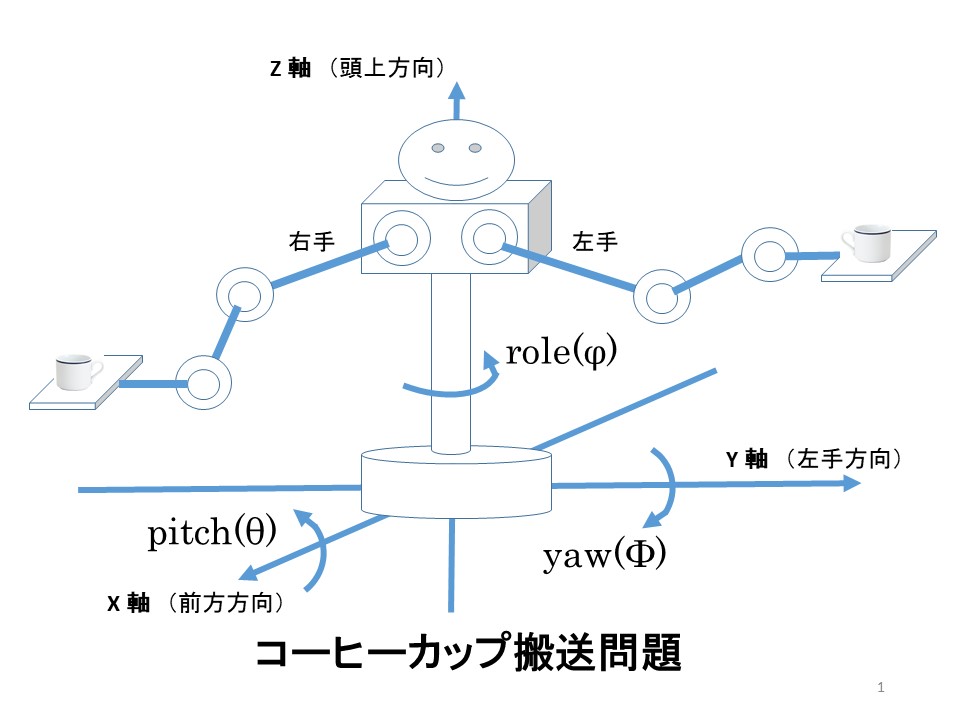

Hanoi Tower Problem

Coffee Cup Problem

Artificial Intelligent Robot Vision

In 1975 Hagiwara invented the Pinned Photo Diode for future AI Robot Visions.

Hagiwara invented the Pinned Photo Diode in 1975.

SONY introduced in 1978 a very light sensitive video camera system with the Pinned Photo Diode.

SONY introduced to the world the super light sensitive CCD image with the

Hagiwara Photo Diode,

which later SONY called SONY original HAD sensor and the world called the

same thing as

the Pinned Photo Diode. The truth is that Hagiwara is the inventor of the

SONY original HAD

sensor and also the Pinned Photo Diode. Hagiwara saved CCD which everyone

gave up to use

because CCD has very poor light sensitivity. With Hagiwara's invention,

CCD image sensor

became a very light sensitive image sensor. The truth is that CCD is really

light sensitive.

Hagiwara Photo Diode invented by Hagiwara in 1975 is the super light sensitive

photo diode.

The world did not call it Hagiwara Diode. SONY called it SONY original

HAD sensor. The world

outside of SONY all called it Pinned Photo Diode. But both are Hagiwara's

invention. They

are Hagiwara Photo Diode. SONY HAD sensor is in a sense SONY HAgiwara Diode.

Even the backside illuminated modern CMOS image sensor is based on

the Hagiwara 1975 invention ( 1975-127647 ).

Hagiwara is the inventor of .the backside illuminated PPD image sensor.

Hagiwara is also the inventor of the Schottky barrier type PPD image sensor.

Hagiwara is also the inventor of the vertical charge transfor opration,

that is,

with the completely depleted signal charge storage area by the complete

charge transfer mode operation in the vertical direction in the silicon

crystal.

CCD has a very important feature of Complete Charge Transfer operation,

but CCD charge transfer operation is along the surface of the Silicon cystal.

The Photo Diode Hagiwara proposed in his 1975 patents have the vertical

direction charge trasfer operation with Complete Charge Transfer Modes

as seen in the figures given in Hagiwara 1975 patents.

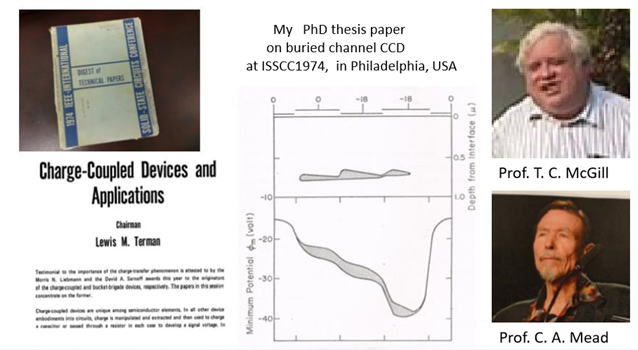

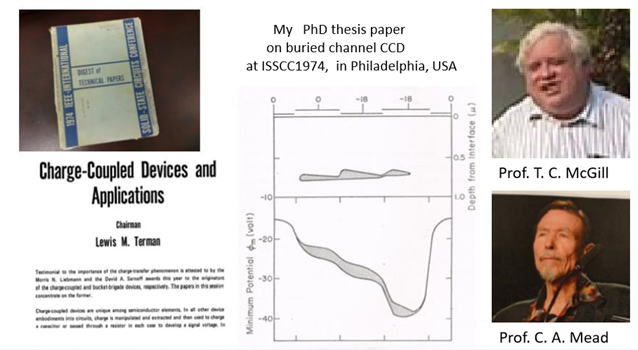

Yoshiaki Hagiwara received BS(1971),MS(1972) and PhD(1975) degrees from

California Institute of Technology ( CalTech ) in Pasadena, California

USA.

His PhD thesis was about the complete charge transfer mechanism of

the buried channel CCD operations by computer simulation analysis.

Hagiwara published his PhD thesis at the international solid state circuits

conference ISSCC1974, and showed that the newly invented buried channel

CCD has very fast and efficient charge transfer capability, achieving the

99.999% charge transfer efficiency, which is a very important feature for

consumer video camera applications.

The original invention of the sureface type CCD had the charge transfer

efficciency of about 99.9 % which is not enough for any practice application.

Intel gave up making CCD type dynamic memory LSI chips. CCD was well

recognize in early 1970s when Hagiwara started working for his PhD thesis.

But by 1975 most of the companies gave up to any CCD in any LSI chip

business applications. Sony was the only company in the world seriously

working hard on CCD for consumer video cameras for home video systems.

Hagiwara joined Sony on February 10, 1975, right after the PhD final oral

presentation, and soon learned that the camera system engineers did not

like poor light sensitive CCD image sensors, because CCD is composed

of a series of charge transfer metal electrodes, which are inherently

Metal-Oxide-Semiconductor ( MOS ) capacitors, and the metal electrons,

as you know all, do not pass light.

The truth is that CCD image sensor has a poor light sensitivity inherently.

Hitachi engineers were working on the classical MOS image sensors which

have SiO2 exposed N+Psub junction type photo diode which had excellent

light sensitivity.

Hagiwara worked in Sony as a university student trainee in SONY bipolar

transistor process lines in the summers of 1971 and 1973, and understood

the device structures and operations of bipolar transistors, including

the

thyristor punch-thru operaion mode which was undesirable for the

proper operations of the bipolar transistor type LSI chips for SONY

color TV sets.

With the two hints, that is, with Hitachi N+P junction photo diode and

with Sony P+NPNsub junction type bipolar transitor technology,

Hagiwara created a new more powerful photo diode structure.

Hagiwara soon filed two patents on the new photo diode structures

for buried channel CCD type charge transfer device (BCCD type CTD),

But Hagiwara inventions were on the photo diode structures which

can be apllied both for CCD type CTD and also for MOS type CTD.

The new photo diode structures were invented and defined in details

in Hagiwara 1975 patents are shown below. This new photo diode

structure is now called as Pinned Photo Diode, which is also very

identical to the Sony origilal Hole Accumulation Diode ( Sony HAD ).

For the original document, visit and search the Japanese Official Patent

Web :

https://www4.j-platpat.inpit.go.jp/eng/tokujitsu/tkbs_en/TKBS_EN_GM101_Top.action

Put the document number ( 1975-134985 ) for Hagiwara 1975 invention on

the P+NPNsub junction ( thyristor ) type Pinned Photo Diode with vertical

OFD.

For the original document, visit and search the Japanese Official Patent

Web :

https://www4.j-platpat.inpit.go.jp/eng/tokujitsu/tkbs_en/TKBS_EN_GM101_Top.action

Put the document number ( 1975-127647 ) for Hagiwara 1975 invention on

the NPNN+ junction ( NPN transistor structure )type Pinned Photo Diode

with vertical charge transfer to the surface type MOS charge transfer gate.

SONY original HAD and Pinned Photo Diode are the same thing,

both invented and defined in the two Japanese Patents

Please visit the oficial Japanese Patent Search Web Site,

https://www4.j-platpat.inpit.go.jp/eng/tokujitsu/tkbs_en/TKBS_EN_GM101_Top.action

to search Hagiwara's original Japanese Patents and put the following two

document numbers,

Document No. ( 1975-134985 ) on the P+NPNsub junction type PPD Patent

Invention and

Document No. ( 1975-127647 ) on the NPNN+ junction type PPD Patent Invention

、

both filed by Yoshiaki Hagiwara in 1975 at Sony.

See the original Pinned Photo Diode Patent 1975

See three invited talks related to SONY HAD sensor now called also as Pinned

Photo Diode.

(1) International Conference CCD79 in Edinburgh, Scotland UK

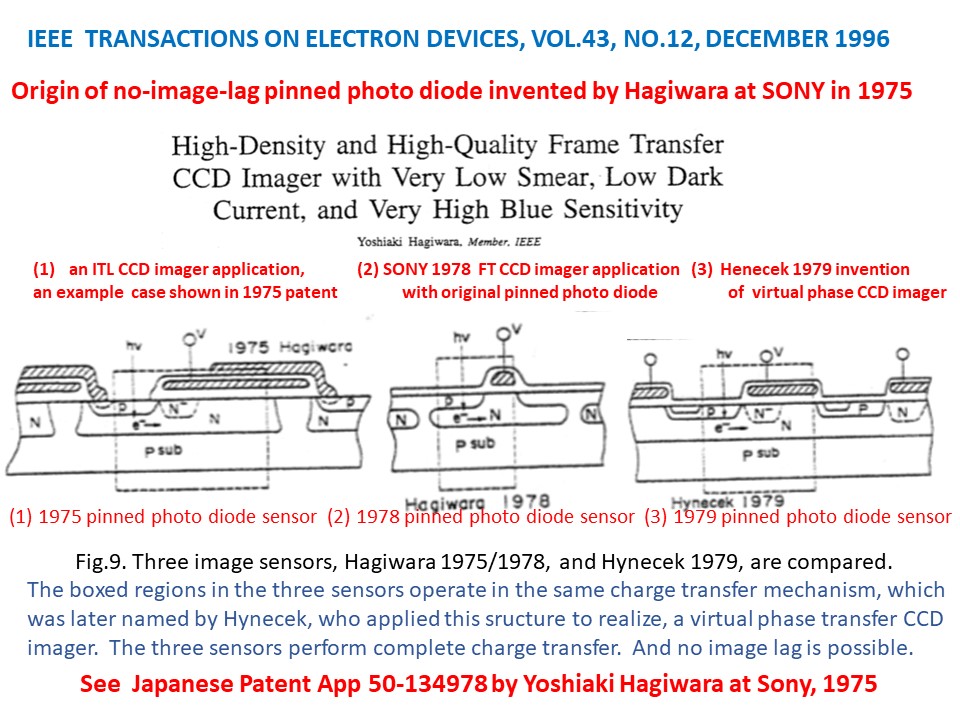

(2) International Conference ESSCIRC2001 in Vilach, Austria.