## Japanese Official Invention Acknowledgement WEB site

See http://koueki.jiii.or.jp/innovation100/innovation\_detail.php?eid=00059&test=open&age=

| イメージ                                  | ジセンサ                       | — (CCD · C                         | MOS)                          |                                                                                                                   |                                  |                                |

|---------------------------------------|----------------------------|------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------------------------|

|                                       | 概要                         | イノペーション                            | >に至る経緯                        | 発明技術開発の概要                                                                                                         | 主な受賞歴                            | 参考文献等                          |

| 概要                                    | 発明                         | 明協会の公                              | ≿式WEB                         | サイトからの情                                                                                                           | 報                                |                                |

|                                       |                            |                                    |                               | 「スタートである。機械式<br>トを与えつつ、大きく発                                                                                       |                                  | 撮像素子(以下                        |

|                                       | り、固体化力                     | 「望まれていた。1                          | 1960年代半ばに                     | 、消費電力が大きい、置<br>にイメージセンサーの開新<br>秋原の発                                                                               | ŧがスタートした                         | 。そのときは、                        |

| 単純であり、イメー<br>加えられたことから、<br>1978年、山田歴生 | ジセンサーの<br>イメージt<br>(当時 東芝) | )ような大規模な7<br>2ンサー開発の中心<br>は、強い光が入身 | アレイ構造を製<br>ひはCCDにな<br>けしたときに総 | <ul> <li>Coupled Device、電荷<br/>進するのに適しているこ<br/>った。1970年後半からに<br/>線の段信号を発生させる。</li> <li>(当時 N E C) が、白橋</li> </ul> | と、矢継ぎ早に(<br>は開発の中心は日<br>ブルーミングを# | C C D に改善が<br>体に移った。<br>0利する縦型 |

| や転送ノイズを解消                             | する埋込フィ                     | トダイオード (0                          | Pinned Photod                 | lode)を発明した <sup>1</sup> 。ご<br>して星産されていった。                                                                         |                                  |                                |

| は、埋込フォトダイ:<br>多くの機関で熱心に!              | オードをCM<br>開発が進めら           | OSイメージセンセ<br>られた。2000年に            | ナーに適用する<br>3米田智也ら(3           | ジスターを画素内に配置<br>ことでCCDと同等以上<br>9時 キヤノン)が、強い<br>1ら (当時 ソニー)が、3                                                      | の低ノイズが達用<br>光が入射したとき             | 成でき、世界の<br>きに発生する              |

| 5. これらの技術開発                           | NによりCMG<br>的に増加させ          | 05イメージセンサ<br>たいった。2010             | ーが主役になり<br>年に楊林拓ら             | <ol> <li>低消費電力という様</li> <li>(当時 ソニー) が、イメ・</li> </ol>                                                             | 主のお始ちあり、                         | 携帯電話に搭載                        |

|                                       |                            |                                    |                               | ed Photo Diod<br>射も実際は萩                                                                                           |                                  |                                |

This Japanese Official Invention Acknowledgement WEB site, written in Japanese, says,

- (1) The vertical Overflow drain was invented by Yamada-san of Toshiba in 1979.

- (2) The pinned photo diode was invented by Teranishi-san of NEC in 1979.

- (3) The back-light illumination image sensor was invented by Suzuki-san of Sony in 2001.

But Hagiwara believes that

- (1) Hagiwara invented in 1975 the vertical Overflow drain, NOT Yamada-san of Toshiba in 1979.

- (2) Hagiwara invented in 1975 the pinned photo diode, NOT Teranishi-san of NEC in 1979.

- (3) Hagiwara invented in 1975 the back-light illumination image sensor, NOT Suzuki-san of Sony in 2001.

Which one is the truth ? Please judge for yourself.

Yoshiaki Hagiwara visited his friends in Sony Kumamoto Technology Center on November 19, 2018.

https://electronics.stackexchange.com/questions/83018/difference-between-buried-photodiode-and-pinned-photodiode/83025

🖄 stack over

0

🗱 slack 🎽

What is the difference between Buried Photodiode and Pinned Photodiode? I understand that the P+/N/P structure where the P+ and P layers have the same potential is the Pinned Photodiode. So what is the buried Photodiode?

This is a commonly misunderstood misused set of terminologies.

First off these are not PIN Photodiodes - which stands for P - Intrinsic- N. These have large depletion regions for higher internal QE (Quantum Efficiency) and faster response. You can't make an array with this design though.

Pinning, refers to fermi-level pinning or pinning to a certain voltage level. Or also the forcing or prevention of the fermi-level/voltage from moving in energy space.

You can get surface state pinning from the dangling Si/SiO2 bonds providing trapping centers. A buried PD (Photodiode) has a shallow implant that forces the charge carriers away from these surface traps. The Si/SiO2 surface contributes to increased leakage (dark current) and noise (particularly 1/f noise from trapping/de-trapping). So confusingly a buried PD avoids pinning of the fermi-level at the surface.

A pinned PD is by necessity a buried PD, but not all buried PD's are pinned. The first Pinned PD was invented by Hagiwara at Sony and is used in ILT CCD PD's, these same PD's and the principles behind this complete transfer of charge are used in most CMOS imagers built today.

A pinned PD is designed to have the collection region deplete out when reset. AS the PD depletes it becomes disconnected from the readout circuit and if designed properly will drain all charge out of the collection region (accomplishing complete charge transfer). An interesting side effect is that the capacitance of the PD drops to effectively zero and therefore the KTC noise  $q_n = sqrt(KTC)$  also goes to zero. When you design the depletion of the PD to deplete at a certain voltage you are pinning that PD to that voltage. That is where the term comes from.

I've edited this Answer to acknowledge Hagiwara-san's contribution. It has long been incorrectly attributed to Teranishi and to Fossum (in CMOS image sensors)

share edit

edited Aug 16 at 19:17

answered Sep 21 '13 at 14:34 placeholder 27.3k • 8 • 49 • 97

It is important that this reply stand for context and to correct for a historical error and misreporting. One cannot understate the importance of how significant his techniques and efforts have been. Even if this doesn't align with the EE.SE . In the previous form of my answer, I was reporting on the narrative that has been promoted in the image design community. Attribution is imortant. placeholder Aug 16 at 19:20

Evidence that Hagiwara invented the Pinned Photo Diode in 1975.

Yoshiaki Hagiwara, Ph.D. IEEE Life Fellow

\*\*\*\*\*\*

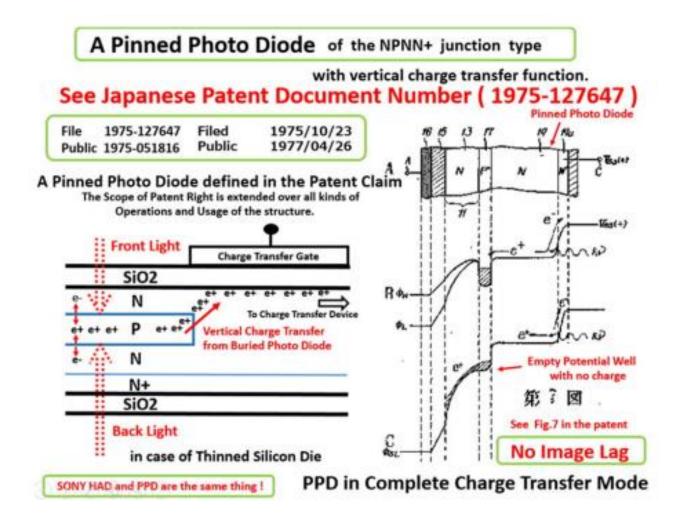

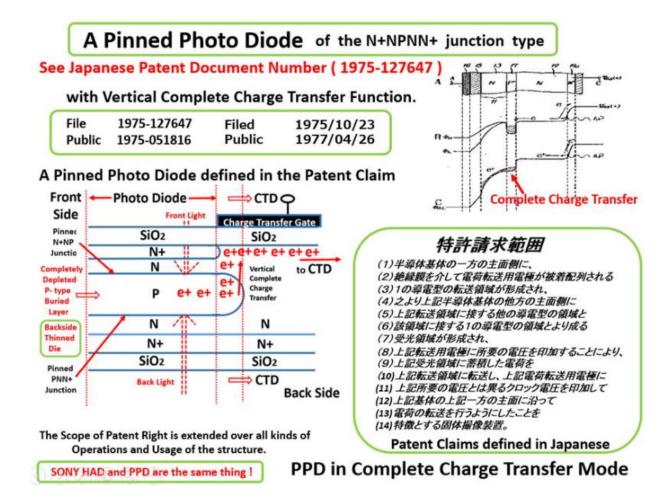

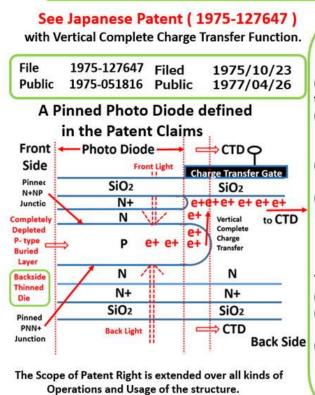

Evidence that Hagiwara at Sony is the true inventor of the Pinned Photo Diode is given by the two Japanese patents Hagiwara filed in 1975 at Sony, Japanese Patent (1975-127647) and (1975-134985). The evidence is described in details in these two Hagiwara 1975 patents.

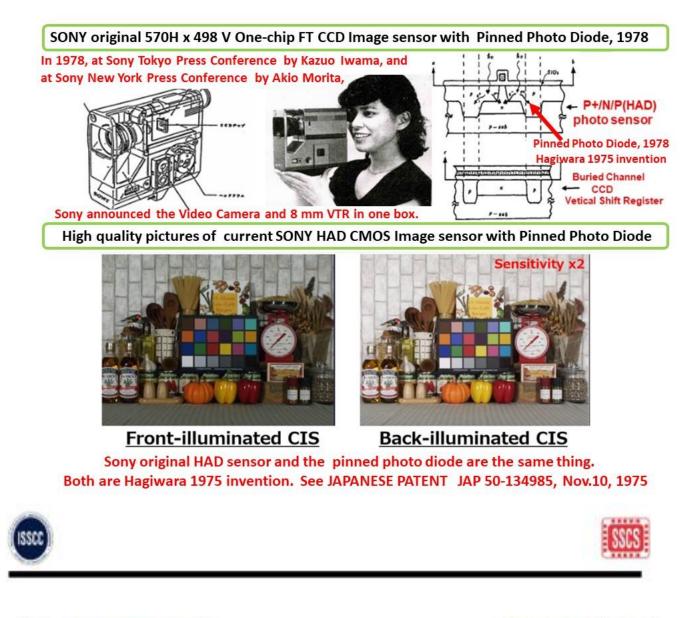

In 1978 Sony announced a new video camera in Tokyo and New York Press Conferences at the same date, one held by Sony Chairman Akio Morita in New York and the other one held by Sony President Kazuo Iwama in Tokyo at the same date in 1978.

The video camera announced in the two Press Conference was built with the Frame Transfer CCD image sensor with the Pinned Photo Diode light detecting photo sensing picture cell structure that Hagiwara invented in 1975, which has a very light sensitivity, a very low noise and a very low image lag features.

The figures N0.1 thru No.5 in Hagiwara 1975 patent (1975-134985) explained in details an example of the interline transfer CCD image sensor application with the Hagiwara invented Pinned Photo Diode.

Sony engineers, after the 1978 Press Conferences in Tokyo and New York, worked hard for, and succeeded to acquire, the production and the reliability technolgy of the CCD video camera of the interline transfer CCD image sensor application with the Pinned Photo Diode light detecting picture cell structure with the vertical overflow drain function built in each P+NPNsub junction (thyristor) type PPD.

With the diligent SONY engineers efforts, SONY could produce the portable Passport size Compact CCD image sensor video camera, with the Pinned Photo Diode (PPD) that Hagiwara invented in 1975. And at the same time, Sony filed a trading name officially, which is the SONY Brand Name of "Sony original HAD sensor".

ページ(1)

With the help of the Hagiwara invented Pinned Photo Diode, which was now called as "Sony original HAD sensor " with the strong SONY original sales features of high light sensitivity, low noise and no image lag characteristics, Sony could become soon very dominant and strong over the world consumer video camera markets.

The feature of no image lag characteristics in the Hagiwara invented Pinned Photo Diode is explained and shown in details, as an example application case, in the figure No.6 of Hagiwara 1975 Japanese Patent (1975-134985) and also in the figure No.7 of Hagiwara 1975 Japanese Patent (1975-127647) in details.

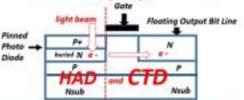

Hagiwara 1975 Japanese Patent (1975-127647) proposed a Back Light illumiantion type light detecting photo sensing picture cell structure with the buried layer type photo signal charge storage. And in the figure No.7 of Hagiwara 1975 Japanese Patent (1975-127647) was shown clearly how the signal charge in the buried storage layer are trasfered completely to the region under the charge transfer gate formed on the front side of the silicon wafer. This means clearly the light sensing picture cell structure, which is now worldly called as the Pinned Photo Diode, has the very important feature of no image lag characteristics.

The patent claim descriptions and the patent figures for possible patent application examples given in details in these two Hagiwara 1975 Japanese patents (1975-127647) and (1975-134985) support the fact that Hagiwara is the true inventor of Pinned Photo Diode.

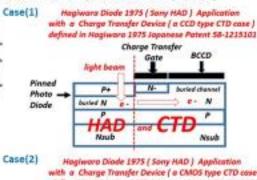

In conclusion, it is a clear cool fact that Hagiwara at Sony is the true inventor of the Pinned Photo Diode. The Haiwara patents claims that the light detecting picture cell structure (now called as the Pinned Photo Diode) can be applied to any kind of charge transfer devices (CTD) which includes the BBD type, the classical MOS type, the CCD type and the modern CMOS image sensor type charge transfer devices.

Hagiwara proposed the Pinned Photo Diode with P+NPNsub junction (thyrisor) type light detecting picture cell structure with the vertical over flow drain for the first time in the world.

ページ(2)

Moreoever, Hagiwara proposed in the Japanese patent application example of figure No.7 of Japanse patent (1975-126747) the Back Light illumination Pinned Photo Diode (PPD) type Light Detecting Picture Cell Structure for the first time in the world.

Moreoever, Hagiwara proposed in the 1975 patent application example of figure No.4 of Japanse patent (1975–134985) the Schottky Barrier type Light Detecting Picture Cell structure in the Interline transfer type CCD image sensor application for the first time in the world.

However last year Hagiwara learned a very surprising news :

The winners of the 2017 Queen Elizabeth Prize for Engineering Foundation were :

- (1) George E. Smith for the CCD image sensor invention

- (2) Michael Tompsett for the CCD image sensor development.

- (3) Nobukazu Teranishi for the invention of the pinned photodiode (PPD) and

- (4) Eric Fossum for developing the CMOS image sensor.

Hagiwara, as the true inventor of the Pinned Photo Diode, got really surprized at the announcement that Teranishi was awarded for the invention of the pinned photodiode(PPD).

And many SONY dilligent engineers working for the compact digital CMOS image sensors got really surprized at the announcement that Fossum was awarded for developing the CMOS image sensor.

ページ(3)

The truth is that Teranish did not invent the PPD. Teranish only published in his 1982 IEDM paper the image lag free interline CCD image sensor with the PPD light detecting photo sensor structure that was invented by Hagiwara in 1975. Hagiwara 1975 patents clearly defined the image lag free interline transfer CCD image sensor as an application example in his 1975 patent claims. And the first image lag Interline transfer CCD image was designed by Hagiwara and developed by Sony deligent engineer team in 1980 with the transparent electrode type MOS type light detectiong structure with CCD charge transfer mode and with the lateral overflow drain function.

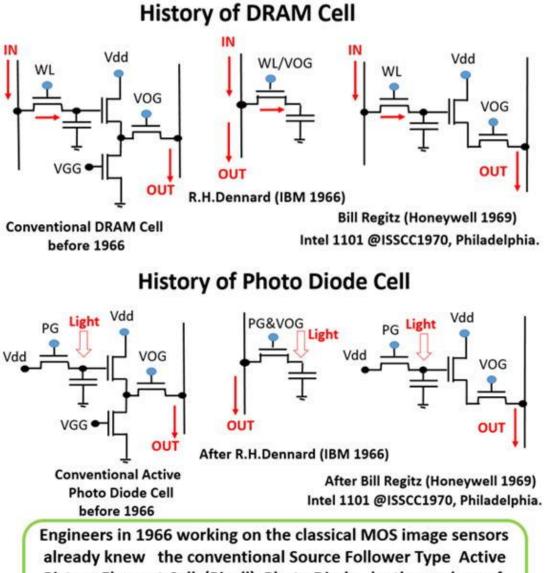

Fossum wrote a paper on "Active Pixel Sensors: Are CCD's dinosaurs ?", in Proc. SPIE, Vol.1900, pp.2-14, 1993. However, the three transistor type active circuit was already invented by Bill Regitz of Honeywell in 1969. This active pixel sensors was not Fossum invention. Fossum actually did not develop the active pixel sensors either. Sony dilligent engineerings did.

Hitachi MOS Image Sensor Engineers and Intel MOS Process Engineers all knew that eventually scaled down MOS Process Technology will conquer all other kinds of Process Technologies including CCD image sensor technology because of the power consideration and scaled down dimensional advantage of CMOS process technology. The three transistor CMOS active picture cell was already invented as, since the three-transistor circuit is identical to, the three-transitor circuit of the DRAM cell with the active source follower type current amplification. Fossum was just a commentator in his SPIE 1993 paper above. Fossum was just emphasizing the well understood fact and speculations that the original image sensor experts all knew in 1970s. Fossum did not invent active pixel sensors. Peter Noble did. Fossum actually did not develop the active pixel sensors himself either.

Sony diligent engineerings developped the active pixel Pinned Photo Diode type Light detecting photo sensors for compact digital CMOS image sensors with the Back Light Illumination.

ページ(4)

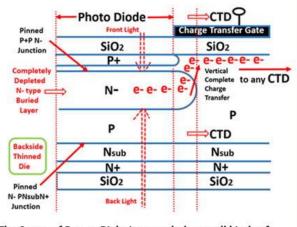

## A Pinned Photo Diode of the N+NPNN+ junction type

## See Japanese Patent (1975-127647) with Vertical Complete Charge Transfer Function.

| File   | 1975-127647 | Filed  | 1975/10/23 |

|--------|-------------|--------|------------|

| Public | 1975-051816 | Public | 1977/04/26 |

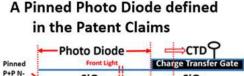

#### A Pinned Photo Diode defined in the Patent Claims Front Photo Diode CTDC Side Front Light Charge Transfer Gate Pinnec SiO<sub>2</sub> SiO<sub>2</sub> N+NP N+ e+e+e+ e+ e+ e+ Junctio e+ Ν Completely Vertical to CTD Depleted Complete e+ P- type Charge e+ e+ Ρ e+ Transfer Buried Layer N N Backside Thinned N+ N+ Die SiOz SiO<sub>2</sub> Pinned PNN+ \Rightarrow CTD **Back Light** Junction **Back Side**

The Scope of Patent Right is extended over all kinds of Operations and Usage of the structure.

SONY HAD and PPD are the same thing !

**Patent Claims**

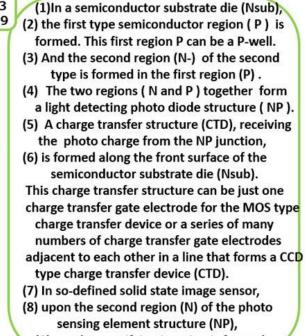

(1)On the front side surface of the semiconductor substrate die (Nsub),

Here Nsub can be chosen for easy-understanding.

The substrate can be a P-type substrate (Psub ) but will make pictures more confusing and complex. )

(2) the charge transfer MOS gate (CTG) electrode is formed on the oxide insulator (SiO2) layer

Which is formed on the surface of the substrate die Nsub. This MOS gate now is a PMOS type gate.

(3) The first doping type region (N) is formed to store and transfer signal charges under the CTG electrode. For easy-understanding, this first region can be an N-well in the N-sub type substrate die.

(4) Besides that, along the backside surface of

the semiconductor substrate Nsub, (5) another region (P) of another doping type is formed in the substrate die(Nsub), which is placed adjacent to the charge transfer region under the CTG. This second region(P) can be formed by selfaligned deep ion-implantation to the surface type PMOS charge transfer polysilicon electrode. So this second region (P) is a buriedregion inside the

Nsub and just under the first region(N).

## A Pinned Photo Diode of the N+NPNN+ junction type

SONY HAD and PPD are the same thing !

(6) With the first region (N) ,

(7) this second region (P) in the substrate die Nsub makes a light detecting photo diode. which is an NPNsub junction type Pinned Photo Diode.

(8) By applying a proper voltage of one-shot pulse to the Charge Transfer Gate (CTG ) electrode,

(9) the photo signal charge carriers stored in the photo storage region, that is, in the NPN type Pinned Photo Diode,

(10) Are to be transferred to the adjacent shore.

- (10) Are to be transferred to the adjacent charge storage region under the oxide layer of the CTG.

(11) The second storage the CTG and the transferred to the CTG.

- (11) Then, by applying on the CTG electrode different clock voltage, (which is not the oneshot pulse applied before,) the signal charge carriers under the CTG are transferred further along to the nearby charge transfer device (CTD).

This CTD can be either a CCD type or a CMOS type.

(12) Along the front side surface of the region N,

(13) the signal charge carriers are to be transferred to the adjacent CCD type CTD or CMOS type CTD.

(14) The combined solid state image sensor structure, with these features, including all its usage and operations (of the Photo Diode and Charge

Transfer Device defined above ) is in the scope of the patent claims defined above.

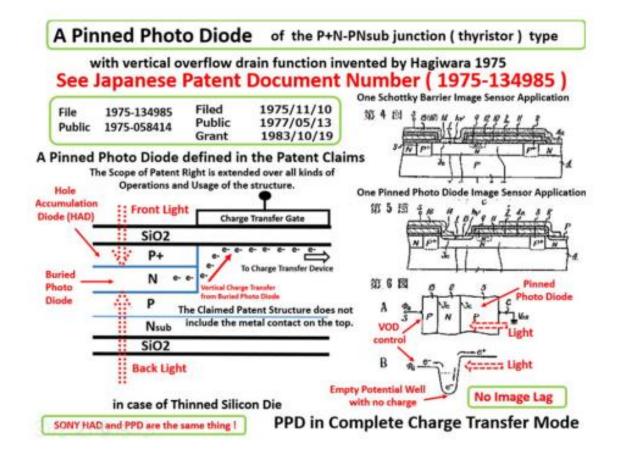

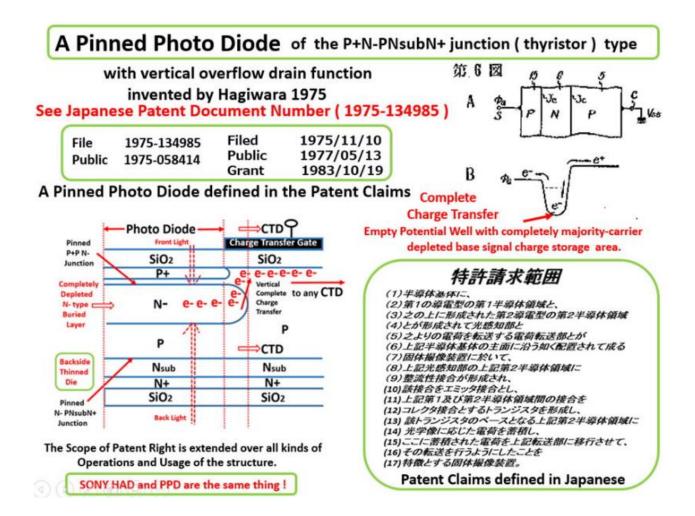

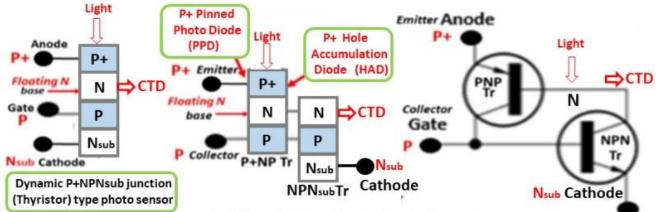

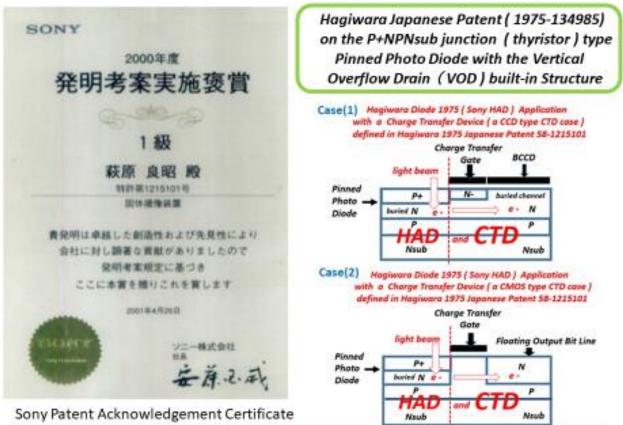

## A Pinned Photo Diode of the P+N-PNsubN+ junction (thyristor) type

with vertical overflow drain function invented by Hagiwara 1975 See Japanese Patent Document Number (1975-134985)

| File<br>Public | 1975-134985<br>1975-058414 | Filed  | 1975/11/10 |  |

|----------------|----------------------------|--------|------------|--|

|                |                            | Public | 1977/05/13 |  |

|                |                            | Grant  | 1983/10/19 |  |

## A Pinned Photo Diode defined in the Patent Claims

The Scope of Patent Right is extended over all kinds of Operations and Usage of the structure.

SONY HAD and PPD are the same thing !

### Patent Claims

(9) another rectifying junction is formed.

A Pinned Photo Diode of the P+N-PNsubN+ junction (thyristor) type with vertical overflow drain function invented by Hagiwara 1975

See Japanese Patent Document Number (1975-134985)

| File<br>Public | 1975-134985<br>1975-058414 | Filed<br>Public<br>Grant | 1975/11/10<br>1977/05/13<br>1983/10/19 |

|----------------|----------------------------|--------------------------|----------------------------------------|

|----------------|----------------------------|--------------------------|----------------------------------------|

| P+P N-                                      | SiO <sub>2</sub> | SiO <sub>2</sub>       |

|---------------------------------------------|------------------|------------------------|

|                                             | P+               | ) e- e- e- e- e-       |

| Completely<br>Depleted<br>N- type<br>Buried | N- e- e-         | e-e-Charge<br>Transfer |

| Layer                                       | Р                | P<br>⇔CTD              |

| Backside                                    | Nsub             | Nsub                   |

| Die                                         | N+               | N+                     |

| Pinned                                      | SiO <sub>2</sub> | SiO2                   |

| N- PNsubN+<br>Junction                      | Back Light       |                        |

The Scope of Patent Right is extended over all kinds of Operations and Usage of the structure.

SONY HAD and PPD are the same thing !

(10) This junction (P+N) can be called as an emitter junction of the P+NP junction type transistor structure for convenience.

- (11) Furthermore the junction (NP) composed of the second region (N) and the first region (N)

- (12) Can be called as a collector junction (NP)

- of the P+NP junction type transistor structure. (13) The second region (N), which can be now

called as the base region of the P+NP junction type photo transistor structure, (14) Is the photo-charge storage area of the

- majority carriers, generated according to the illuminated optical image information.

- (15) After transferring the photo signal charge from the base region (N) to the adjacent charge transfer structure (CTD),

(16) The adjacent charge transfer) structure further performs the subsequent proper charge transfer operations to the final chip outlet.

(17) So-define solid state light detecting sensor structure is in the scope of the patent claims. P+NPNsub junction (Thyristor) Type Photo Sensing Structure invented by Hagiwara in 1975 for the built-in vertical overflow drain (VOD) function and excellent blue light sensitivity with no image lag.

Pinned Photo Diode (PPD) and Sony original Hole Accumulation Diode (HAD),

patented by Hagiwara at SONY in 1975 Japanese Patent (JAP 50-134985), originally defined as a dynamic photo sensing P+NPNsub junction Structure with the storage electron charge in the base N region to be transferred completely, from the N charge storage region in complete majority-carrier depletion mode, to the adjacent charge transfer device (CTD) to realize no image lag pictures.

The adjacent CTD can be historically a simple classical MOS image sensor, Bucket Brigate(BBD) type image sensor, Frame Transfer type CCD imager, Interline Transfer type CCD imager, or current CMOS technology active image sensor.

PPD and Sony HAD are the same thing, both invented by Hagiwara at Sony in 1975.

Hagiwara at Sony invented the pinned photo diode 1975. See the JAPANESE PATENT, JAP 50-134985, 1975.

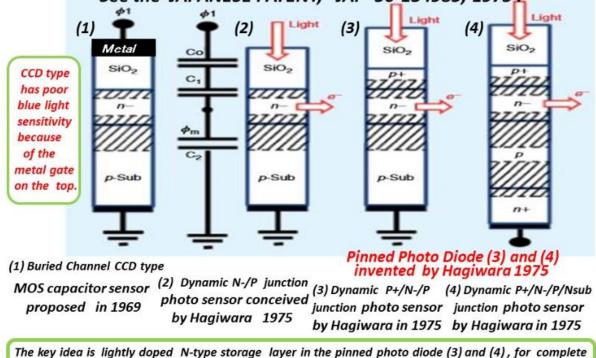

charge transfer with no image lag, similar to the lightly doped N- type buried layer of BCCD of type(1).

Reference: IEEE Solid-STATE CIRCUITS MAGAZINE, SUMMER 2013 issue, pp. 6

Charge-Coupled Devices and Applications

Daiman

Lewis M. Terman

Substantial to the importance of the charge-transfer phenomenon is arbitrary to the the Boyce B, Labourne and the Stack A, Samuell Assertio and the page to the important of the charge-coupled and bocket import design association. However, the pages in the pages interactions to the forum:

Despinação desse en uniça since principar e estar, la el obei deste antesteres insultanas, despis successiva en extente est time caté in despia canadice es asses divinal o testor in sub can in monite e apre singe to

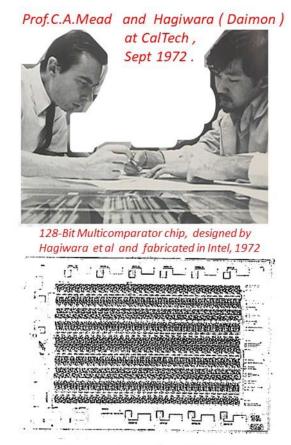

My PhD thesis paper on buried channel CCD at ISSCC1974, in Philadelphia, USA

Prof. T. C. McGill

Prof. C. A. Mead

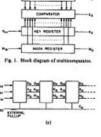

### 128-Bit Multicomparator

CARVER A. NEAD, RICHARD D. PASHLEY, MEMBER, IEEE, LEE D. BRITTON, YOSHIAKI T. DAIMON, AND STEWART F. SANDO, JR., MEMBER, IEEE

npars function. The o ter with en a 107 × 15 g 3350

INTRODUCTION IN

circuit consists of three independently choiced static-tis shift neglister with associated RECULUIY-2-cone gui-la operation, the device indicates a match between the word and the summissed bits of the key word. The renti-mator is loaded with a key word by serially shifting the into the key register and looking the register in static While the key word is being loaded, the comparator is of by enstring zeros<sup>1</sup> in the appropriate locations of the

nationality residend March 15, 1976; recised July 18, 1976. C. A. Marel is with the Colliners longitude of Technology, Fanderse, 26, 2112. Santa Class, C.A. L. B. Bolton is with the Hereder-Koole Laboratoria, Cupartias, C.A. D. Bolton is with the Hereder-Koole Laboratoria, Cupartias, C.A. Values, C.A.

see is with the Sany Corporation, Tokyo, Jopun. committion: high="1"=" $P_{OC}$ , low="4"=" $P_{OC}$ . Note that is negative for p-channel HOS and positive for nHOS andrian logic (TTL) levels may or may not have revenue waiting role proceedings uncel.

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. SCI1, NO. 5, OCTOBER 1978

Fig. 2. P (1) Ca

mask register. Marking allows the multicomparator to search for bit strings of varying length and composition. For example, summe it is occessary to search for all words containing a specific 113-bit cocks. By entering the 113-bit cock in the key ingenter and masking out the rest of the comparator, the multi-comparator is conformed to search for this cock wherever it occurs in the data file. Once the multicomparator is loaded with "key" and "mask" words, the file being searched is enaily shifted brough the data ten negitor. The data words are compared in bit peaked with the summated bits of the key word at they pass through the data negitor. When smith is found, the compare output gots high. Lengt multicomparators can be constructed of the 128-bit

norm, an compare output post high. Large multicomparators can be constructed of the 128-bit icritics. Cascide [Fig. 2(s)], the comparator can be used to march for words longer than 128 bits. By implementing multi-comparators in parallel [Fig. 2(b)], a word-setial, bit-parallel

Ref: IEEE Journal of Solid State Circuits, VOL.SC11, No.4, October 1976

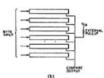

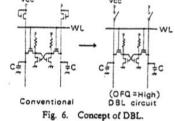

### ISSCC1989 Paper on Sony 4 M bit Fast Cache SRAM for Digital Image Sensor

#### A 25-ns 4-Mbit CMOS SRAM with 50 -1/1/ Dynamic Bit-Line Loads ≠c FUMIO MIYAJI, YASUSHI MATSUYAMA, YOSHIKAZU KANAISHI, c₽ KATSUNORI SENOH, TAKASHI EMORI, AND YOSHIAKI HAGIWARA, MEMBER, IEEE Conventional -A 25-ns 4-Mbit CMOS SRAM with 512K word×8-bit orga-BUFFER REDUNDANCY CLOCK GEN. has been developed. The RAM was fabricated using a 0.5-µm and double-aluminum CMOS technology and was assem 400-mil DIP. A small cell size of 3.6×5.875 µm<sup>2</sup> and a chip g ž LINE LOAD TYNAMIC B 146×17.41 mm<sup>2</sup> were obtained. A fast address access time of 25 ATD single 3.3-V supply voltage has been achieved using our newly CELL ARRAY

dynamic bit-line load (DBL) circuit scheme incorporated with an ransition detector (ATD), divided word-line structure (DWL), re sense amplifier, and low-noise output circuit approach. A low current of 46 mA at 40 MHz and low standby currents of 70  $\mu$ A 5 µA (CMOS) were also attained.

I. INTRODUCTION

E MEMORY capacity of SRAM's has quadrupled

BUFFER CLOCK GEN. 7,12,14 ROW ADD. BU -DECODER BUFFER 2 L/01 ROW SWL DRIVER -51,11,11.84 ADD. WRITE DRIVER 10N (8/ DEC.) 8/A Fig. 1. Block diagram of the RAM.

See also Journal of the Solid State Circuits, Vol. 24, No.5, October 1989

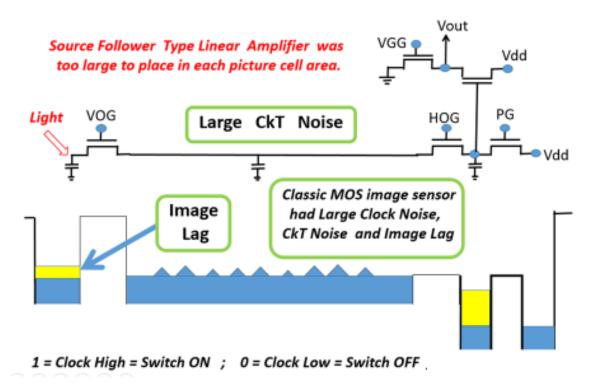

### Classic MOS image sensor type Charge Transfer Device (CTD)

228

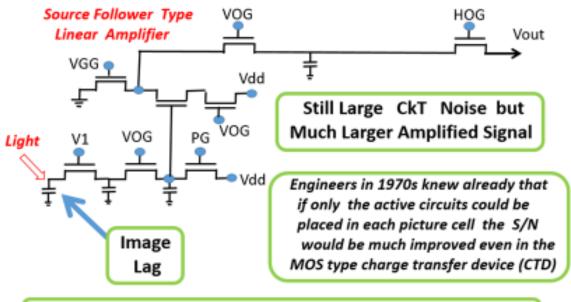

### Active Pixel Type CMOS image sensor type Charge Transfer Device (CTD)

But we have to sacrifice the picture cell light detecting window area. The only Solution would be the back light illumination with thinned die.

### Hagiwara Patent (1975 – 127947) invention already gave the solution with the Image Lag Free Pinned Photo Diode with Back Light Illumination.

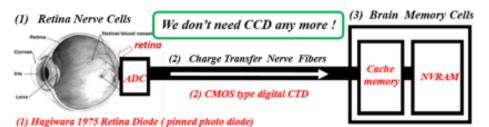

# **Digital CMOS image sensor**

is made of (1) Pinned Photo Diode (2) Charge Transfer Device(CTD) (3) A/D converter (4) Fast Cache SRAM and (5) Slow Nonvolatile RAM

Pinned Photo Diode for DCIS was invented by Hagiwara in 1975. Back illuminated CMOS image sensor was developed by Sony Engineers First A/D converter for DCIS was first developed by Sony Engineers. First Cache 4M bit SRAM for DCIS was developed by Hagiwara in 1989. First Nonvolatile RAM for DCIS was invented by Prof. Simon Sze in 1966.

already knew the conventional Source Follower Type Active Picture Element Cell (Pixell) Photo Diode, by the analogy of DRAM cases as shown above. Nothing is new about the Active Picture Element Cell (Pixell) Photo Diode CMOS image sensor.

| Comparison of four types of Light Detecting Sensor Structures |                    |      |      |                       |  |

|---------------------------------------------------------------|--------------------|------|------|-----------------------|--|

| feature                                                       | N+P <sub>sub</sub> | SCCD | BCCD | P+N-PN <sub>sub</sub> |  |

| Sensitivity                                                   | 0                  | Х    | Х    | 0                     |  |

| Image Lag                                                     | Х                  | 0    | 0    | 0                     |  |

| Surface Dark Current                                          | Х                  | Х    | Х    | 0                     |  |

| Surface Trap Noise                                            | Х                  | Х    | 0    | 0                     |  |

| Vertical OFD Function                                         | Х                  | Х    | Х    | 0                     |  |

## Hagiwara invented the P+N-PNsub type Pinned Photo Diode See Japanese Patents (JA 1975-127647) and (JA 1975-134985)

The Pinned Photo Diode is much better than the CCD type light detector. The Active Pixell CMOS type DIGITAL CTD is much better than the CCD type ANALOG CTD.

In the total performance, CMOS Image sensor in digital system is considered to be much better than CCD image sensor in analog charge transfer system now.

238

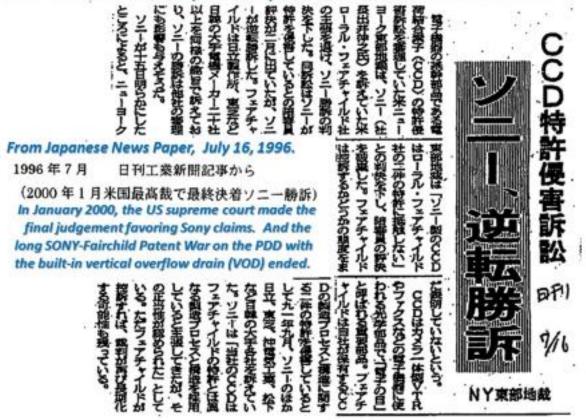

## Fairchild\_to\_Sony\_Patent\_War\_1991\_to2000

### SONY- Fairchild Patent War (1991-2001) on Pinned Photo Diode with Vertical OFD

Fairchild Early Patent on CCD sensor with vertical OFD protection USP3896485 ( July 22, 1975 )

Fairchild Early Patent, filed on July 22, 1975, applied on the surface CCD type MOS capacitance with poor blue sensitivity while Sony Hagiwara Patent, filed on Nov. 10, 1975, appiled on the Pinned Photo Diode, with good blue sensitivity and low dark current also with the built-in vertical overflow drain function, which was well known as the P+NPNsub Thyristor Punch-Thru action. Sony took more than ten years in this Patent War to challenge to explain the differences on the two image sensor structures and the two vertical overflow drain sturctures to the authorities who did not have any backgrounds on the semiconductor device physics.

Sony Hagiwara Patent on Pinned Photo Diode

with P+NPNsub Thyristor type vertical OFD protection

JAP50-134985 (November 10, 1975)

with a Charge Transfer Device ( a CMOS type CTD cose ) defined in Hagiwara 1975 Japanese Patent 58-1215101 Charge Transfer

See Hagiwara Japanese Patent Application (50-134985, 1975)

SONY- Fairchild Patent War (1991-2000) on Pinned Photo Diode with Vertical OFD

## Sony\_Top\_Managements\_finally\_acknowledged\_Hagiwara

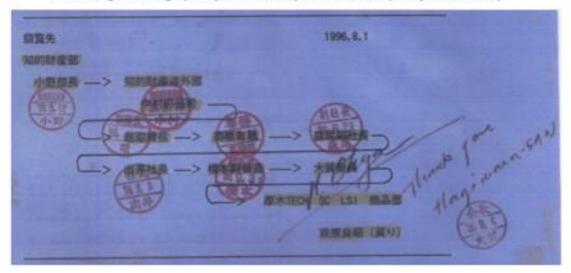

Sony won the Fairchild-Sony Patent War in the 1996 New York State Court, and Hagiwara received a Thank\_YOU\_NOTE from SONY TOP Managements, including Mr.Ohga(Sony Chairman) and Mr.Idei (Sony President).

The final US Supreme Court decision was made in 2000, finally after ten years of pains.

Hagiwara protected SONY Image Sensor Business by Hagiwara 1975 patents on the Pinned Photo Diode with the vertical Overflow Drain Structure.

Sony\_Top\_Managements\_finally\_acknowledged\_Hagiwara\_1975\_Patents\_on\_PPD.

given to Hagiwara in 2000 after the patent-war.

## Fossum 2014 fake paper attacking Hagiwara Patents

(19) 1975, Hagiwara application on bipolar structures for CCDs in which a pup vertical structure was disclosed, among several structures [24]. The top p layer was connected by metal to a bias used to control full-well (4) capacity and the stype base layer was proposed for carrier storage. In an universal paper, Hagiwara, in 1996, revisited the 1975 invention and claimed it was essentially the invention of both the virtual phase CCD and the NEC low-lag structures, as well as the basis of the Sony so-called "Hole Accumulation Diode," or HAD structure [25]. However, the 1975 application did not address complete charge transfer, lag or anti-blooming properties found in the NEC low-lag device, and does not (7) seem to contain the built-in potential step and charge transfer device aspects of the virtual-phase CCD. Hagiwara repeats these claims in a 2001 paper [26] and shows a VOD structure that is not found in the 1975 patent application. Sony did not seem to pursue the HAD structure until well a (9) NEC paper was published. However, the "narrow-gate" CCD with an open p-type surface region for improved QE also disclosed in the 1975 application was reported in more detail by Hagiwara et al. at Sony in 1978 [27]. A similar structure was used extensively by Philips [28].

## This is a fake paper.

These (1) thru (9) statements are all biased and false. Many corrections are requested Fossum is insulting Hagiwara and SONY by making many false statements.

This is the most serious false statement.

Yes, Hagiwara 1975 addressed the Complete Charge Transfer and Image Lag and anti-blooming, by drawings of Fig.5 and Fig.6 in Hagiwara 1975 patent on the original pinned photo diode.

Evidently, Fossum has never seen Hagiwara 1975 patent. In Fossum 2014 biased fake paper, Fossum did not quote the Fig.5 and Fig.6 of 1975 Hagiwara Patent invention

See Hagiwara Japanese Patent Application (50-134985, 1975)

Hagiwara believes that

Hagiwara invented it, in the Japanese 1975 patent (1975-134985) as the P+NPNsub junction (Thyristor) type Light Detecting Picture Cell Structure, and Sony diligent engineers, including Hagiwara, developed, the stitching technology for large area image sensors. SONY called it as the SONY original HAD sensor technology in SONY business. Naturally, the technical world did not use the SONY business Brand Name HAD, and called it by another name, the Pinned Photo Diode. But the Pinned Photo Diode and SONY original HAD technology are the same thing, both invented by Hagiwara in 1975.

At least, Teranishi did not invent the Pinned Photo Diode. Hagiwara is the inventor of the Pinned Photo Diode.

Sony diligent engineers developed and now Sony owns the world record in low-noise in the voltage domain for CMOS Image Sensor (CIS) with the Pinned Photo Diode with the Back Light Illumination, that was also invented by Hagiwara of SONY in 1975 the Japanese 1975 patent (1975-127647).

At least, Fossum is not the inventor of the active image sensor picture element.Peter Noble is the inventor of the active image sensor picture element. http://www.pjwn.co.uk/

In the Fossum 2014 fake paper, Fossum attacked Hagiwara 1975 patent with lies, insulting Sony and Hagiwara honor and pride on purpose. I could not understand Fossum motivation. But I am now convinced that Fossum wanted Fossum himself to be recognized by the world, with false explanations on Fossum friend Teranishi as the TRUE inventor of the Pinned Photo Diode, NOT Hagiwara.

Fossum wanted to convince the world that Fossum himself developed the modern CMOS digital camera. But now I understand that Peter and SONY diligent engineers, including Hagiwara. This is not fair at all. It is all lies. The world should know the truth.

Until last June I did not know what is the Pinned Photo Diode. I knew SONY HAD. But I did not know myself that SONY HAD and the Pinned Photo Diode are the same thing. My friends in Sony informed me that Teranish received awards from Queen Elizabeth and Japanese Emperor as the inventor of the Pinned Photo Diode. SONY diligent engineers were not happy at all. So I began to study what is Pinned Photo Diode last June. Then I found the Fossum 2014 fake paper.

Besides, SONY won the SONY-NEC Patent war by Hagiwara 1975 patent against the Teranishi1979 patent a long time ago. So Teranish should know that Hagiwara is the inventor even though Teranishi published his work in IEDM1982. Teranishi work was just a copy of Hagiwara 1975 patents that defined as one example case of Interline CCD image sensor with the complete charge transfer mode ( no image lag ) P+NPNsub junction type photon detector structure, which is now called as the Pinned Photo diode.

But it is now more than four years after Fossum 2014 fake paper publication. I found this fake paper, really too late. I was very, very late since I do not belong to the image sensor community any more.

Yes, with my interests in the intelligent image sensors included, but my current major interests are in the AIP (Artificial Intelligent Partner) systems, including AI software and AI digital circuit system applications.

I try to be calm, but cannot be silent. I feel that the world should know, at least, what is the truth. I don't think I can change the past history. But people can learn the truth anytime, now and in future. Yes, many people contributed. Their diligence and efforts must be much worth recognitions.

$http://www.aiplab.com/Hagiwara\_at\_Sony\_is\_the\_true\_inventor\_of\_Pinned\_Photo\_Diode.html$

http://www.aiplab.com/Story\_of\_Pinned\_Photo\_Diode.html

http://www.aiplab.com/