***************************************************

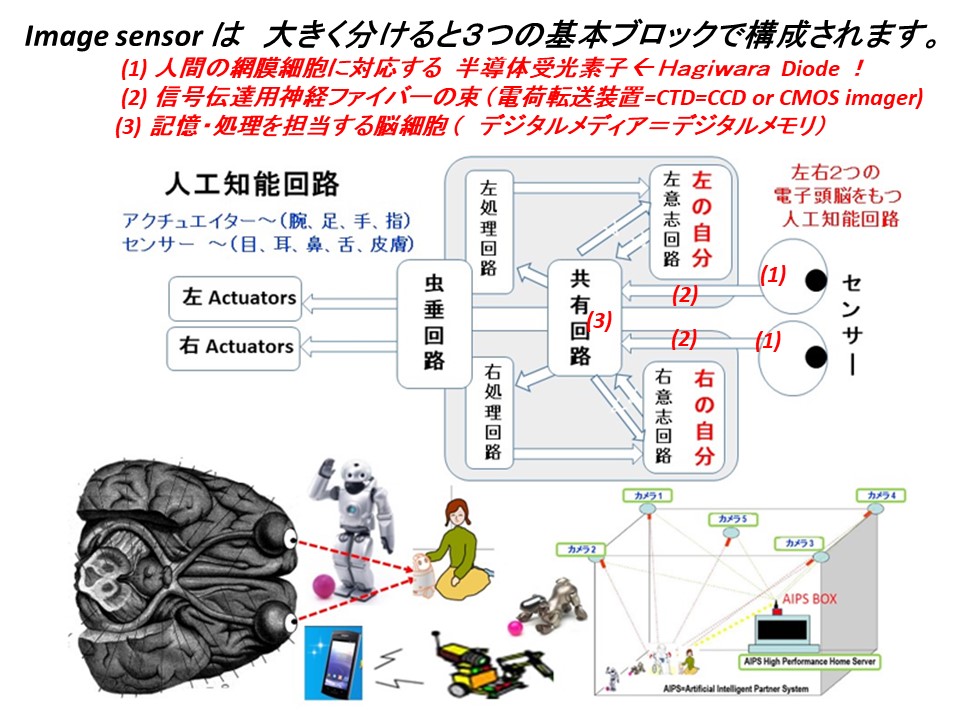

The AIPS ( Artificial Intelligent Partner System ) Home Page

................. a story of the intelligent AIPS image sensor..............

***************************************************

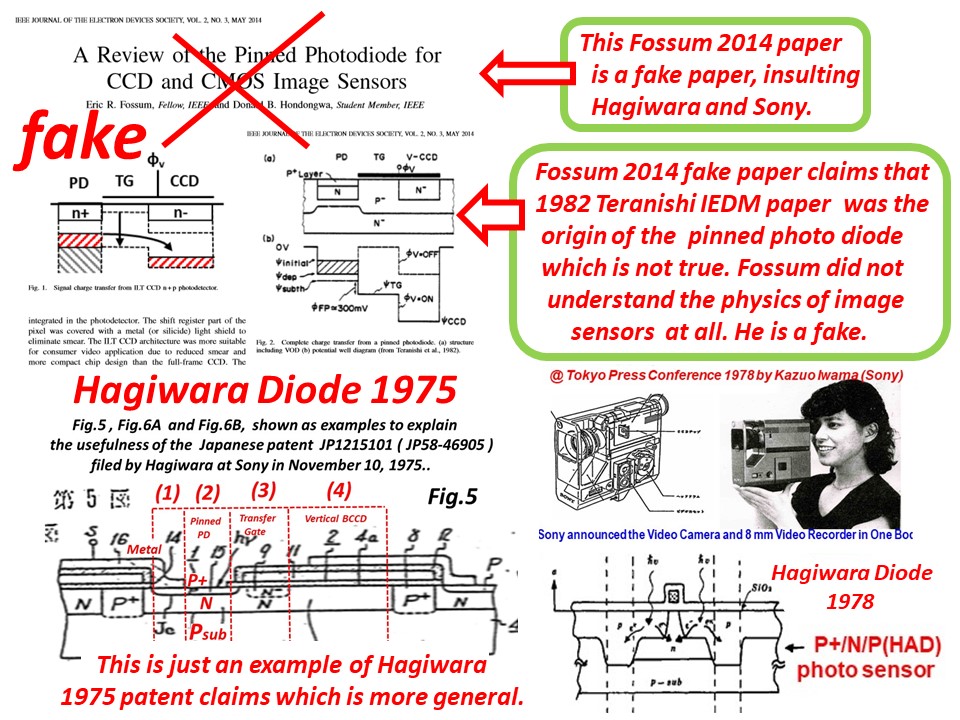

Fossum is a liar !

i

**********************************************************************

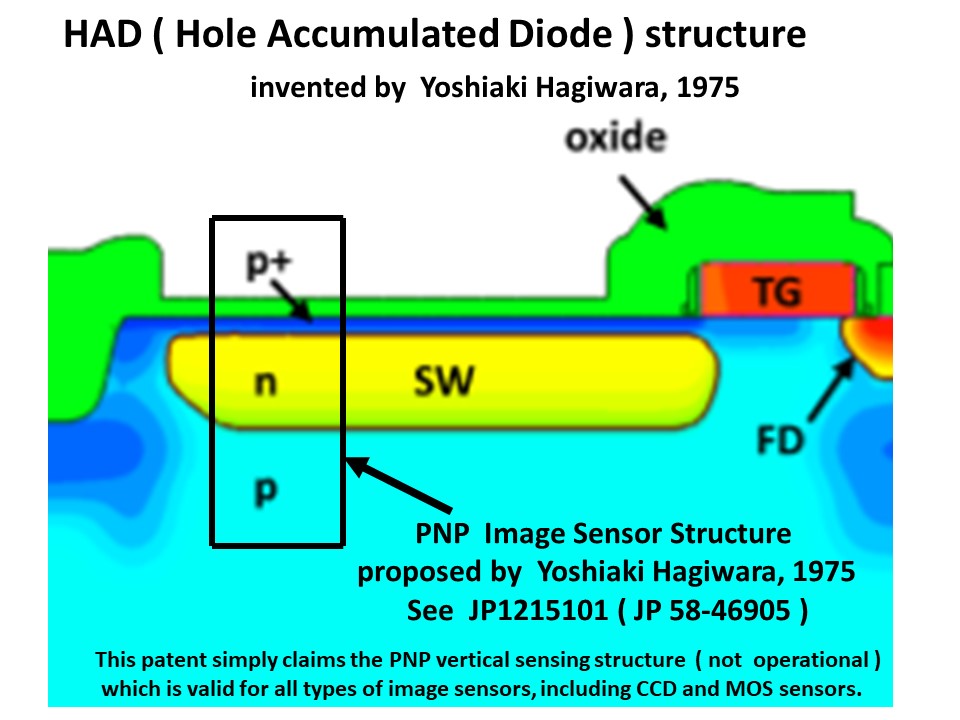

SONY HAD sensor の秘話

SONY HAD sensor の特許戦争の秘話

The evience of the fact that Hagiwara invented pinned photo diode

********************************************************************

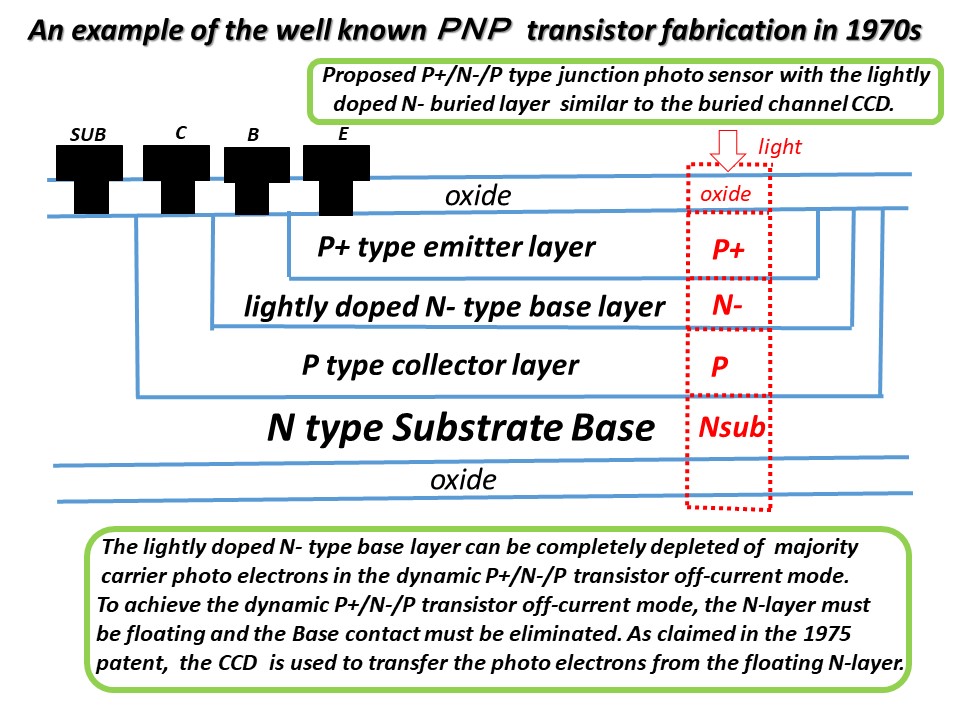

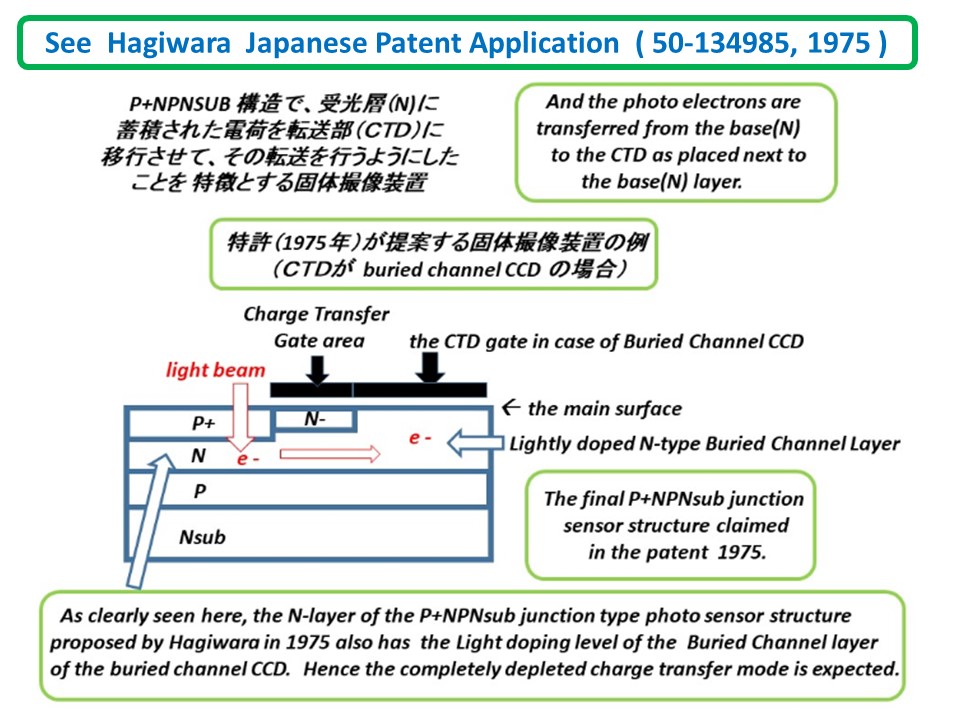

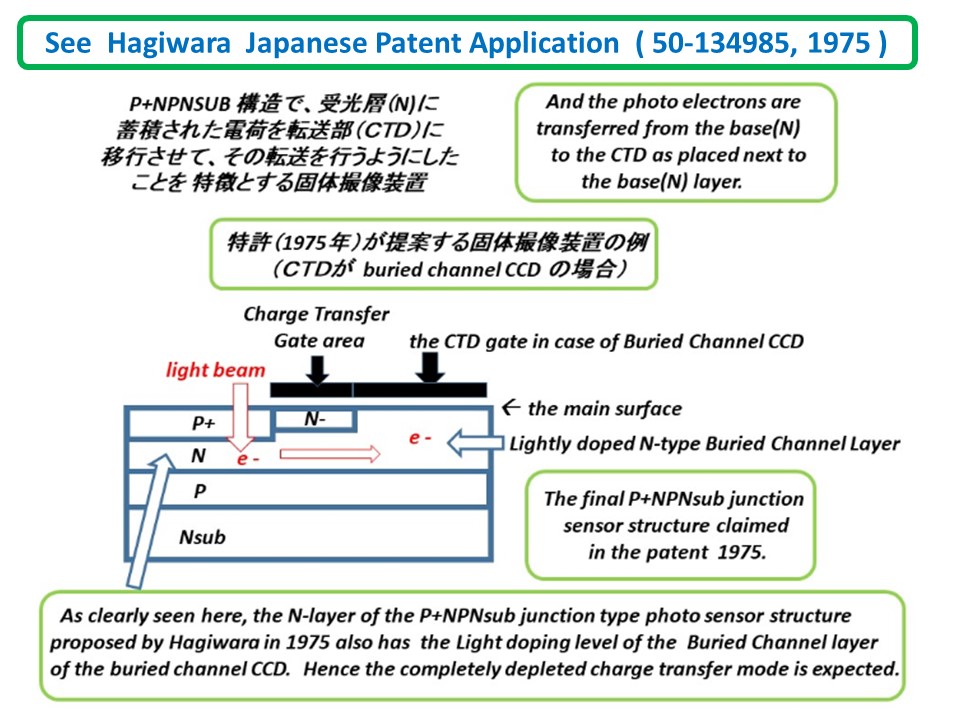

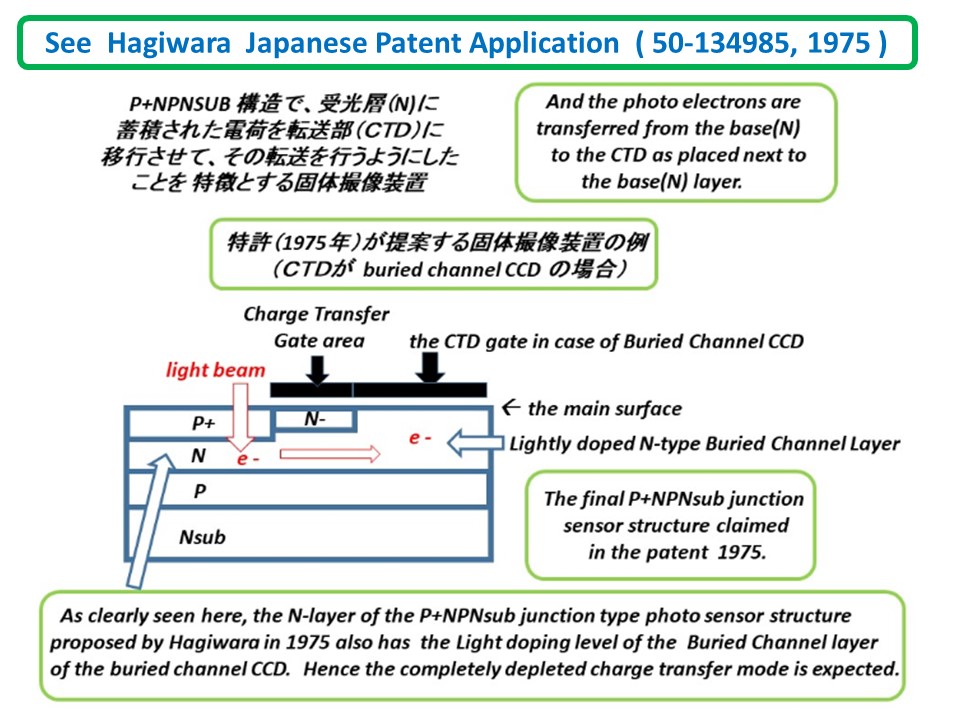

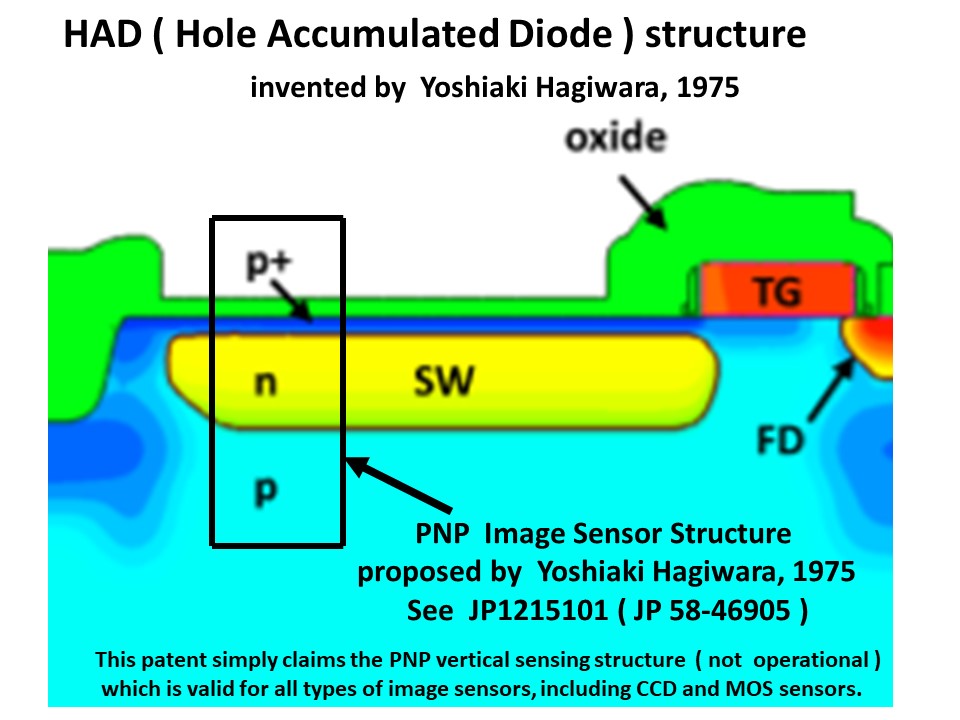

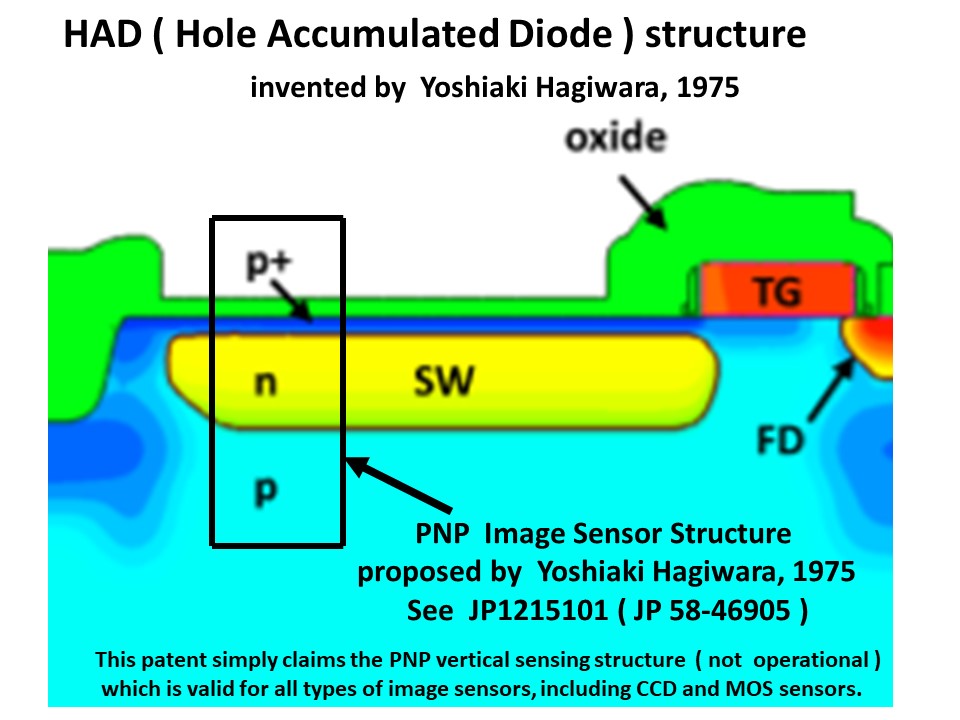

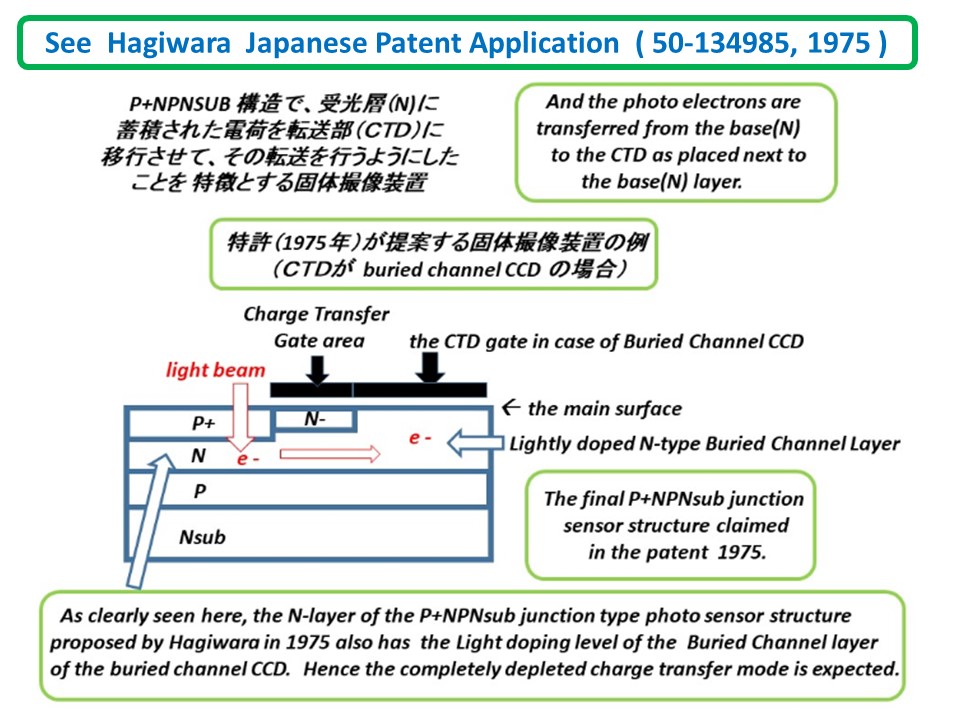

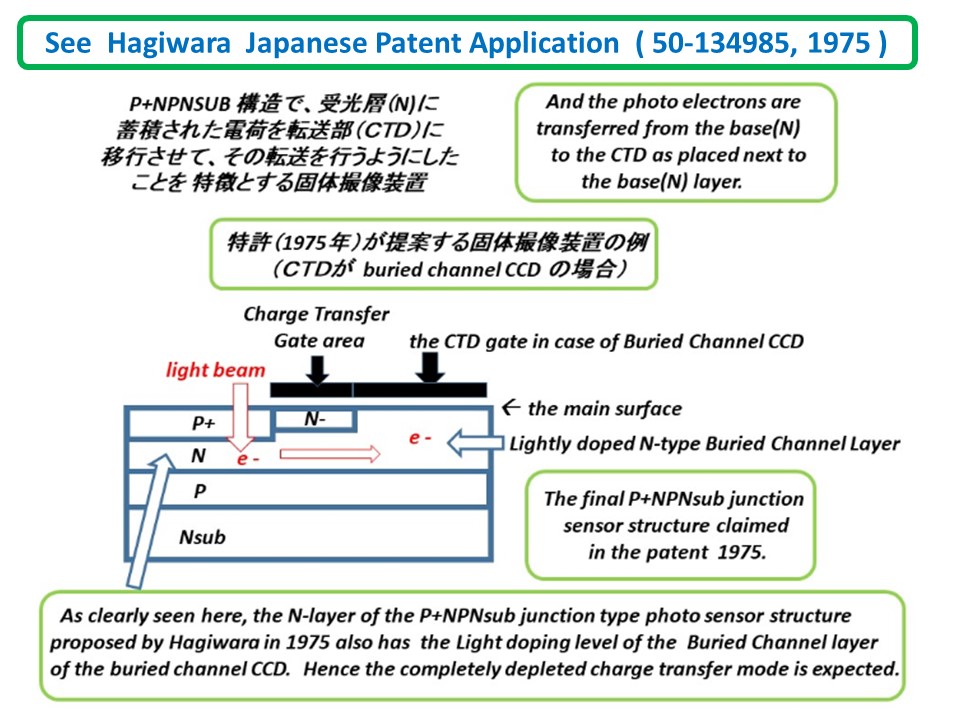

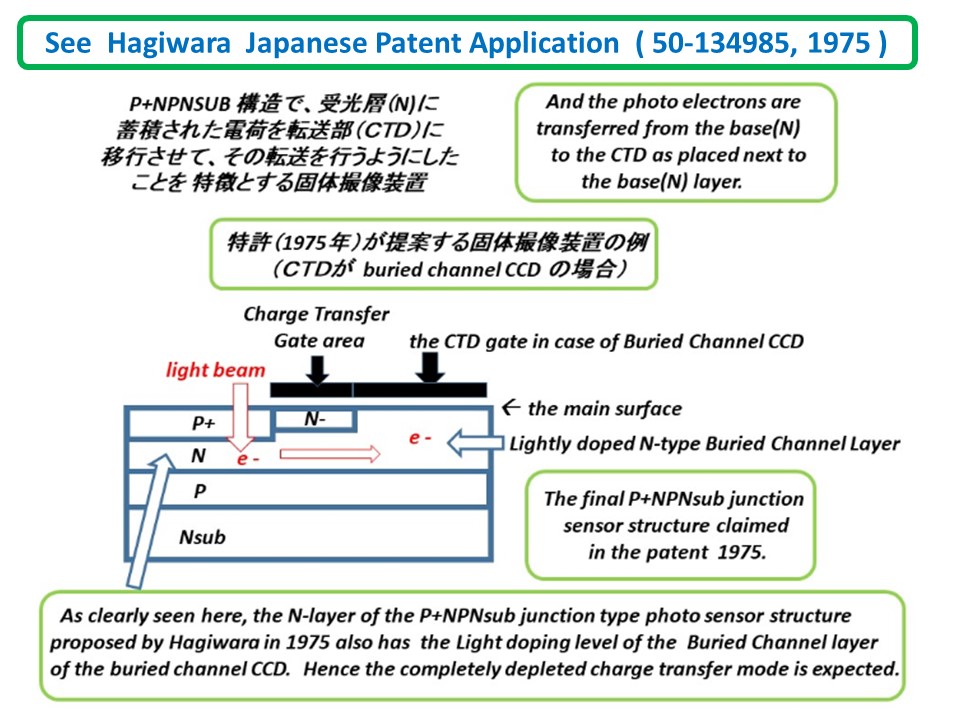

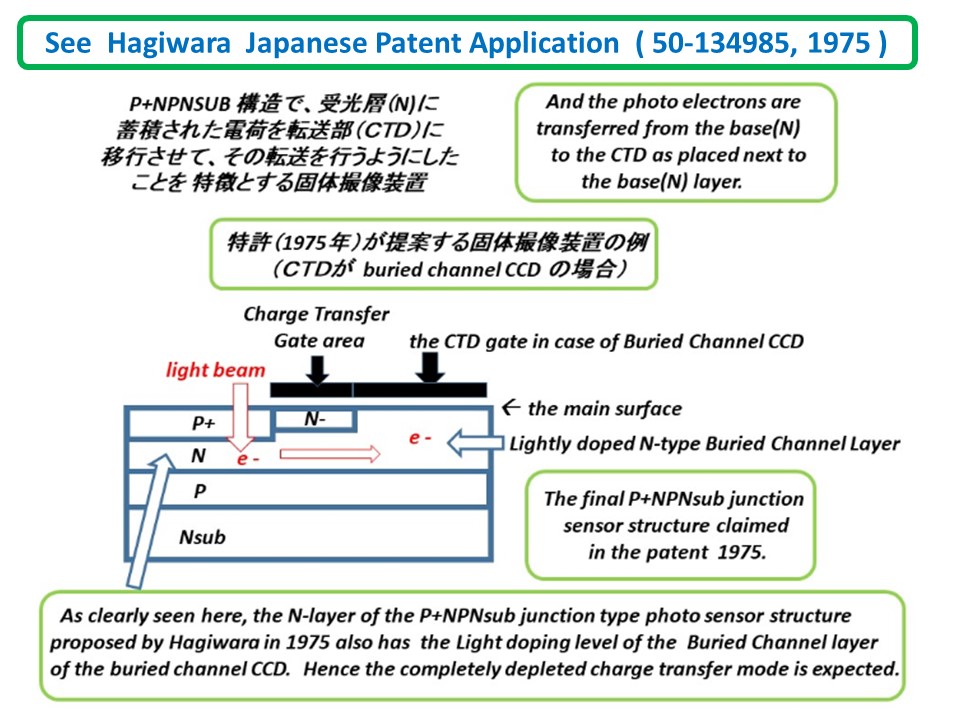

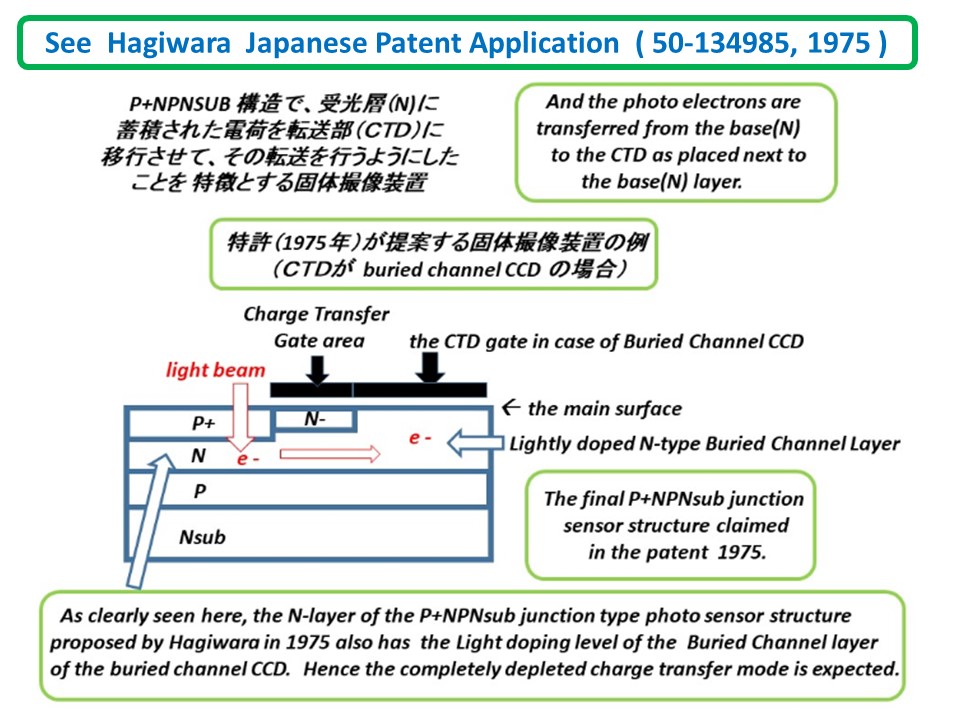

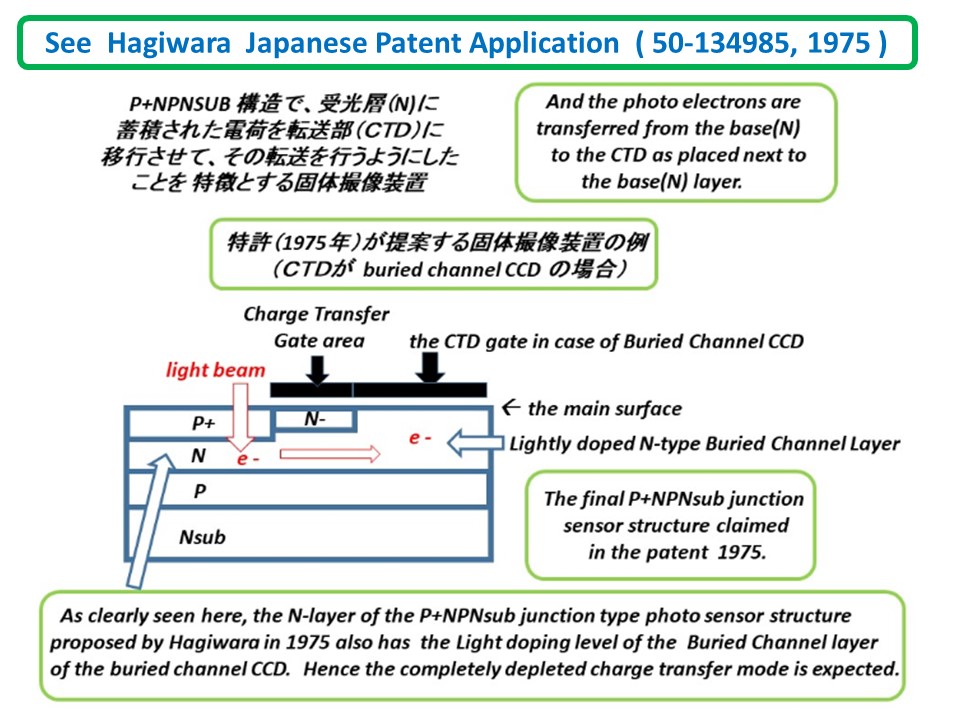

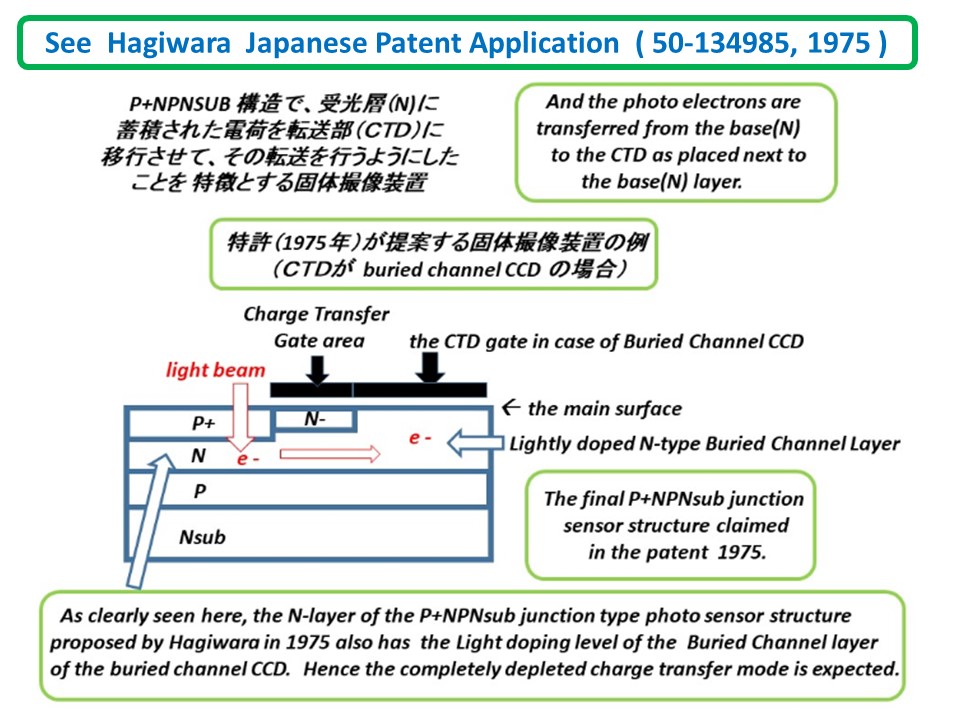

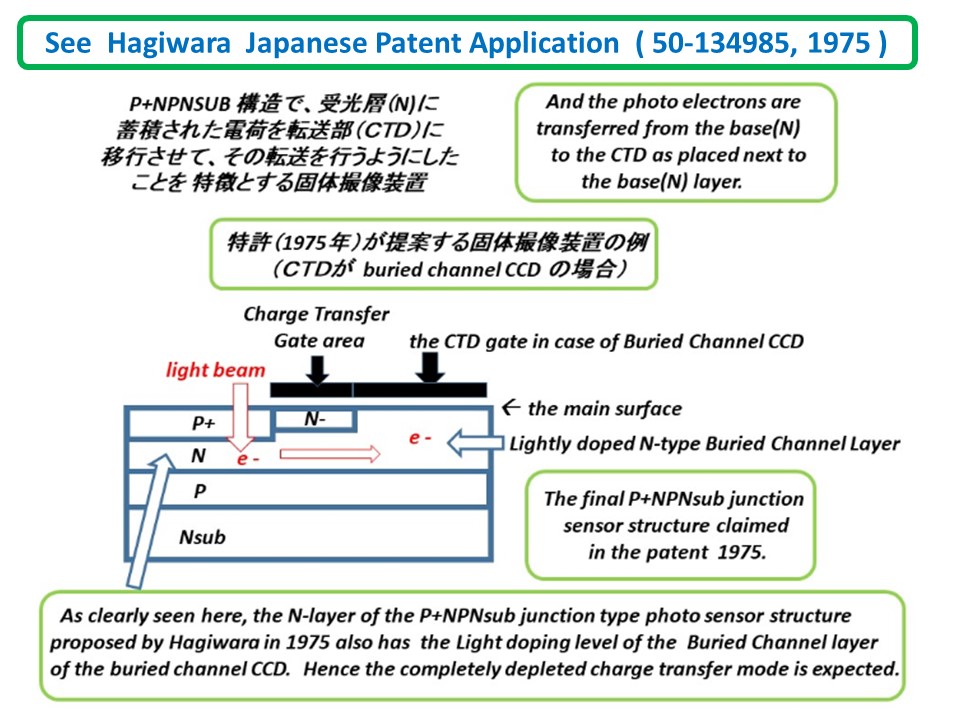

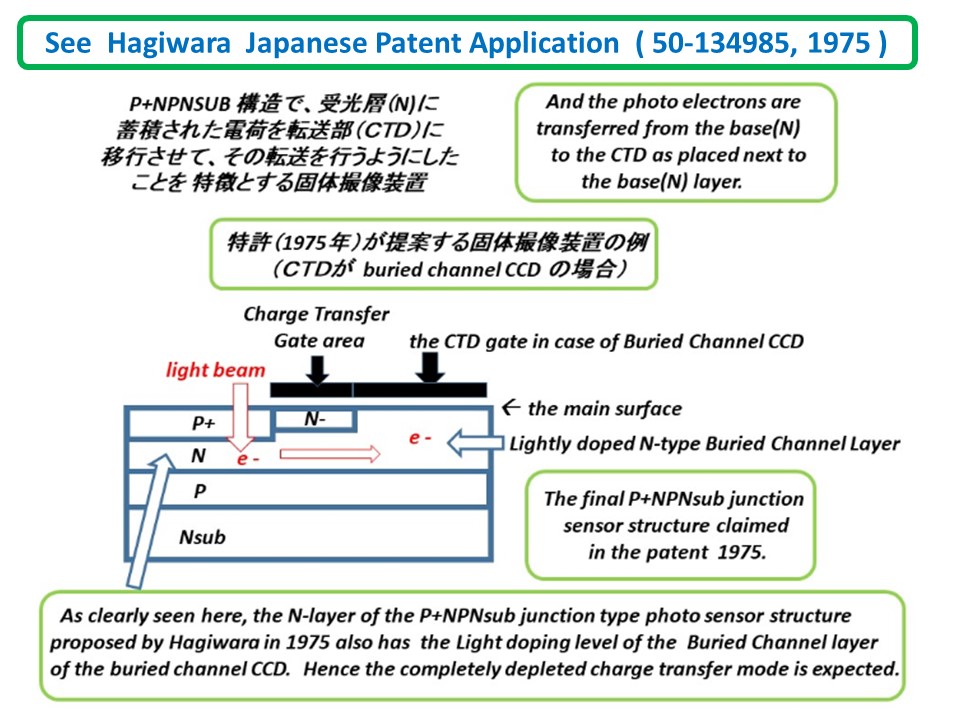

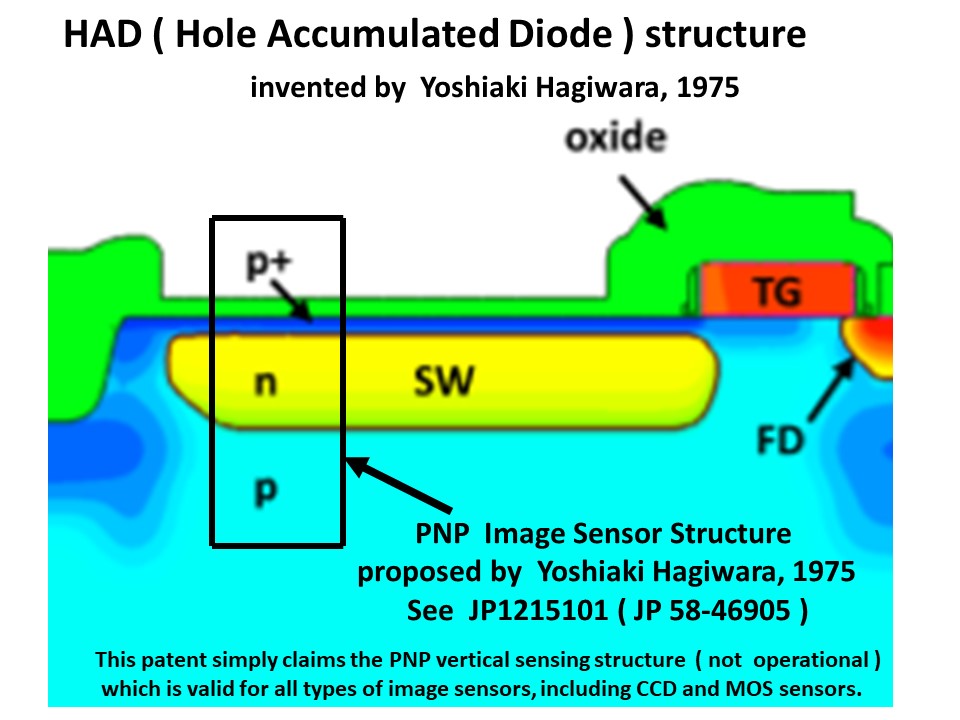

Sony に1975年に入社し、すぐに萩原は受光素子の構造特許

を出しました。 HAD+CTD の構造特許です。すなわち、

HADで光電変換してHADに蓄積した信号電荷(電子)をCTD

にCCD転送の様に完全空乏化・完全電荷転送( complete

charge transfer from completed depleted empty potential well )

して、隣接する CTD ( CCDも, BBDも, MOS type CTD もCTD

です、CTDはどれでもよい)に転送を可能とする構造特許です。

萩原が考案し、構造特許として、1975年に特許申請し、その特許

請求範囲で定義された受光素子構造図を下図に示します。

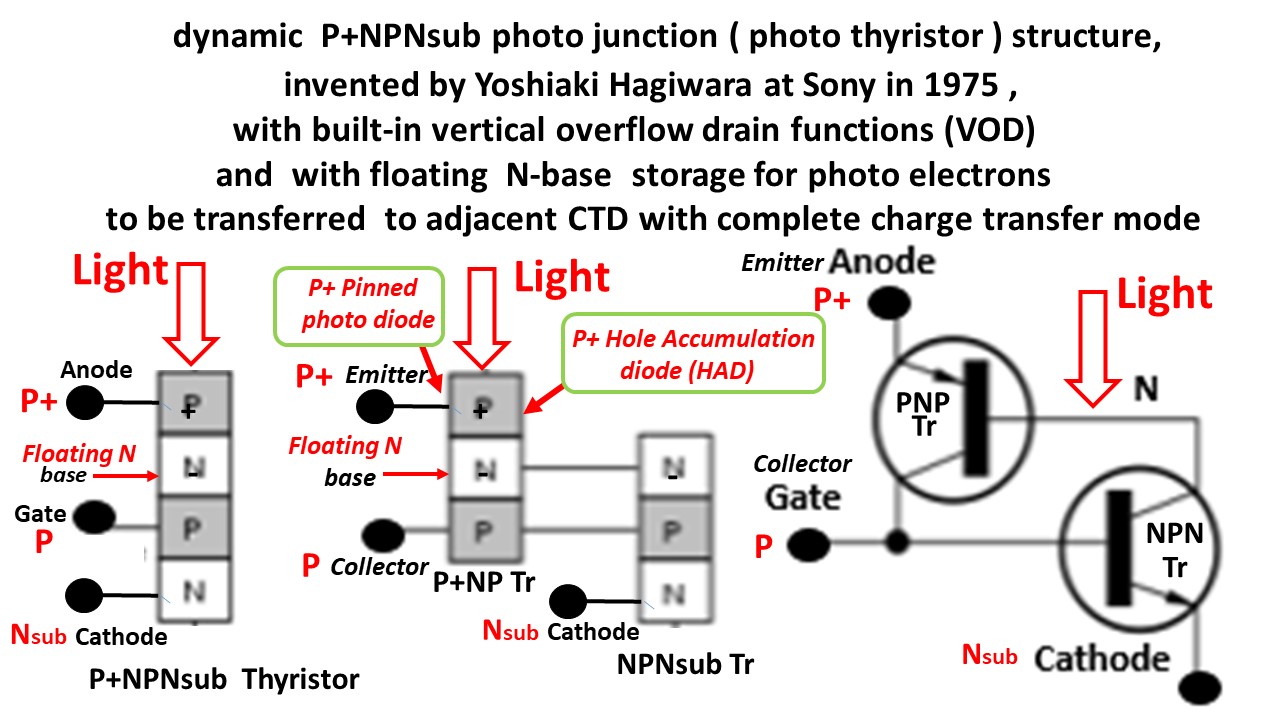

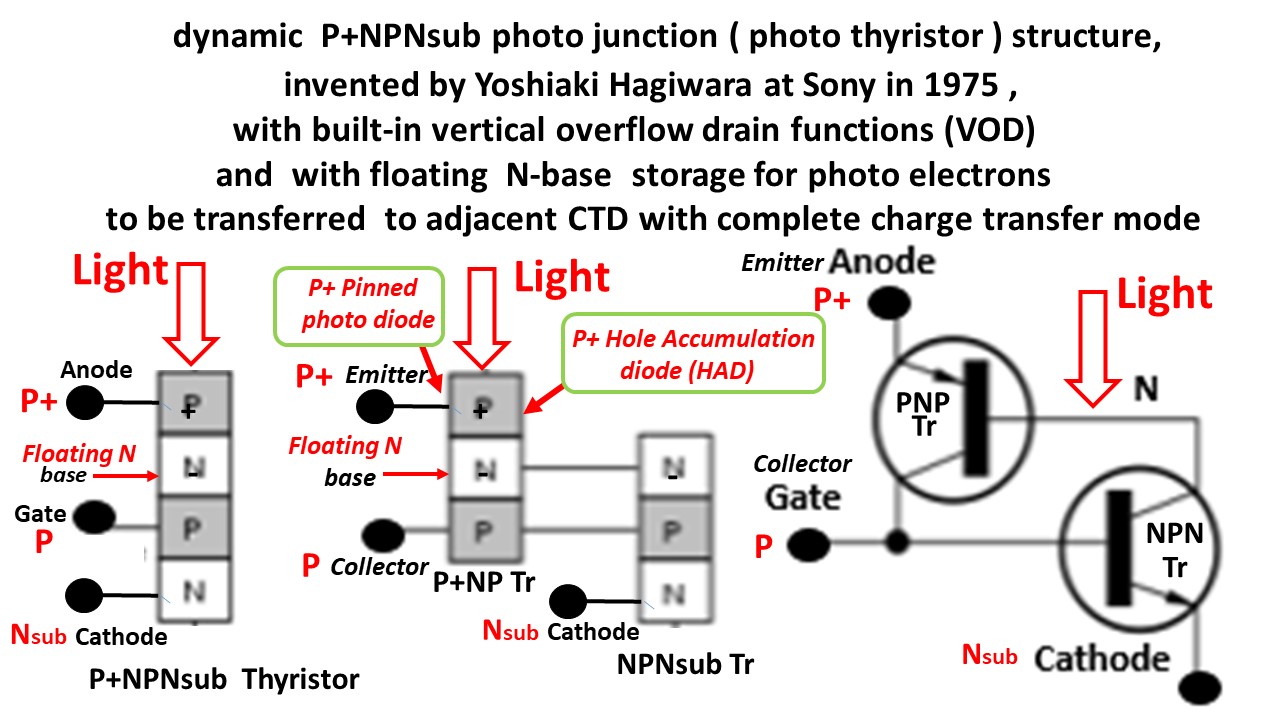

簡単なP+NPNsub接合(thyristor)の構造体で、

この図を特許に添付しなかったのが今問題になっています。

この図では PNP Tr の emitter 端子(P+ 領域)には

Anode 端子が接続され、外部電圧で、P+領域の電圧は

外部から固定(ピンとめ)されています。

これが pinned photo diode の言葉の由来です。

Thyrisor defined in wikipedia

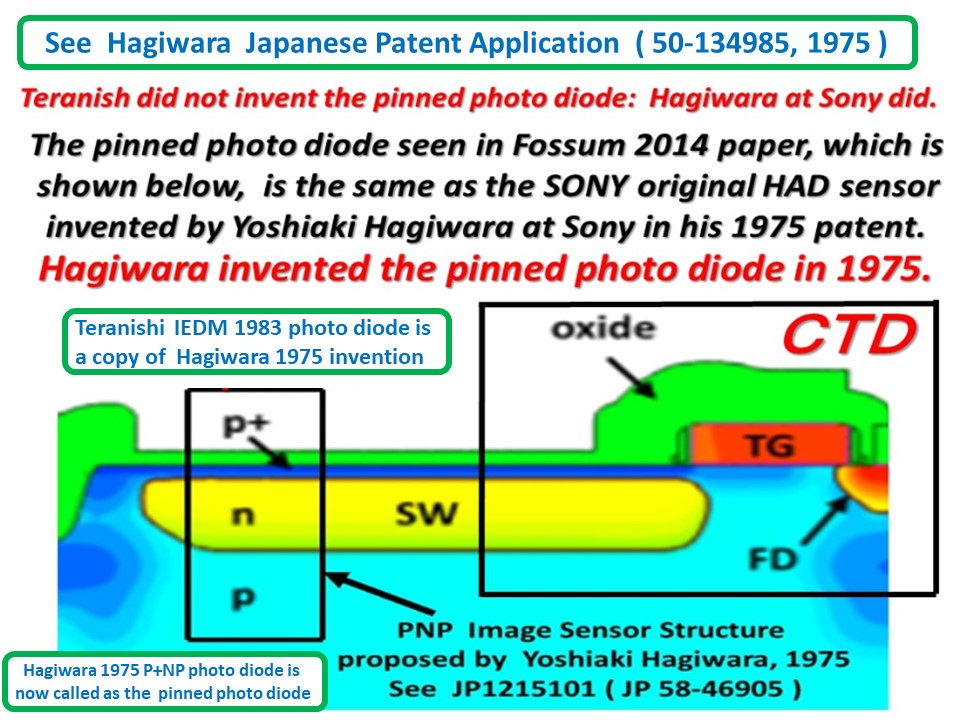

Hagiwara at Sony invented the pinned photo diode in 1975

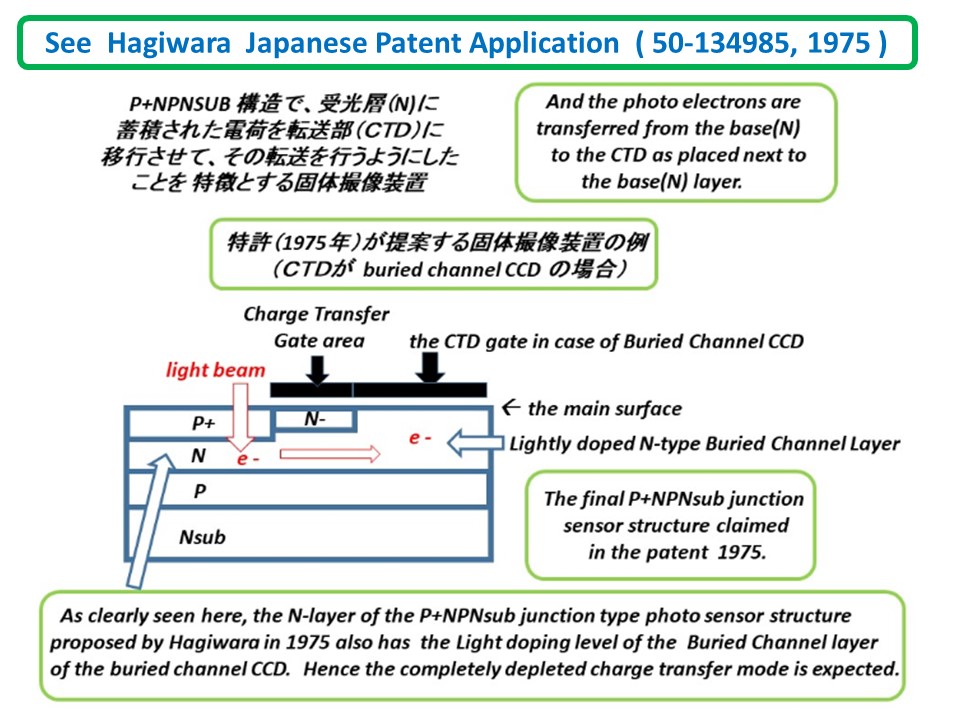

Hagiwara at Sony filed a Japanese patent in 1975.

The world does not know the empty potential well

Hagiwara drew for the first time in the wotld

in his 1975 patent

which implies the complete charge transfer mode

of the pinned photo diode,

the evidence of the fact that

Hagiwara at Sony

invented in 1975

the pinned photo diode.

Fossum was not aware of

Hagiwara's empty potential well,

Fossum led to a false conclusion

that confused the world

by his irresponsible paper

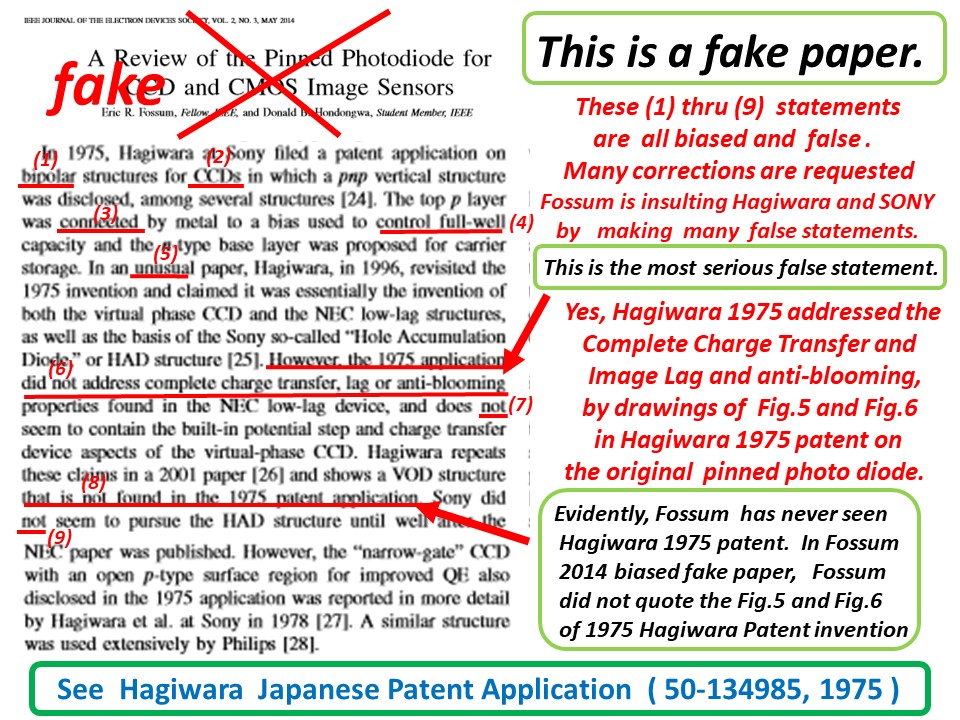

" A Review of the Pinned Photodiode for CCD and CMOS Image Sensors"

by Eric R. Fossum and Donald B. Hondongwa , which was published in

IEEE JOURNAL OF THE ELECTRON DEVICES SOCIETY, VOL. 2, NO. 3, MAY 2014

Corrections are requested in his paper..

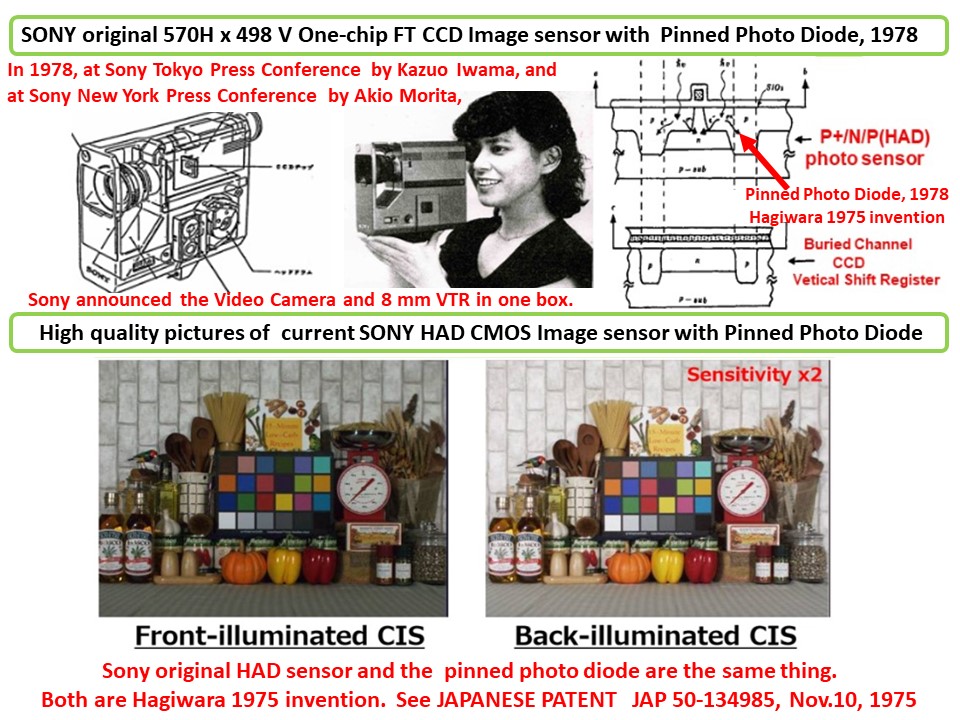

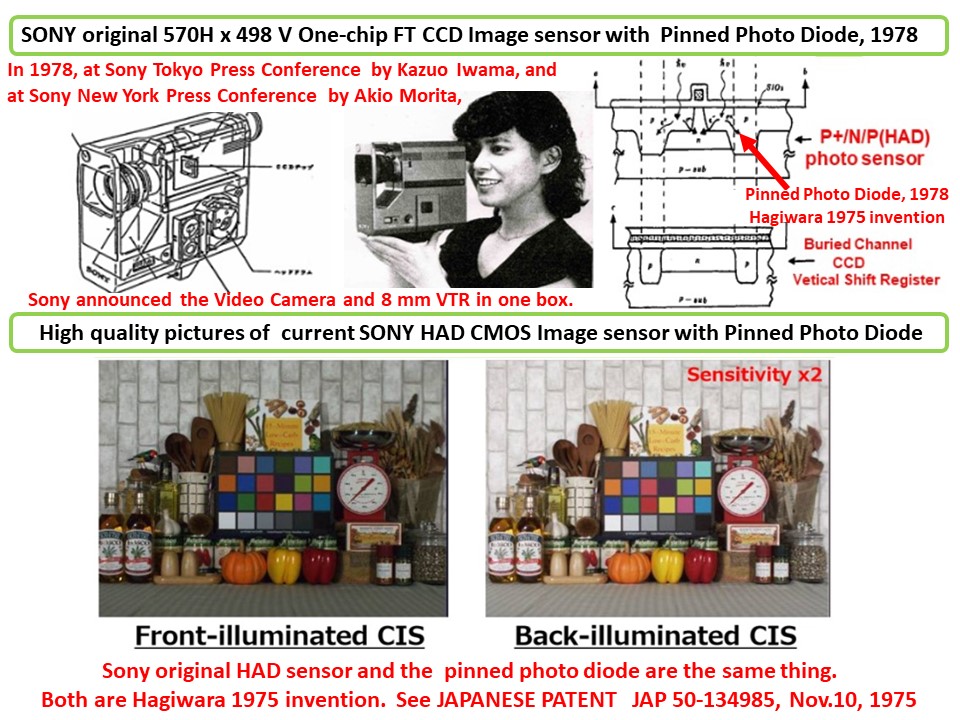

The world does not know that

the pinned photo diode

and

Sony original HAD sensor

are the same thing

Yoshiaki Hagiwar of Sony

invented in 1975.

Sony に1975年に入社してすぐ、萩原は受光素子の構造特許

を出しました。P+NPNsub接合(thyristor)の構造体です。N層を

浮遊状態(floating)として光信号電荷(電子)を蓄積し、それを

隣接するCTD(CCDやBBB,MOS imagerなど)に電荷転送

する半導体固体撮像装置です。固体撮像装置の未来像がどな

ものかと萩原は思案していました。そして、次の5つ特徴を満足

する半導体受光素子でないといけないと考えました。(1)低残像

( low image lag )(2)低熱雑音 (low CkT noise) 、(3)低界面

準位雑音 ( low trap noise)、(4)超光感度( high quantum

efficiency) (5)過剰電荷放流機能(built-in OFD function)

の5つの特徴を持たねばならないと考えました。

学生時代にBCCD(埋め込みチャネル型CCD)の動作解析を

博士論文の研究テーマとしていました。SCCD(表面型CCD)

よりBCCDの方が電荷転送効率が99.999%以上と期待でき、

将来、 信号雑音比(S/N比)の良い、すなわち感度のいい

固体撮像装置として有望視されていた時代でした。

そのBCCDの動作解析で、1974年2月に自分の博士論文を

ISSCC1974で発表し、翌年1975年2月にSONYに入社し横浜

中央研究所のCCD image sensorの研究開発チームに配属

されました。

ソニー厚木工場からプロセス開発チームが研究棟の4階に

集結し、萩原の所属する設計評価チームは5階に集結して

連携をとり、仕事を進めていました。萩原の所属する情報処

理研究所ではCCD image sensorの設計と評価のチームだけ

でなく、そのCCD image sensorを使ってカメラシステムを組み

立て商品化に耐える性能があるかを評価確認するチームも

ありました。

実はSONYに入社してすぐ気がついたことですが、CCDに

には致命的な欠点がありました。最終的にはあまり未来の撮

像素子としては、実用的でないと萩原はすぐに感じるように

なりました。

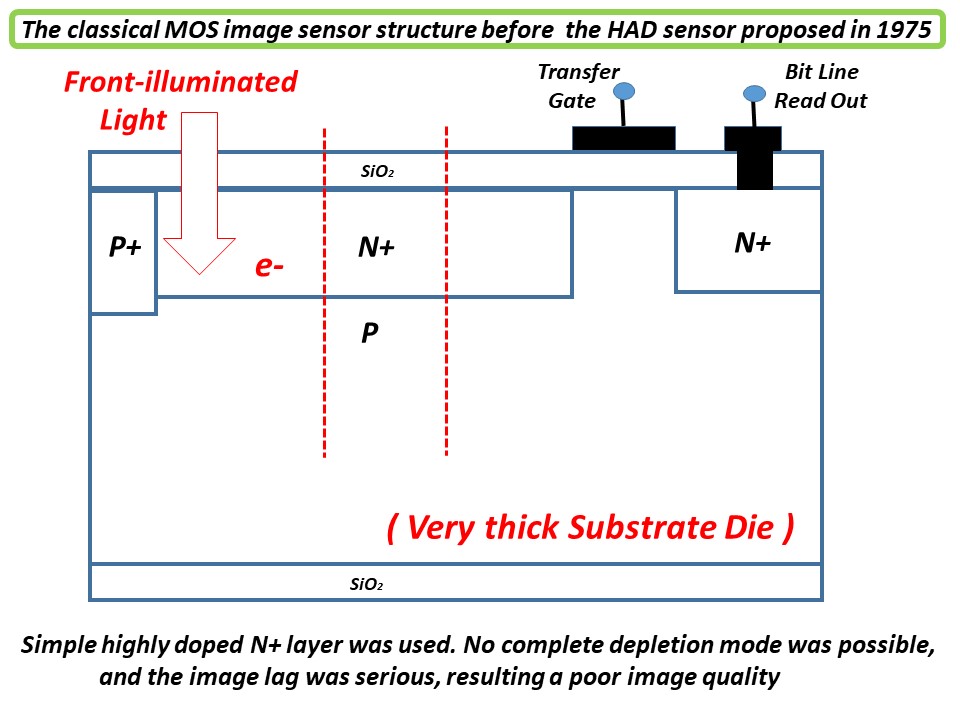

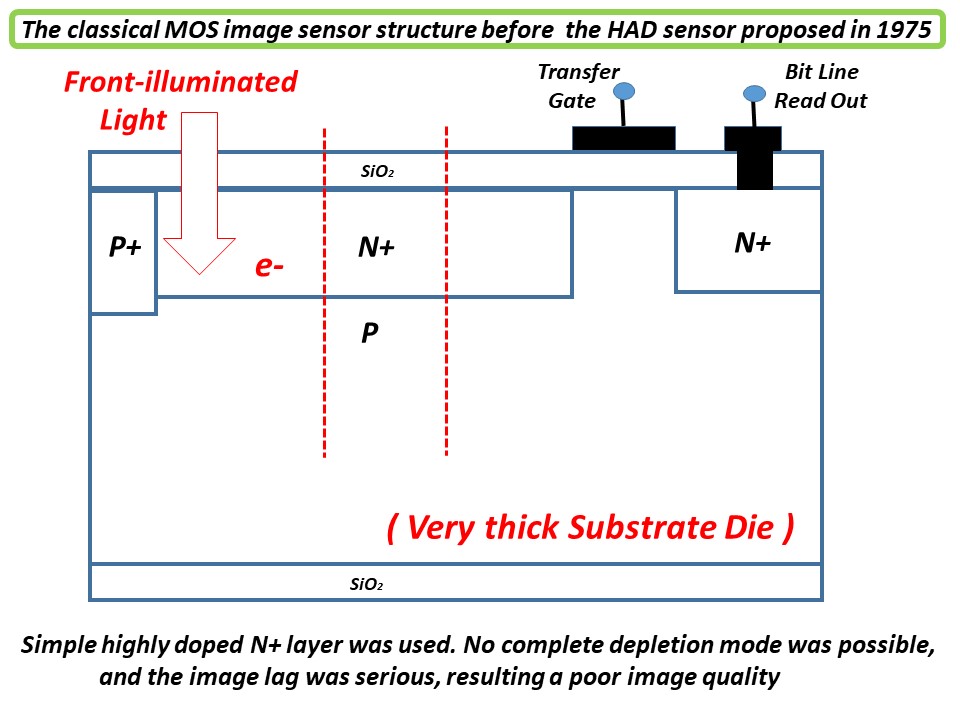

なぜなら、初めからMOS imagerを開発ターゲットをしていた、

日立などの会社がありました。MOS imager はCCDより製造

プロセス工程が単純でした。

従来のMOS transistor のプロセスで製造可能で、その

MOS transistor のsource 領域のN+層をfloatingとして

N+Psub接合を受光素子としたものです。

しかし、受光部であり、光電変換された光信号電荷(電子)を

受光時に蓄積するN+領域は、底なし井戸の様に、電子を

水にたとえると、水がいっぱい入った、底なし井戸の水をくみ

出す様なもので、いくらくみ出しても、そこは深く、人が底なし

井戸の水をくみ出すには、限界があり、いつまでたっても、

底なし井戸を空っぽにはできません。

そこで、光が照射されると、井戸の水は光の量に比例して、

井戸の水が増加する仕組みになっています。その比例した

増加ぶんだけの水量、すなわち光信号電荷(電子)を

くみ出すことが可能な受光素子でした。しかし、N+領域は

たいへん濃い濃度をした領域(底なし井戸)で光信号電荷

(電子)を全部くみ出せず、特に光量が多い場合、くみ出し

残りが生じ、それが残像という現象で、撮影した動画に

現れました。せっかく溜まった井戸の水、すなわち光信号

電荷(電子)を井戸から完全にくみ出せないという、不完全

電荷転送装置でした。

●MOS imager の欠点の1つは不完全電荷転送(残像あり)です。

MOS imagerは光信号電荷(電子)の個数に比例したアナログ情報

を取り扱う、典型的なアナログ情報処理回路です。一方、DRAMは

信号電荷(電子)があるかないか、すなわち、1 か 0 を判定する

デジタル情報を処理する回路です。そのアナログまたはデジタルの

信号情報を信号情報蓄積部から読み出す手法は、両者ともほぼ、

同じで、金属または濃い濃度の拡散層N+で形成され、濃い濃度

の拡散層N+も、ほぼ金属と同じような、抵抗値が小さく、電子を導通

される能力のある、垂直読み出し金属信号線と、水平読み出し金属

信号線を装備しています。

しかし、半導体の微細化がまだ十分進歩していなかった

1970年代では、この金属配線間の容量Cが大きく、この容量

Cに起因する熱雑音 ( CkT noise ) が大きくなります。

●MOS imager のもう 1 つの欠点は熱雑音 (CkT noise) です。

しかし、1969年に米国ベル研究所で発明されたCCDは、

濃い濃度のN+領域を必要とせず、ただ単純にMOS容量を、

電荷転送方向に多数並べただけのものでした。

金属電極下の半導体結晶表面(界面)に、浅い電位井戸を

形成することが可能になりました。また、受光時に、MOS容量に

蓄積された、照射光量に比例した、光信号電荷(電子)を、隣接

する受け取り側の容量に、効率良く転送することが、2つの容量の

総合連携結合効果により、実行可能となりました。

蓄積していたMOS容量、すなわち、受光部であり、かつ同時に、

蓄積部の電位井戸から、電子(水)を、受け取り側のMOS容量に、

完全にはき出すことが可能となりました。

すなわち、完全にMOS容量の井戸の水を完全に空(empty)にでき、

すなわち井戸(well)を完全空乏化 (complete majority carrier

depletion) でき、つまり、完全にはき出す ( complete charge

transfer )ことができ、すなわち、完全電荷転送ができることが

できることになりました。

完全蓄積部の空乏化および完全電荷転送 (complete charge

transfer that results in comolete charge-depleted empty

potential well )が可能な固体撮像装置(solid state image sensor )

が、CCDの到来で実現したということで、CCDは脚光を浴びることに

なりました。

この最初に発明されたCCDは、酸化膜と半導体結晶の接触平面

(界面)に光信号電荷(電子)が転送されるので表面型CCD、

すなわち簡単にSCCDと呼ばれました。

(1)SCCDは残像なしの特徴を持っています。

SCCDの発明により蓄積部の完全空乏化と完全電荷転送が可能

となり、その結果、残像のない動画が実現し、高速撮影、action

picture の撮影が可能となりました。

(2)SCCDはさらに、熱雑音 (CkT noise) なしの特徴を持っています。

さらに、長い金属信号配線が必要でないので MOS imager の場合の

金属配間容量に比例した熱雑音がありません。SCCDは、MOS imager

の致命的な2つの短所、すなわち、残像と熱雑音のない、優れたものとして、

脚光を浴びることになりました。

しかし本来、SCCDの中の信号電荷(電子)は、酸化膜と半導体結晶の接触

面(界面)に存在し、移動転送します。その酸化膜と半導体結晶の接触

面(界面)には、電子を捕獲する(trap)界面準位というものがあります。

一種の落し穴です。電子がその落し穴に落ちると、完全転送が出来ず、

不完全転送となります。またこの落し穴に落ちる様子が、毎回一定でなく、

ランダムに起こり、落ちたり、落ちなかたりが無規則に起こり、目的地(隣接

する受け取り側のMOS容量)には、到達する」電子の数がランダム無秩序

となり、映像でその結果、映像に雑音が入っている様に見え、その雑音を

界面準位雑音といいます。

●SCCDには界面準位雑音がある。

SCCDの発明の後、その派生品種、改良型が発明されました。

埋め込みチャネル型のCCD、すなわち、BCCDと呼ばれました。

SCCDよりさらに転送効率がよく、学会では99.999%(five nine)

の電荷転送が可能で、完全電荷転送が実現したと期待されて

いました。

BCCDもMOS容量を単純に並べたもので、濃いN+拡散層が

不要です。MOS容量により、このBCCDでは、埋め込みN層に

浅い井戸を形成することが可能です。蓄積部の完全空乏化が

可能で、かつ完全電荷転送が可能です。

従って、SCCD の良さを兼ね備え、さらに、SCCD と違って、

光信号電荷(電子)は半導体結晶体の表面下に埋め込まれた

薄い濃度のN層の真ん中に形成される通路(channel)、まるで

地下鉄の電車の様に、地下の通路(buried channel)を地上の

落し穴に落ちる事なく、安全に移動することが可能です。

地上のさわがしい交通量(界面準位雑音)からも解放され、

地下鉄(埋め込みチャネル)転送方式は静かで雑音のない

環境(no trap noise )が実現しました。。

ばかばか、地下鉄は騒音が多く、実はやかましいよ(笑)

その雑音ではありません(笑)。

電車が予定通り遅れず目的地に時刻表通りに到着する

どうかのお話です。

ほぼかっきりと予定通りの時間に到着するのが地下鉄です。

いや通勤時はそうでもないよ(笑)。

しかし、地上の乗り物はもっとひどく、渋滞状態が日ごとに

異なり、ランダムとなり、SCCDのランダム雑音となります。

テレビの映像を見ると、何かもやもやした雑音の多い、きた

ない映像に感じる、SCCDのランダム雑音ものになります。

そのSCCDのランダム雑音、界面準位雑音( trap noise )

がBCCDではなくなります。

(3)界面準位雑音 (trap noise) なしの特徴

このBCCD の3つの特徴で未来の固体撮像装置と期待される

BCCDを博士論文テーマに萩原は選択しました。

1972年の秋から1975年の冬迄の間、萩原は母校米国 CalTech

( CaliforniaInstitute of Technology) で、3人 の 指導教官、

Prof.C.A.Mead 。Prof.James McCaldinと Prof.T.C.McGill の

指導のもと、研究。25歳にして、ISSCC1974で学生論文(PhD

paper)を発表。

論文の内容は、BCCDを使った固体撮像装置がどのくらい高速

に動作するかの可能性について解析した結果報告でした。

すなわち、BCCDの埋め込み層の転送通路(buried channel )

に生まれる電界強度、すなわち、ボールが下り坂をどのくらい

はやくころげ落ちるか、下り坂の傾斜の関係で、どのくらい早く

ぼーるが落ちることかの解析報告でした。

半導体内の光信号電荷(電子)の二次元動作解析を。大学

にあったIBM360を使って Fortran 言語で program して

computer simulation をして、さらに、 CalTech所属の JPL

(ジェット推進研究所、鉄腕アトムのジェット推進百万馬力を

連想する研究所で、月面、火星へで自動走行する探索機と

地球への通信システム技術を開発する研究所)にある、特殊

なNASAの装置を使い、その計算結果を36ミリフィルムに焼き

付け、お隣のHolywood では、映画撮影関連会社で 16ミリフィ

ルムに焼き付けて、あらかじめ、ISSCC1974の会場で用意して

もらっいた16ミリフィルム映写機を使って、数分のアニメーション

動画としてISSCC74の学会で1000人以上いる半導体集積回路

の技術者の前で映写しました。

発明されたBCCDの有望性を明らかにするために、この埋め

込み層型CCDの埋め込みN層の中を、界面準位から守られた

光信号電荷(電子)のかたまり(packet)が流れる様子をアニ

メーション動画として再現しました。世界で初めてで、多分また、

最後のBCCDの完全電荷転送をコンピュータアニメーション

化したものでしょう。それも当時最新のIBM360コンピュータを

使って、さらにJPLのNASAの film 描画装置を使って、さら

に Holywood の会社で16mmにして、コンピュータアニメー

ション動画にしました。

BCCD の3つの特徴、すなわち、(1)低残像(2)低熱雑音 (CkT

noise) (3)低界面準位雑音 (trap noise) の特徴を兼ねてもつ、

極めて有望な未来の固体撮像装置として期待されるものでした。

学生時代にBCCD(埋め込みチャネル型CCD)の動作解析を

博士論文の研究テーマとしていました。SCCD(表面型CCD)

よりBCCDの方が電荷転送効率が99.999%以上と期待でき、

将来、 信号雑音比(S/N比)の良い、すなわち感度のいい

固体撮像装置としてBCCD有望視されていました。

そのBCCDの動作解析で、1974年2月に自分の博士論文を

ISSCC1974で発表し、翌年1975年2月にSONYに入社し横浜

中央研究所のCCD image sensorの研究開発チームに配属

されました。未来の固体撮像装置の性能を満足する為には

次の5つ特徴を満足するこが必要だと職場の先輩に教えて

もらいました。(1)低残像( low image lag )(2)低熱雑音

(low CkT noise) 、(3)低界面準位雑音 ( low trap noise)、

(4)超光感度( high quantumefficiency) (5)過剰電荷放

流機能(built-in OFD function)の5つの特徴があります。

なるほど、BCCDは(1)、(2)、(3)の特徴があるが、(4)の

感度に関しては今いちで、(5)のOFD機能はBCCDで実現

できるとは全く思われませんでした。それにBCCD感度も金属

電極を持つMOS容量構造を受光部としてもつBCCDは、

金属が光を反射するして光を通過させないのでまったく感度

を考えるとMOS容量構造を受光素子ともつ固体撮像装置

には未来がない、CCDでは未来がない、と不安になりました。

せっかく、CCDをスーパスターと信じ、学生時代、自分の青春

時代を過ごしてきたのに、他にスーパスター、自分の夢になっ

てくれるものがあるはずと思うようになりました。日立の技術者も

同じことにすでに気づいていて、早期にCCDを未来の固体

撮像装置としての候補から外していました。

当時 Intel社は MOS transistor 技術で MOS ICを商品

化し、IBMという大型顧客をつかみ Intel のMOS transistor

技術で製造された DRAM chip がバカ売れしていました。

その創設者の Gordon Moore 社長が会社に経営ビジョンとして

半導体の微細化構造のscaling則を根拠に、3年ごとに2倍の

集積度を持つ、すなわち同じ大きさで2倍の数の MOS transistor

が組み込まれて MOS IC chip を市場に提供すると宣言して

いました。

すなわち、MOS imager の致命的な欠点は熱雑音 (CkT noise)

は、いずれ、MOS transistor の微細化努力で CCDより

MOS imager が勝つと信じているようでした。事実、SONYが

CCD imager を世に出すより、はるか前に、日立はきれいな

MOS imager を試作を世に発表し、学会でもその詳細を報告

していました。しかし、ソニーのカメラ事業部の要求は厳しく、5つ

の特徴をもつ撮像素子でソニーは高性能カメラを市場提供し

販売すべきと譲りませんでした。

ソニーのカメラ事業部とそのために固体撮像素子を開発すべく

模索している開発部隊の見解としては、不完全電荷転送(残像)

と熱雑音 (CkT noise) を持つ MOSimager は当然使い物に

ならないという見解でした。

その頃、ISSCC1974で BCCDの動作解析を博士論文として

学生論文を発表しました。彼の博士論文は 3つの特徴、(1)低

残像( low image lag )(2)低熱雑音 (low CkT noise) 、(3)低

界面準位雑音 ( low trap noise)を兼ね備えたBCCDをテーマ

にしており、ISSCC1974の学会でBCCDが将来有望で、論文

の中に萩原が使った正確な言葉を言うと、 low light imaging

の応用でBCCDは最適であると論じていました。

それを信じて萩原は1975年1月最終博士論文の論文発表会で

合格した、その足で6月の卒後式も待たず、すぐ帰国し、1975年

2月20日にソニーに入社し、横浜中央研究所に配属され、未来

の固体撮像装置の開発研究に挑戦しました。

Sony に1975年に入社してすぐ、萩原は受光素子の構造特許

を出しました。P+NPNsub接合(thyristor)の構造体です。N層を

浮遊状態(floating)として光信号電荷(電子)を蓄積し、それを

隣接するCTD(CCDやBBB,MOS imagerなど)に完全空乏

化電荷転送する半導体固体撮像装置です。未来の固体撮像

装置の性能を満足する次の5つ特徴を満足します。(1)低残像

( low image lag )(2)低熱雑音 (low CkT noise) 、(3)低界面

準位雑音 ( low trap noise)、(4)超光感度( high quantum

efficiency) (5)過剰電荷放流機能(built-in OFD function)

の5つの特徴があります。

この特請求範囲で定義・提案する構造体は、特徴(1)から(3)

の特徴は構造を見ただけでだれでも理解できるものでさらに

この構造体は酸化膜の上に金属電極がない構造なので、そ

の構造を見るだけで特徴(4)超光感度( high quantum

efficiency) も、言葉しして説明することもないもので、特徴(1)

から(4)の説明はいらないだろう。図を1枚描けば素人さんに

は読み取れないが、固体撮像素子の実践開発担当従事して

いる技術者には簡単に認識できるはず、と萩原は考えた。会社の

特許関係者も、見る人ぞ見るで、あまり素人さんや後発メーカ

の教材になるような説明の詳細は必要ないので省略してもよい

のでは、それに時間をかけるより早く職場に戻ってこれを造って

下さい。との話で、実はあまり会社の特許弁理士が私の説明を

口頭で聞いた(録音機つき)を文章化して清書して特許に説明

文は2~3分で棒読みだけで、しかし、特許の請求範囲を定義

する文書は、単語1つ1つしっかりチェックし、図もしっかり考えて

実施例として、すなわち、特許請求範囲の有効性を示す具体

的な特殊例、1例を示す図として提示しました。

しかし、この実施例を、特許の本質の特許請求範囲の定義する

ものと誤解する技術者も多く、社外でもかなり笑われ、私の書いた

特許請求文をまじめに読まずに、ほんの 1 例の実施図 5 を見て

これが私の特許に意味するところすべてだと誤解し、この実施

図 5 を見た社内の上司や同僚からは 「受光絵素部に1個づつ

金属コンタクトをつける構造などものになるかよ、お前ばかか?」

とよく笑われました。

別に金属コンタクトの存在は特許請求範囲の定義には記述されて

いないよ、実際金属配線は受光絵素部以外でもいいんだけよ。この

時はどうするかまでは考えれおらず、どででもいいことで、特許は

あくまで 受光部のたて構造( P+NPNsub Vertically Stacked

Junction )のみに請求範囲を限定するものだよ。 とにかく受光

蓄積部のN層の上にP+領域をとり、このP+層がなにかの外部端子

で固定されていて、浮遊状態(floating)でない、一定ので電圧に

固定(ピンどめ)されるべきものであることを明示するための実施例

にすぎないと主張したが、どれだけ私の説明を理解されたか不明

である。しかし、百聞は一見にしかず、でこの道の実践専門家なら

いろいろなことが見て認識できるはずと思っていました。

結局、社内だけでなく、この特許は日本国にしか申請しておらず、

日本語で記載された特許範囲請求文をしっかり読み理解してい

る人間は、おそらく社内でもこの特許を目にした人は特許関係の

数人だけで、日本国内の他社でも特許をしかり調査をして目を

ひからせる数人の優秀な技術者だけで、外国の技術者は当然

目にしていなくて当然です。この特許は国内での商売の時のみ

特許請求権が発生するもので、外国の技術者には読む必要も

ないものです。外国の技術者は萩原の特許を見たこともなく、

時々萩原が学会に招待講演で紹介するこの1975年の萩原特許

の内容しか外国では公表されていないことになります。

実際、2013年にISSCC2013で説明した時にもこの特許の構造体が

潜在的に完全空乏化電荷転送が可能で残像なしという重要な

ことをコメントしませんでした。しかし、図には埋め込みチャネルの

N-層と同じ濃度のN-が使われていることが明示されていています。

これが完全空乏化電荷転送の存在のヒントになり、ここに提示した

受光構造はすべて残像なしの映像を提供することは自明と萩原

は考えていて、あえて、残像の話はこのIEEE SSCS出版の技術

マガジンの記事には説明文を入れませんでした。

いずれにせよ、1975年の萩原特許の1つの実施例の示す図5と

図6は、必ずしも、特許請求範囲を、限定制限するものではないが、

(1)低残像( low image lag )、(2)低熱雑音(low CkT noise) 、

(3)低界面準位雑音 ( low trap noise)、(4)超光感度( high

quantumefficiency) 、(5)過剰電荷放流機能( vertical built-in

OFD function、VOD )の5つの特徴がもつことを示している。

これが今のSONYのHAD技術搭載の固体撮像素子の特徴です。

SONYのHAD技術搭載の固体撮像素子は1975年に発明考案し

た萩原特から生まれました。当時のMOS構造をもつCCDの受光

構造よりはるかに超感度の特徴を持ち、残像 free であることを

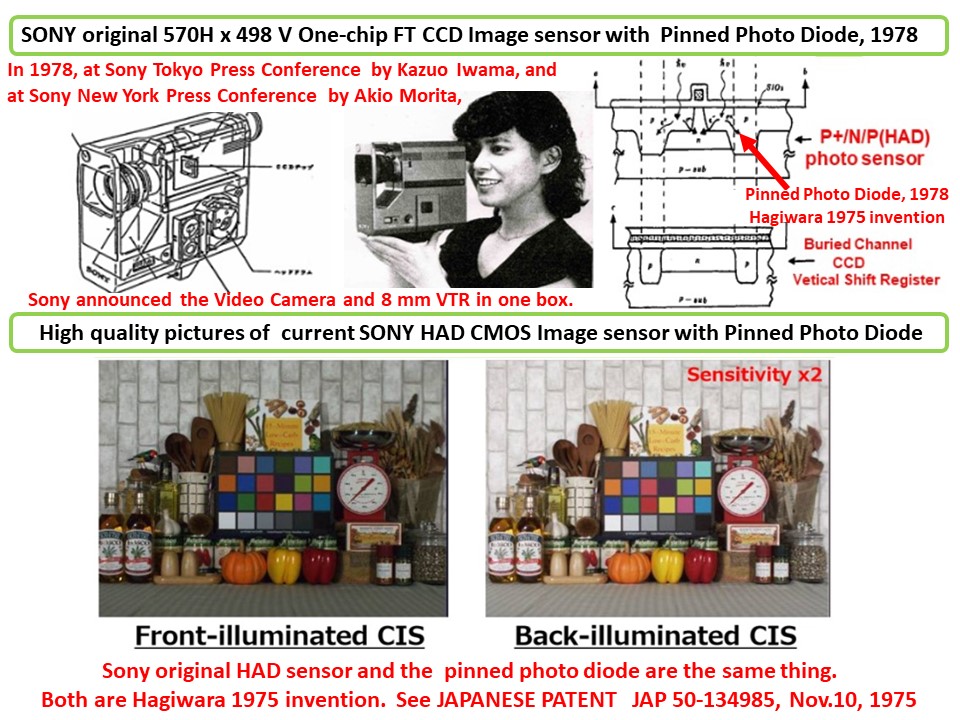

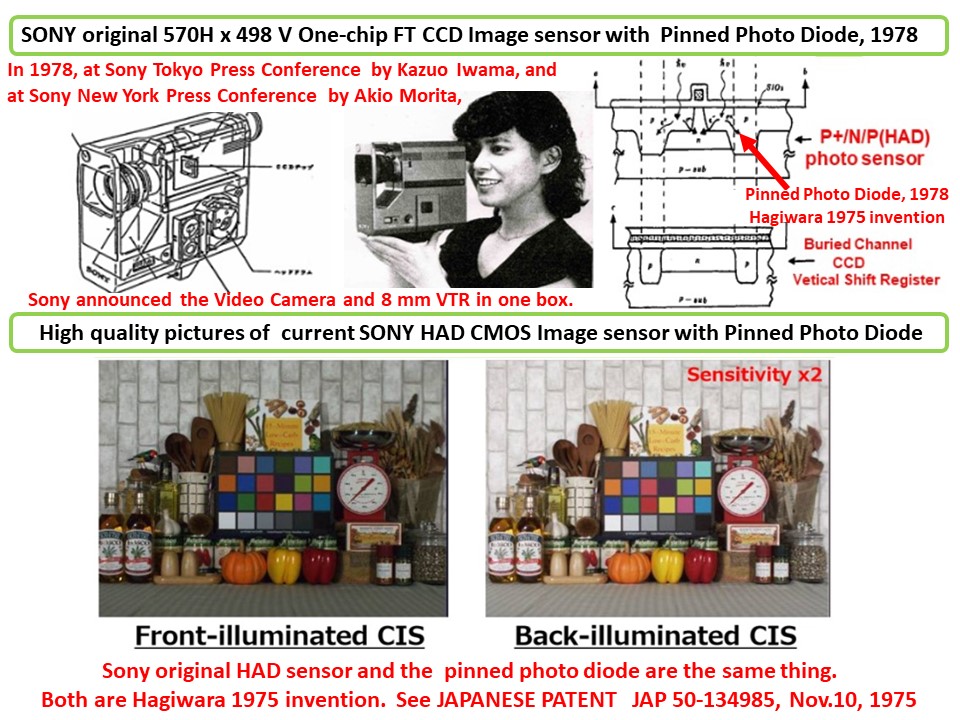

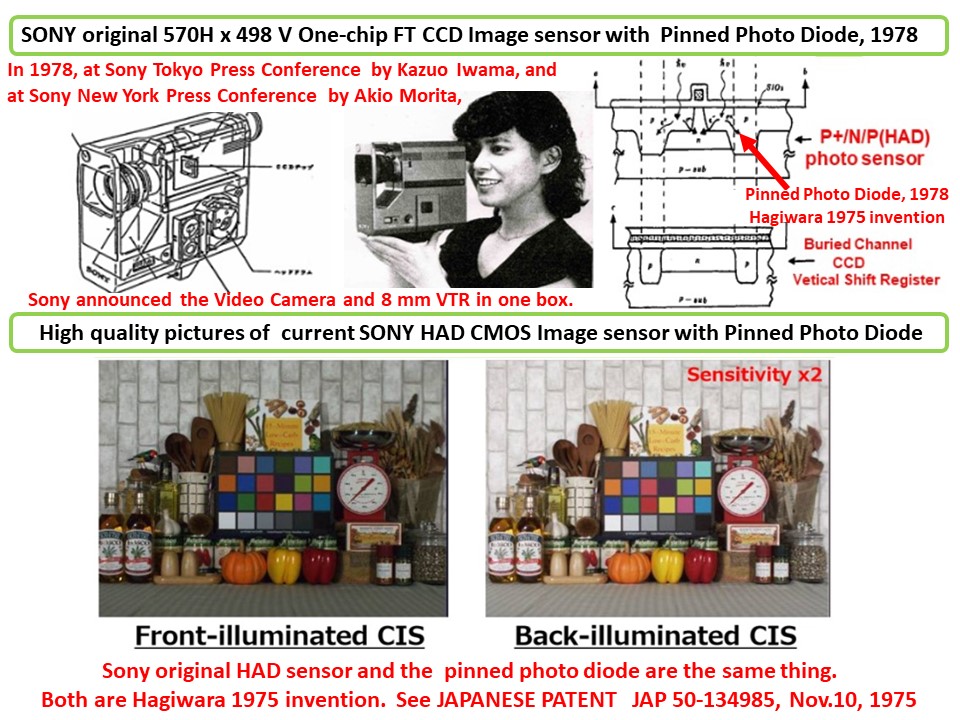

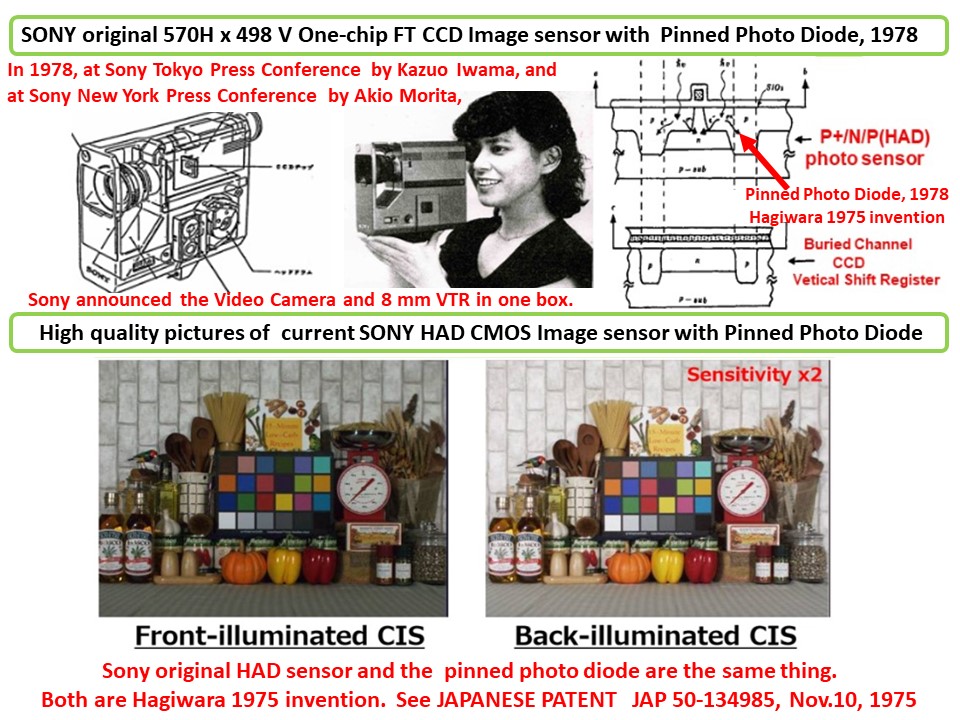

1978年、SONYは初めてSONY original HAD技術搭載の

FT CCD image sensor video camera に原理試作に成功しました。

そのすばらしい感度を持つ SONY original のHAD技術搭載の

固体撮像素子を採用した FT CCD image sensor video camera

をVTRとカメラの一体化 8mm ムービーとして SONYは 1978年、

盛田会長と木原さんが New York で 、岩間社長と森尾さんが

東京で、同時記者会見し、その超感度 SONY original のHAD

技術搭載のFT CCD image sensor video cameraを世の中に公開

しました。

その受光構造構造を発明し、sensor chip 全体を一人で設計した

萩原と、CCDプロセスを担当した阿部と、評価を担当した岡田の、

3人で東京で開催の固体素子コンファランスで技術の詳細を報告。

ここで世界は誤解しました。

SONYが強調した超高感度は、萩原が考案しSONY original の

HAD技術による試作・原理実証された受光構造構造であるのに、

CCD そのものが超感度の性能を持つと世界は誤解しました。

CCDは単純にアナログ信号伝達線として採用されているだけです。

CCDは単純にアナログ信号伝達線の役割しかなく、将来MOSの

transisor 技術に負ける運命にあることを誰も予想しませんでした。

従来のMOS transistorの金属信号伝送線の配線間容量が格段

に少なくなると、熱雑音が小さくなり、実用に耐えるレベルになると、

プロセス工程の単純なMOS transistor のプロセス技術がCCD

を置き換え、CCDを市場から排除するのではないかと萩原は不安

でした。最後はデジタルが勝つ。そう思って萩原はCCDの開発部

から完全に離れ、社内のSRAM、DRAM、ADC,Sony マイコン、

そして PS2 および PS3の Cell Processor を見るようになりました。

固体撮像受光素子構造 (Solid State Image Sensing Element

Structure )は 1975年の基本構造で未来像が見えた。人間でいうと

目の網膜細胞にあたる「電子の目」はこれで多くの技術者の努力

(diligence)で完成する。しかし「賢い電子の目」、「人工知能を

搭載した賢い電子の目」を造るには、まだまだ勉強することが多い。

母校 CalTechの Richard Feynman も、一生研究を続け、癌で

たおれ死ぬ直前まで、物理の授業を学生に講義し、自分の知識

を後進に伝承する努力に惜しまなかった。1967年に CalTechに

入学し、最初に手にしたのは赤い分厚い3冊のFeymann Physics

の教科書だった。萩原は電子工学を major専攻、物理を minor

専攻として両方の電子工学と物理で博士号を取得してが、大学

院生として物理学部の学生に量子力学の教える授業の授業補助

(Teaching Assistant)として量子力学の宿題の模範解答や中間

試験問題、期末試験の模範解答と採点などを講義する偉い教授

のアシスタントもしており、Richard Feynmanの授業も何度も聴講

し、彼の研究室で話を聞いたこともある。その時の話題の1つが、

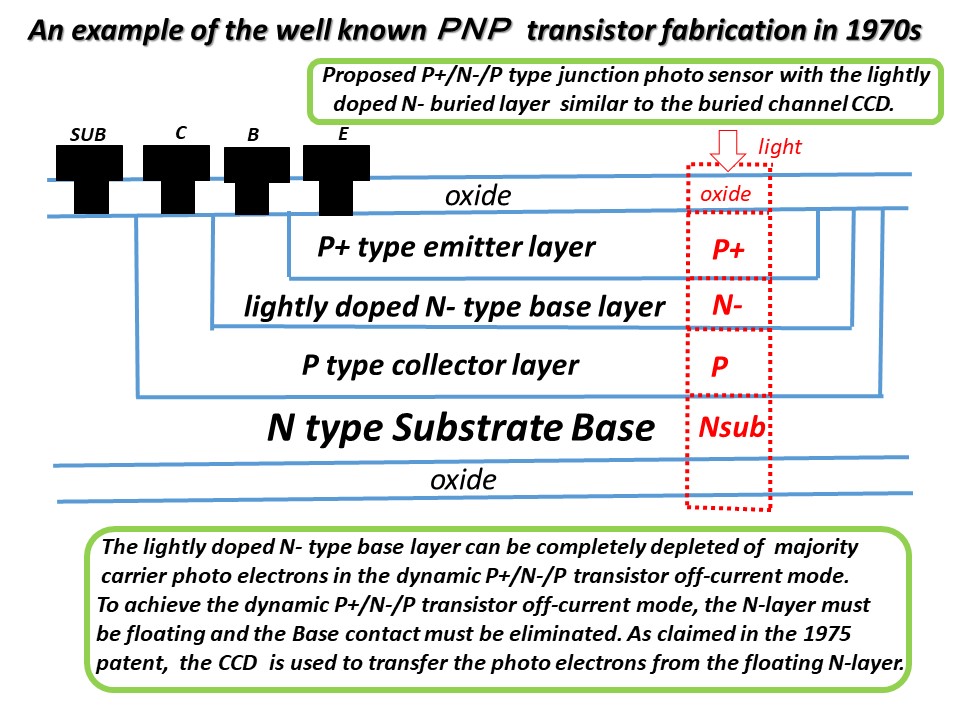

bipolar PNP transistor の動作原理である。Feymannの3冊の本

は1冊目が古典物理、2冊目が電磁気学3冊目が量子力学となって

いるが、3冊目の後半の 第14章に Semiconductor と題して半導

物理の紹介があった。大学2年生だった萩原、当時19歳にして、

はじめて Section 16-4 に紹介されたbipolar taransisor の構造

すなわち PNP接合型 bipolar transistor の構造とその動作

原理を学んだ。図 16-11には、3つの外部端子(Emiiter, Base,

Collector 端子)が同じ電圧、すなわちバイアスなし( no bias)の図

であった。PNP接合型 bipolar transistor の内の正孔(hole)が

見る正電位( positive charge hole potential )の図である。これを

上下さまさまにすると負電位( negtive charge electron potential )

の図となる。現在の業界で良く使われるなじみの図となる。

2年生の時に授業で説明された時は早口の英語でまったくこの図の

意味するところが理解できなかった。3年生になって Prof.McCaldin

の Physics of Semiconductor の教科書で半導体物理だけの授業を

受けた。そして 大学2年で学んだ図は半導体の Band 図であること

を知った。さらに、そして大学院になるとCCDの新しい原理で動く

半導体素子の話を聞き、CCD potential wellの図を良く見るよう

になったが、これも半導体の Band 図であり、大学2年で学んだ図

とおなじものとわかった。

Feynmanの物理の教科書で大学2年の時学んだ図が、萩原が初めて

学んだ potential well の概念図だった。

バイアスなし( no bias )状態でも、すなわち、このPNP接合型

transistor の電流 off 状態でも、両方の emitter-base 接合と、

base-collector 接合の両方の、majority carrier が存在できない

空乏層領域ができる。そこに生じる電界で、P領域の正孔(hole)と

N領域の電子(electron)が分離し、再結合することなく、それぞれ

自分の陣営(領域)でじっとしているとのイメージがCCDの動作

原理を勉強している時、同じ potential well を見て気がついた。

電位で水平になっているのはそこにmajority carrier がたっぷり

集まっている(accumulation mode) 状態で、あたかも池に水が

たまると、水面は水平になっているのに似ているということになる。

PN接合の接合面付近の空乏層には電界があり、それがこの電位

の電位の勾配となり、そこは水平でなくなる。

また、N層(池)の電子(水)が空っぽになると、すなわち、完全空乏

化すると、N層(池)の底の形 (potentail profilel) が見えるはずだ。

もしPNP transistor のbase N層の電子が完全空乏化したら、もし、

濃度が均一なら単純な二次曲線となり、完全空乏化したN層内の

電位曲線はN層の中央付近に極小点を持つことになる。これをよく

CCDの文献で見るようになったが、PNP transisorの N層でも

同じ様な極小点を持つ曲線になるはず。

これは今話題のBCCDの埋め込みN層の empty potential well と

同じはずだ。Bipolar Transisor base N 層も CCD の埋め込み層

の N層も、完全空乏化して電荷が空っぽにすると電位曲線はflat

にはならない。N層は極小点を持つ曲線、empty potial wellとなる。

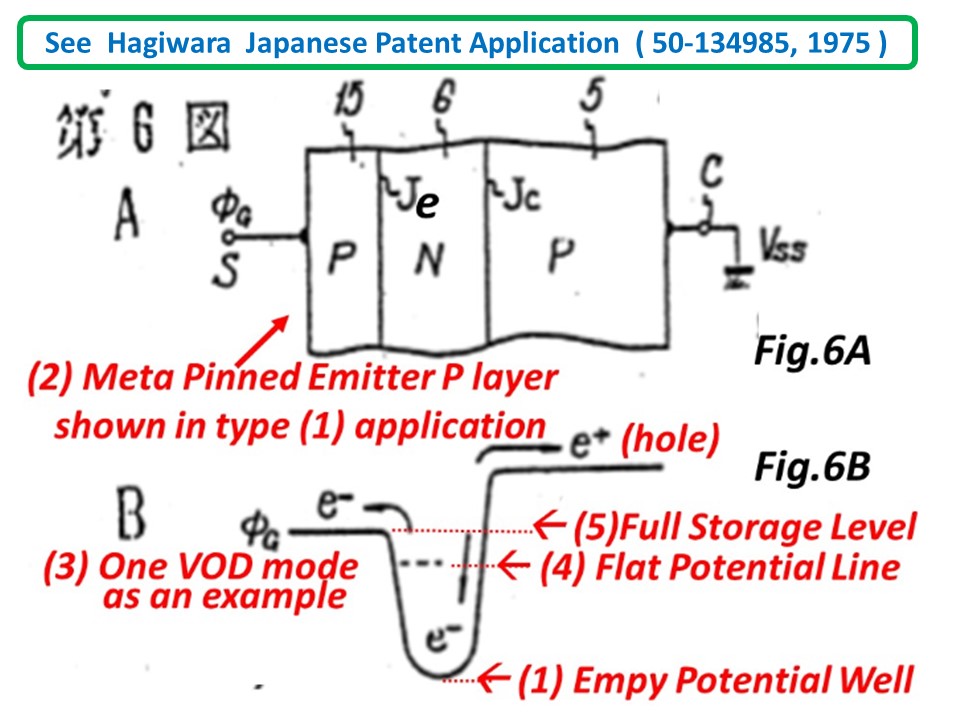

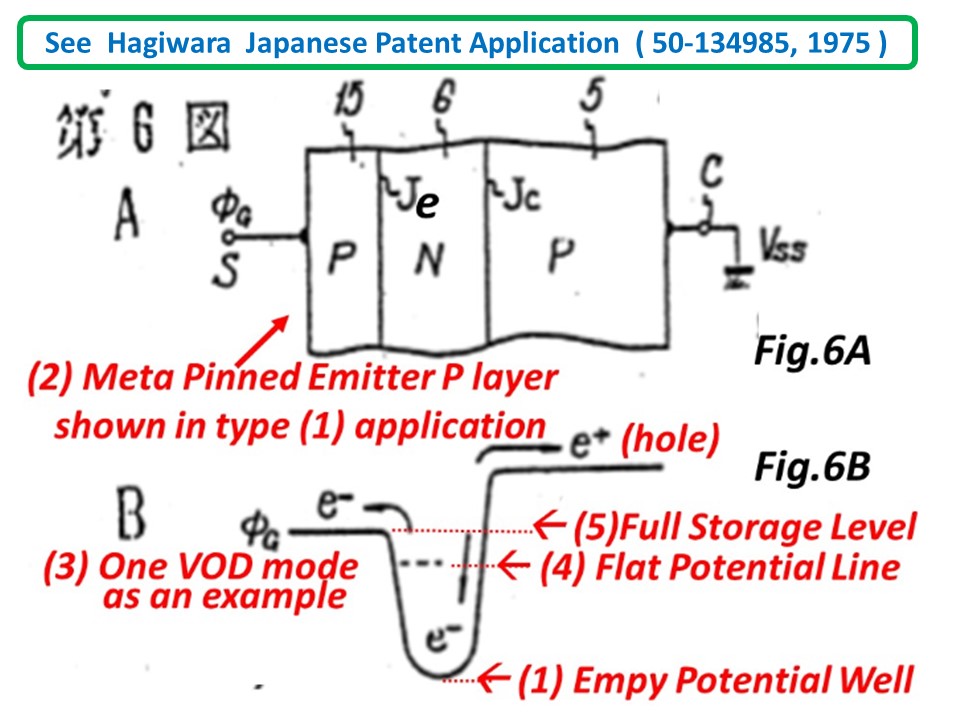

そのことを明示するために萩原は特許の図6BのPNP transisor の

base N 層の中の電位図として、empty potial wellの曲線を描いた。

幼年期にお寺の池で水亀を盗んで家に持ちかえり近所の子供と遊ん

でいたが、その池の水を抜いたら、ほぼ平らな底が出てくるが、それ

とは違うことになる。半導体物理は古典物理ではない、電磁気学の

世界で、さらに、量子力学の世界にも首を突っ込んでいる。

萩原はこの大学時代の時に学習した CCDのpotential wellと

PNPのpotential wellの共通関係を思い出し、1975年出願の

特許の図6Bに empty potial well 図を描いた。

未来の固体撮像装置の性能を満足する5つ特徴、(1)低残像

( low image lag )(2)低熱雑音 (low CkT noise) 、(3)低界面

準位雑音 ( low trap noise)、(4)超光感度( high quantum

efficiency) (5)過剰電荷放流機能(built-in OFD function)

のうち、(1)低残像( low image lag )の特徴をこの萩原特許でも

期待されることを明示するためにempty potential well を図6B

に明示した。また、(2)はCCD転送回路を使えば1975年のプロ

技術でも実現可能であった。(3)低界面準位雑音 ( low trap

noise)は、受光・電荷蓄積部のN層が emitter P+N 接合で

守られているので問題ない。(4)超光感度( high quantum

efficiency)の特性も、P+層の上は酸化膜(ガラス)だけで保護

されているので要求される感度を満足している。

ただ、 (5)過剰電荷放流機能(built-in OFD function)も

この萩原特許では実現可能な構造となっており、その有効性を

図6BのPNPtransistor の動作事例で emmiter 接合で順方向

電流が放流電流として流れる様子を 電子(e-)が1個だあるが、

base領域から流し(drain)となる P+ emiiter 領域へ移動する

様子を示しており、これで 萩原特許1975は、未来の固体撮像

装置が保有すべき5つの特徴をすべて兼ね備えた受光素子構

造体であることが理解できる。

かなり長い論評文になりましたが、以上の説明で、

SONY HAD Technology 搭載の solid state imager は、

(1)低残像( low image lag )

(2)低熱雑音 (low CkT noise)

(3)低界面準位雑音 ( low trap noise)

(4)超光感度( high quantumefficiency)

(5)過剰電荷放流機能(built-in OFD function)

の特徴を持っていることをお理解いただけたでしょうか?

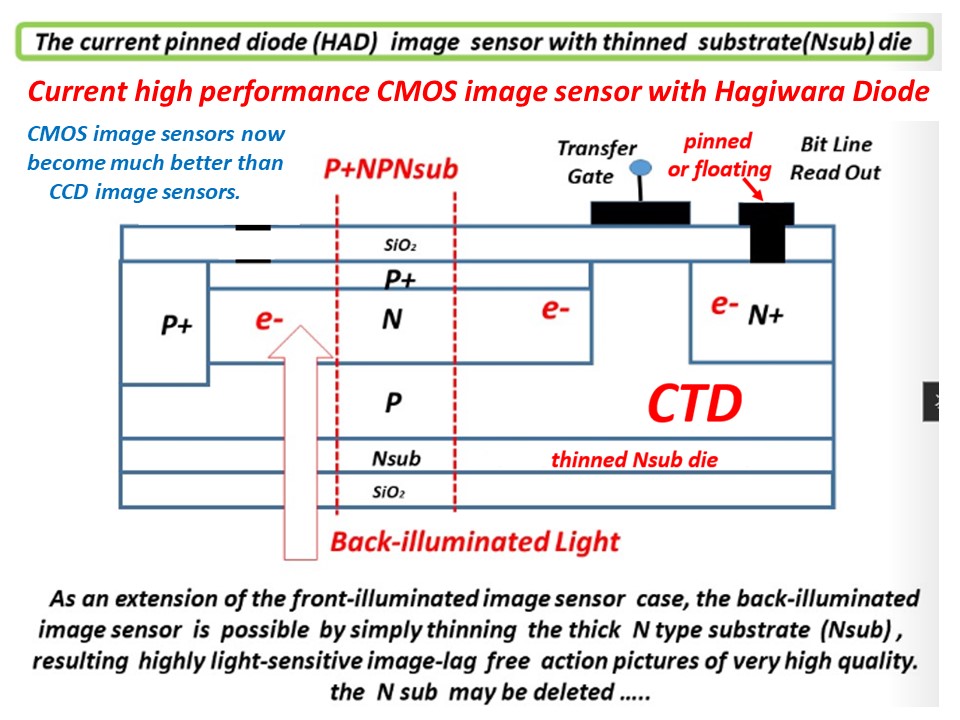

いずれそれは、Intel の創設者Gordon Mooreが提唱した

半導体MOS transistorの微細化技術による進歩のおかげで、

金属配線間容量が極端に減少し、単純に CMOS transistor

と微細化された金属信号線で構成されるアナログ信号電荷

転送回路が、CCDをカメラ市場から完全に排除しました。

しかし、1975年に萩原が発明した超感度超低雑音残像なしの

Sony original HAD sensor 技術は今も生き残っています。

1978年の Sony original HAD sensor 技術搭載の FT

image sennsor で世界は CCD image sensor は感度が

いいんだ、雑音もないのだ、色再現もすごいのだと騒がれて

CCDがちやほやされたいて萩原はさびしい思いになりました。

萩原は実はSony original HAD sensor 技術がすごいの

だと世界に理解してほしかったです。1978年にはじめて

HAD技術を世界に紹介し、それから40年がたちました。

今ではCCDはどこかに消え、Sony original HAD sensor

技術 と 超微細化された CMOS transistor 技術の融合

に現在の固体撮像素子が完成しました。

Sony original のHAD技術搭載の CMOS image sensorが、

今では、世界に カメラ市場の50%以上をSonyが占め、

その単体image sensor chip としての売り上げは1兆円以上と

なっています。

これもすべて、萩原が26歳の若い技術者が考案した未来の

固体撮像素子の構造体特許があっての Sony original

HAD sensor 技術と言えるものです。

先日、半導体産業人協会主催の若手社員向けの半導体講座で

「賢い電子の目, solid state image sensor 」の題目で講義を担当し、

春の講座が先日終了し、秋の講座では資料を最近版にして補充

する必要があります。

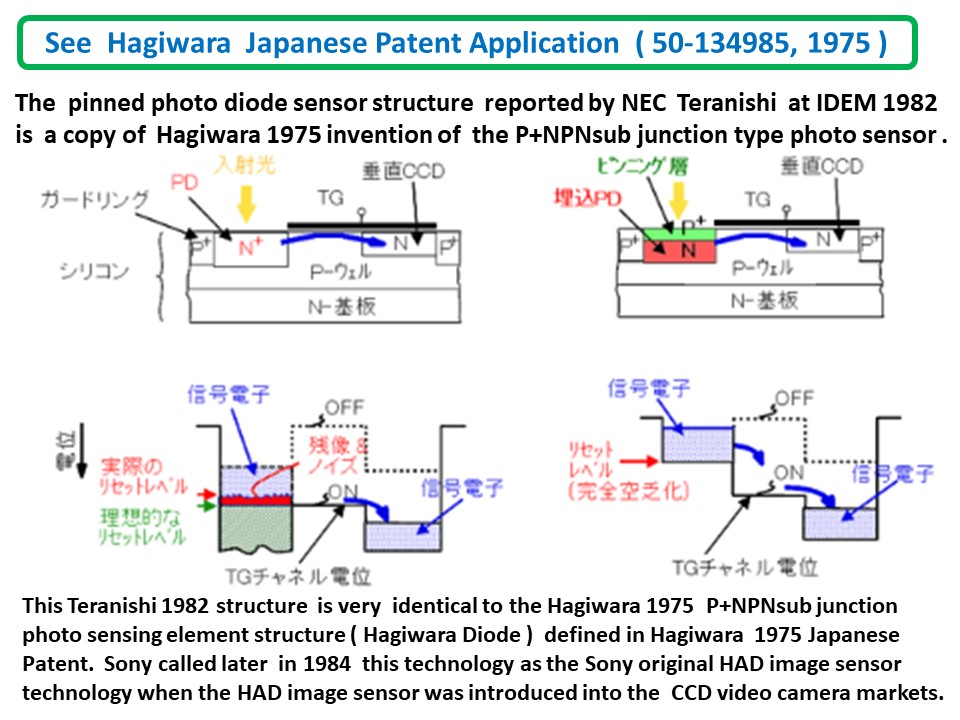

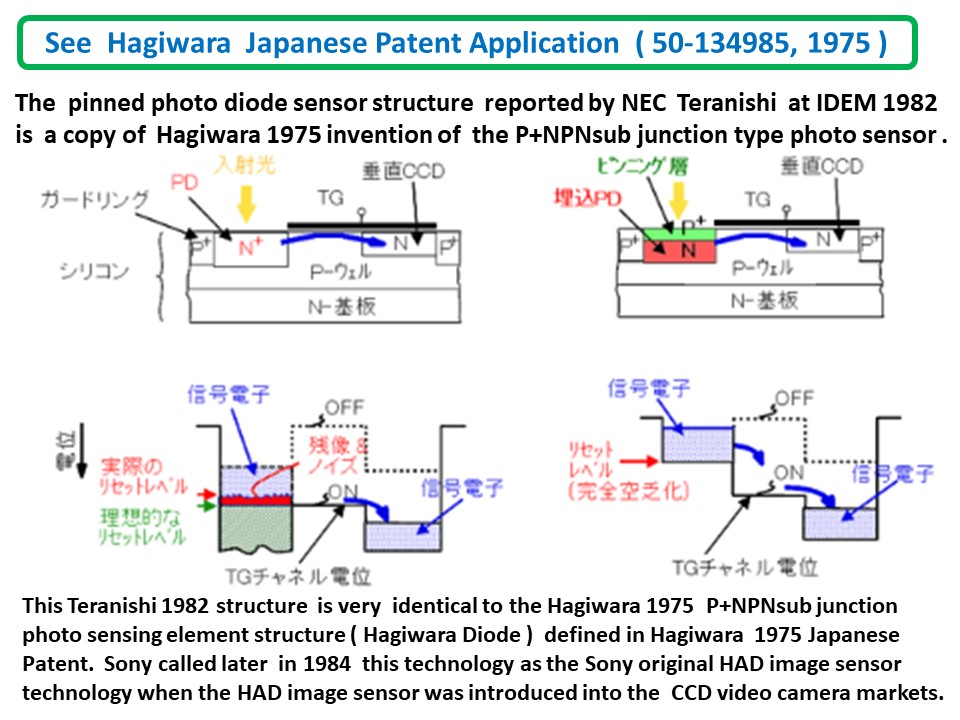

丁度、今、世の中で騒がれている pinned photo diode sensor

の発明者として注目されるもとNECの寺西さんの内容を秋の講座

資料に取り込もうと思い、寺西さんが、1983年にIEDMで発表した

「世界で初めての残像なしの ILT型CCD imager の原理試作

とその特性の詳しい発表」の論文内容と、pinned diode sennsorの

構造とその特徴を勉強し、秋の講座の教材に使用しようと、その

内容を詳細に学習しました。

すると、びっくり、Sony originalの Sonyの商標 HAD sensor

(私の1975年の発明もの)とまったく同じ構造体で、またその特

徴(1)から特徴(5)まですべてほぼ同じことに気がつきました。

一体なにが原因でこうなったのかをこの2週間調査して、やっと

その原因が解明されました。

(1)すべとの世界の誤解は 2014年に投稿された Fossum 論文

の萩原の過去の仕事に対する評論コメントが、事実誤認で

バイアスされていて、SONYをも敵対する姿が見える論文でした。

その中で、SONYのHAD technology と 萩原の 1975年

特許ともに今の pinned photo diode ではないとの結論でした。

彼の論評は、

(1)1975年の萩原特許には 完全電荷転送に関する記述がない

(2)受光部に金属コンタクトがある

(3)従って、pinned photo diode の条件を満たしていない。

(4) 従って、1983年に IEDM で発表した NECの寺西氏が

pinned photo diode の発明者である。

となっているが、彼は萩原の日本語特許を直接見ておらず、

理解していないのが原因のようだ。

彼の論評の(1)と(2)は真っ赤な嘘である:

彼の論評(1)が真っ赤な嘘である証拠:

萩原1975特許の実施例の図6Bに描かれている、

完全電荷転送を示唆する empty potential well の存在を

彼は把握していない。

彼の論文ではこのempty potential well の存在の

記述が全くない。この結論は都合の悪いものを隠している。

事実誤認で、彼の論文を読む読者をだます結果となった。

彼の論評(2)が真っ赤な嘘である証拠:

萩原1975特許の実施例の図5、金属コンタクトが描かれた

図5はあくまで実施例である。

萩原1975特許の特許請求範囲を制限するものではない。

萩原1975特許の特許請求範囲には金属コンタクトの記述

はない、金属コンタクトありなしに関わらず、このP+NPNsub

接合 type、すなわち dynamic thyrister type の受光

素子構造は萩原1975特許の特許請求範囲に含まれる。

結論として、以下の論理が成立する。

(1)1975年の萩原特許には 完全電荷転送の記述がある。

(2)1975年の萩原特許の受光素子構造体は5つの重要な

今の固体撮像装置の特徴を兼ね備えている。

(3)1975年の萩原特許の受光素子構造体は、

今話題のpinned photo diode そのものである。

(4) 従って萩原が 1975年にpinned photo diode を発明したことになる。

(5) 従って、萩原が 1975年に発明したpinned photo diode を

原理試作し、NECの寺西氏の1983年に IEDM で発表しが、

NECの寺西氏は、 pinned photo diode の発明者ではない。

(6)世界初めての pinned photo diode の原理試作は 1978年に

新聞発表の形で、SONYの盛田と岩間が、

学会では 萩原、阿部、岡田が、 FT image sensor の形で

発表している。

(7)1975年の萩原特許に添付に実施例の図には、萩原発明の

受光素子構造体、すなわち、pinned photo diode を

ILT CCD image sensor の形で事例として明示している。

(8) これとまったく同じ構造をNECの寺西氏の1983年に IEDM で

発表したが、SONYでは 1975年の発明から萩原を中心に原理

試作の努力は続けている。会社としては学会発表より、生産立ち

上げに注力した。そのおかげで社外にKnowhowが流れることも

なく、SONYが萩原が生んだ HAD 技術を武器に世界の image

senser 市場をほぼ独占するまでに至った。

***************************************************************************************

萩原良昭の出版図書の紹介

******************************************************************************************

人工知能パートナー(AIPS)を支える

デジタル回路の世界

補足資料(Appendix)

******************************************************************************************

ISBN 978-4-88359-339-2 C3055

本体 9000円+税

B5サイズ 上製 475ページ (ハードカバー)

TEL: 042-765-6460(代) 青山社

*******************************************************************************************

********************************

人工知能搭載の「賢い電子の目」

とそれを支える

デジタル回路の世界

をやさしく 紹介しています。

将来への展望を語っています。

若い技術者、大学の学生諸君には、

是非、読んでもらいたいです。

文系理系にかかわらず、

一般社会人の方でも、

高校数学程度の知識があれば、

じっくり時間をかけて楽しく読めます。

会社や大学の図書館で

是非一冊買ってもらってください。

そして、勉強してください。

頭の体操になります。

*************************

*****************************************************

萩原良昭の出版図書の紹介

*****************************************************

人工知能パートナー(AIPS)を支える

デジタル回路の世界

補足資料(Appendix)

*****************************************************

ISBN 978-4-88359-339-2 C3055

本体 9000円+税

B5サイズ 上製 475ページ (ハードカバー)

TEL: 042-765-6460(代) 青山社

*********************************************************

****************************************************

New Topic June 7, 2018

****************************************************

今回の課題はかなり technical です。 意欲ある若者には、

半導体産業人協会主催(SSIS)の半導体講座を受講すること

をお勧めします。 その中で 「賢い電子の目」 、the intelligent

AIPS image sennsor の講義を講師として担当しています。

*****************************************************

*********************************************************

.............SONY HAD sensor is the origin of our AIPS sensor................

*********************************************************

Please visit the following sites to learn about Sony HAD Sensor.

https://en.wikipedia.org/wiki/HAD_CCD

https://www.ptgrey.com/exview-had-ccd-ii-sensor-technology

https://en.wikipedia.org/wiki/Hole_accumulation_diode

https://www.sony.net/SonyInfo/News/Press_Archive/200002/00-007/

"HAD" technology for CTD (charge transfer device) sensor

that includes CCD,BBD,MOS and many kinds of other applications,

was invented by Yoshiaki Hagiwara at Sony in 1975.

****************************************************

Dear college students, professors and friend,

please judge for yourself.

Who is the inventor of the pinned photo diode

which has the light sensing P+N junction

with complete charge transfer operation mode like CCD ?

And also, who is the true inventor of the virtual phase CCD ?

*********************************************************

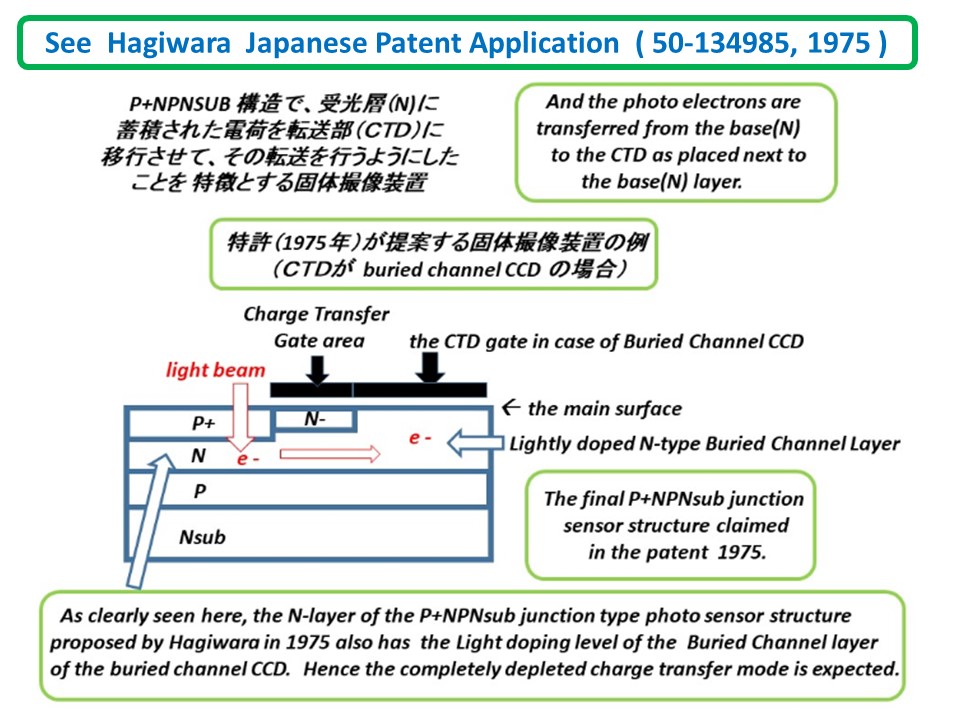

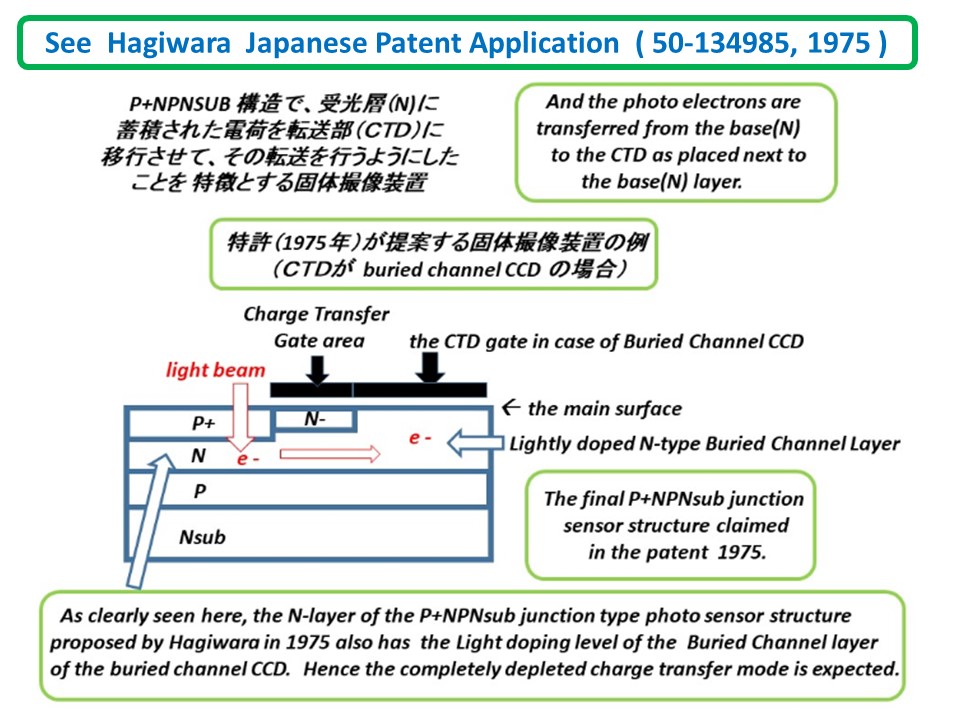

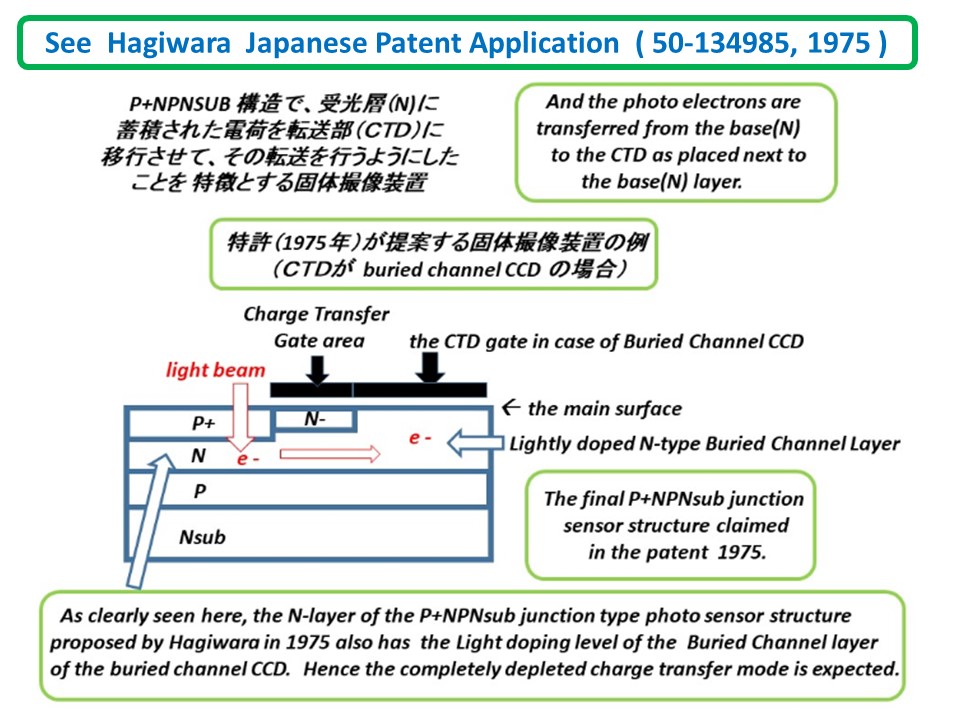

The following figures may give a hint to answer the above questions.

Please study the figures drawn by Yoshiaki Hagiwara at SONY

for the first time in the world in 1975.

**********************************************************

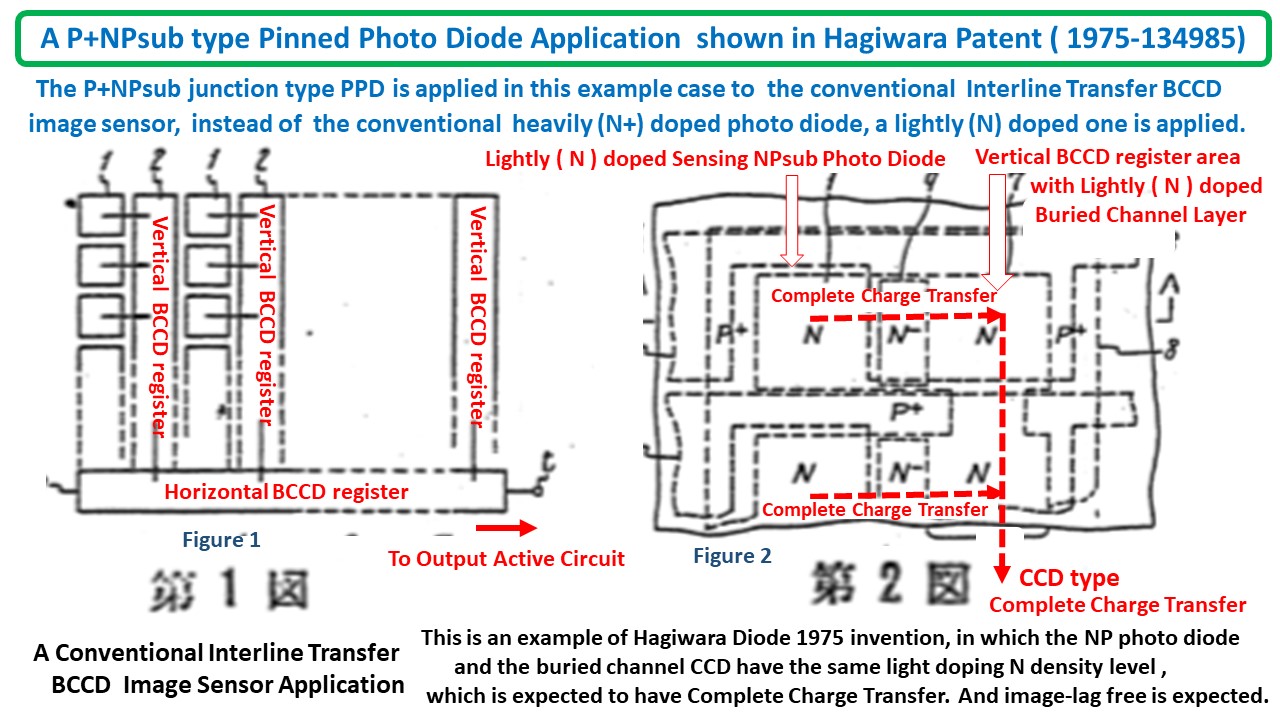

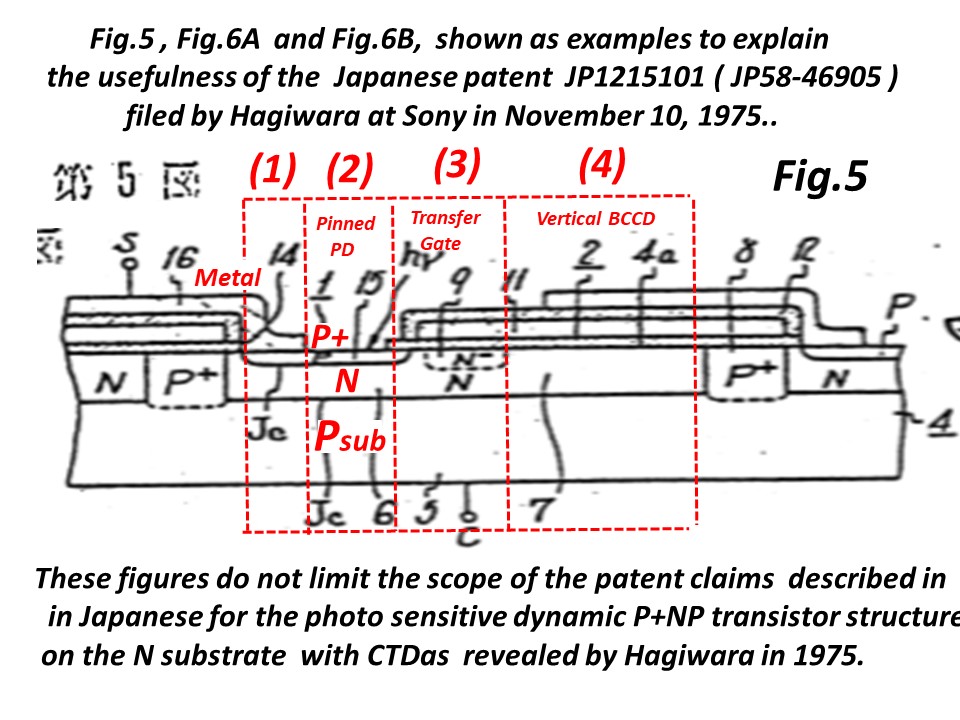

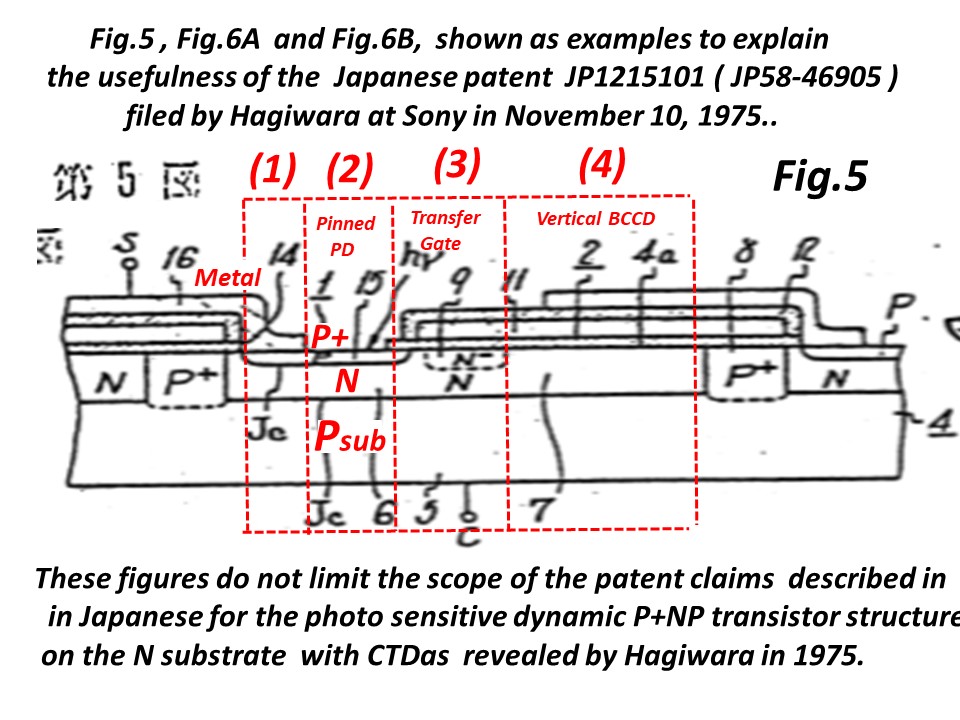

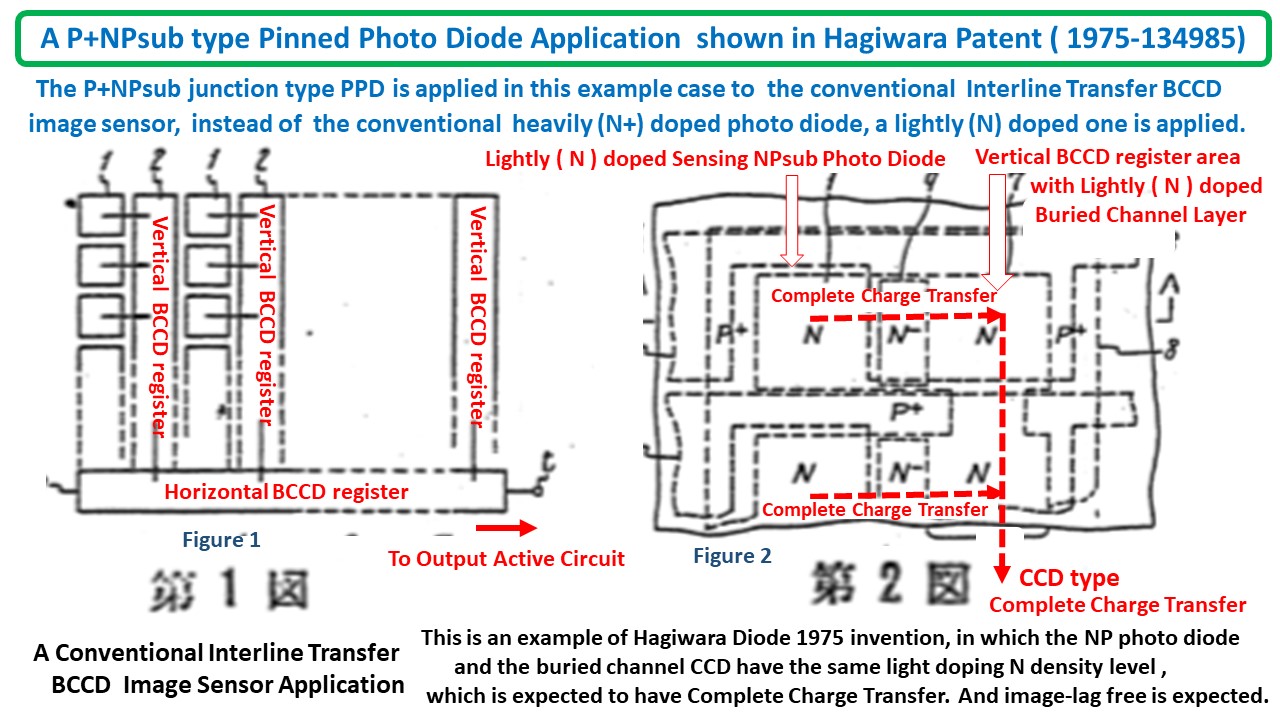

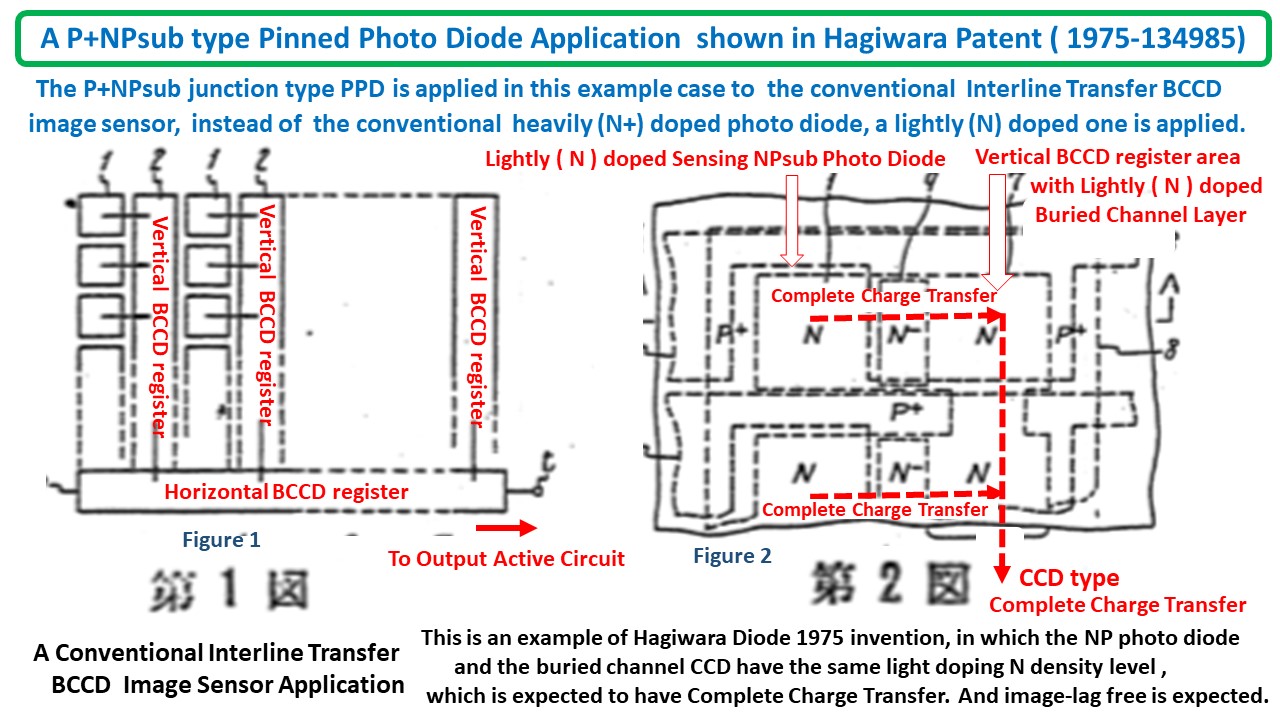

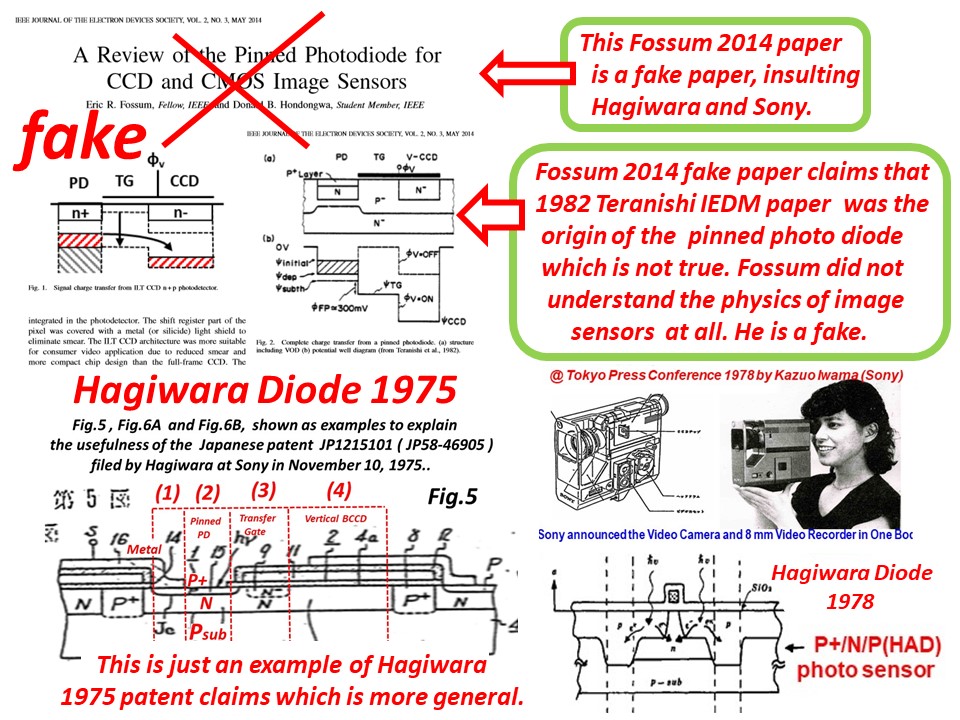

See The 1975 patent claim of Hagiwara Photo Diode

The 1975 patent claim of Hagiwara Photo Diode

was on the (2) structure.

Hagiwara drew the Fig.5 as an example

which shows a combined structure

of the following four parts.

(1) the pinned photo diode by a metal contact

(2) the surface exposed, not shown but protected

by SiO2 layer over , the pinned photo diode

which can be pinned somewhere outside.

(3) The buried channel CCD transfer Gate

with the lightly doped N- layer

(4) The read-out buried channel CCD

to transfer the signal charge (electons)

to the output buffer circuts.

Image sensor experts can easily recognize these four parts

and their operations of complete charge transfer

(1) and (2) for the pinned photo diode charge transfer modes,

as claimed in Hagiwara 1975 patent claim.

So it is concluded that Hagiwara is the inventor of

the pinned photo pinned diode.

the combination of (2) and (3) is now known and named as

the virtual phase CCD charge transfer mode,

which is shown in ig. 5 drawn by Hagiwara in 1975.

So it is concluded that Hagiwara is the inventor of

the virtual phase CCD .

(3) and (4) are for the buried channel CCD charge transfer mode

invented by Bell Lab in 1969,

which was studied intensively when he was a PhD student

under the lederships of Prof. C. A. Mead ,

Prof. Tom McGill and Prof. James McCaldin.

Hagiwara also drew Fg.6 in his patent in 1975.

Fig.6 shows many important features of pinned photo diode.

And Hagiwara phtoto diode defined in his 1975 patent

may be identical to the pinned diode ?

Please judge by yourself.

By just looking at Fig.6, image sensor experts

may be easily led to obesrve the following facts:

(1) Empty Potential Well impolying the N region

is completely depleted, so there is no photo-electrons left.

All the electrons have been transfered complete;y

to the adjacent to the CCD

which is the most important feature

of the pinned diode

(2) pinned photo diode with the P+ region

connnected to the metal wiring.

This is just an exmample which

does not limit the scope clained in the patent

(3) P+N VOD mode as an example.

NP VOD is not shown, but by symmetricity arguments

P+N VOD leads to NP VOD.

Furthermore, one can exxpect P+NPNsub VOD modes.

(4) the dashed line to show the flat potential (surface)

of the photo electrons packet in the potential well

(5) At the full storage level , over-flowing electrons

are draining to the P+ region in this P+N VOD mode

This empty potential well (1) shown above

was drawn by Yoshiaki Hagiwara at Sony in 1975

for the first time in the world.

This fact may prove that Hagiwara is the inventor of

the pinned photo diode

****************************************************

The world did not know the empty potential well ,

drawn by Yoshiaki Hagiwara at Sony in 1975,

which is the evidence

of the complete charge transfer operation mode

of the pinned photo diode.

****************************************************

.

Image sensor device experts may be convinced that

Hagiwara is the true inventor of the pinned diode,.

the the pinned P+N junction photo sensing device,

which was revealed as the photo sensitive emitter junction

of a PNP transistor on the N type substrate,

that was defined clearly in the short Japanese paragraph

in the Japanese patent claim written by Hagiwara in 1975.

Unfortuantely the world did not know this fact

simply because the Japanese patent filed

by Hagiwara in 1975 was described in Japanese.

Moreover, the world was confused

because Hagiwara did NOT in his patent draw a figure

of the simple PNP transistor on the N type substrate

which is well known by bipolar process and device engineers.

An expert can easily picture himself in his mind, however,

and quickly can draw on a sheet of paper

the structure of the PNP transitor on the N type substrate

which also can function as a pinned photo diode.

As a matter of fact, Hagiwara worked at SONY

in the summers of 1971 and 1973

as a part-time student engineer in the bipolar process lines

in the SONY Atsugi Plant, Kanaggawa Japan,

where the bipolar transistors and ICs were

in full production for SONY color televisions in 1970s.

In either way, it is a true fact that

the empty potential was drawn by Hagiwara in 1975

which is the evidence of the complete charge transfer

in the pinned diode with the completely empty N storage region.

In 1970s, it was widely known that CCD is important

becuase of the built-in complete charge transfer mode

which results in a low lag picture of high quality.

Hagiwara did NOT describe anything

about the low imager lag effect

in his 1975 patent claimed structure

but image sensor experts can see easily that

the empty potential well drawn by Hagiwara,

in 1975 for the first time in the world

implies the low image lag effect

in high speed action pictures.

Hagiwara gave a hint by showing the empty potential well

that explains one usefulness aspect of the pinned diode structure,

that is, the low image lag effect in high speed action pictures.

As claimed and defined clearly Hagiwara 1975 patent,

the N storage region of the dynamic PNP tansistor

is directly conneted to CTD near by.

CTD, that is charge tranfer device in short,

does not have to be CCD, it can be a type

of CMOS imagers in full production these days.

However, Hagiwara chose CCD as an example

in the figure in his 1975 patent

to explain another useful aspect

which is now called virtual charge transfer opeation.

As seen in the figure given as an example structure,

the floating dynamically operationable N layer

has a smooth transition

from the left structure of

the vertical stack of the exposed SiO2 on the pinned P+layer

over the N layer in the P type substrate

to the left structure of

the vertical stack of the exposed SiO2 on the CCD metal gate

over the N - and N layer in the P type substrate.

It is now clear that this protion of the structure was

revealed for the first time in the world in 1975

in a figure drawn by Hagiwara, in Sony, 1975.

Experts can easily see that this is the structure of ,

the virtual phase CCD charge transfer,

that is, the combination of two complete transfer modes.

One transfer mode is the pinned diode charge trasfer mode,

and the other is the buried channel charge transfer mode.

In short , by drawing the figure of two structures

next to each other, along the line of the semiconducter surface,

Yoshiaki Hagiwara in 1975 disclosed

for the first time in the world

the device structure of the vertual phase CCD.

From the combinational structure revealed in the figure

which was drawn by Hagiwara in 1978,

image sensor device experts can be convinced that

Hagiwara was the true inventor of the virtula phase CCD.

Hagiwara 1975 patent does not care about

how the proposed dynamic photo sensing structure operates.

That is , any company can use the structure,

whatever way they wish as long as

the company pays the patent fee to SONY.

Sony as the patent holder comapny has the right to claim

the patent fee to any company using the structure.

****************************************************

*****************************************

萩原良昭の出版図書の紹介

*****************************************

人工知能パートナー(AIPS)を支える

デジタル回路の世界

*****************************************

ISBN 978-4-88359-339-2 C3055

本体 9000円+税

B5サイズ 上製 475ページ (ハードカバー)

TEL: 042-765-6460(代) 青山社

*********************************************************

********************************************************

A story of 1975 Hagiwara Photo Diode

*********************************************************

Does the Hagiwara photo diode

described in his 1975 patent

differ from the pinned diode ?

Please study the difference if any.

Hagiwara thinks they are the same.

Is he wrong ?

****************************************************

The original PPD structure, while invented in 1975

by Yoshiaki Hagiwara in the

form of P+NPNsub junction photo seinsing element,

the 1978 FT CCD application by Hagiwara, and

the Teranishi's 1983 low lag ILT CCD application,

shares a strong resemblance

to the Hynecek virtualphase CCD structure,

with the exception of the VOD

The two inventions

were solving different problems

with essentially the same device structure

and operating principles.

In 1975, Hagiwara at Sony filed a patent application

on bipolar structures for CCDs

in which a pnp vertical structure was disclosed,

among several structures [24].

In 1975, Hagiwara at Sony filed a patent application

on a photo sensing vertically stacked P+NPNsub structure

with the floating N base region

as the storage for the photo electrons

from which the photo electrons are to be transfered

to a charge transfer device[24].

.

*****************************************

萩原良昭の出版図書の紹介

*****************************************

人工知能パートナー(AIPS)を支える

デジタル回路の世界

*****************************************

ISBN 978-4-88359-339-2 C3055

本体 9000円+税

B5サイズ 上製 475ページ (ハードカバー)

TEL: 042-765-6460(代) 青山社

*********************************************************

***************************************************

Dear college students, professors and friends,

please read the following very interesting review paper.

***************************************************

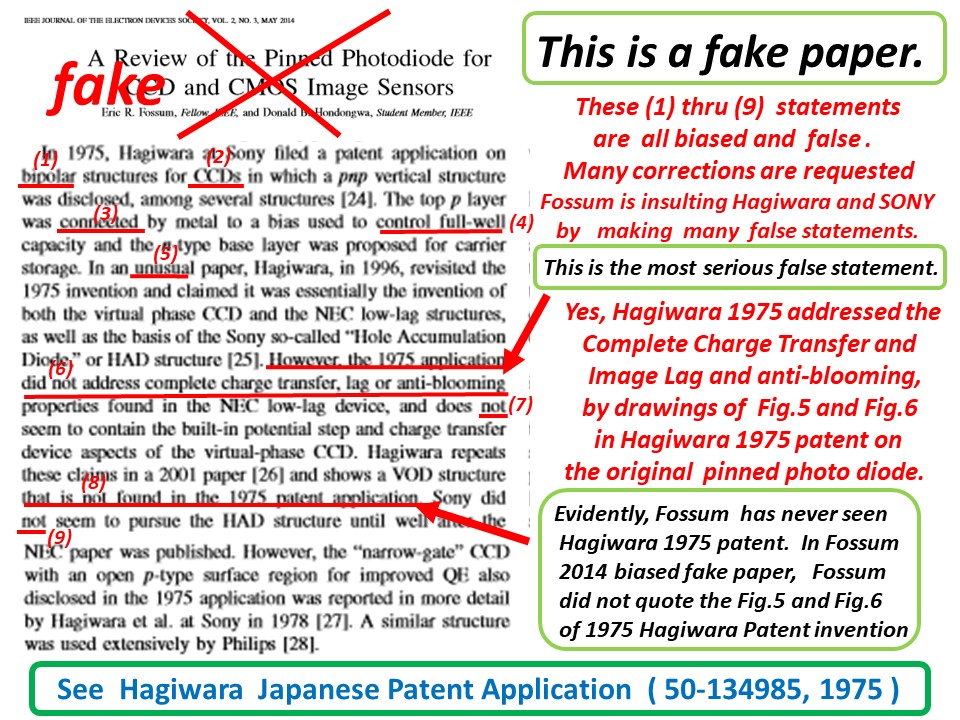

***************************************************

" A Review of the Pinned Photodiode for CCD and CMOS Image Sensors"

by Eric R. Fossum and Donald B. Hondongwa , which was published in

IEEE JOURNAL OF THE ELECTRON DEVICES SOCIETY, VOL. 2, NO. 3, MAY 2014

****************************************************************************

There are many false descriptions in this paper,

maybe simply because of lack of information ?

But it is a very good educational paper for college students

if the false descriptions are all corrected.

I belive poeple can say anything,

but the false comments shoud be corrected.

The truth shall make you free.

Yoshiaki Hagiwara in CalTech from 1967 to 1975.

***************************************************

*******************************************************************

The following is the quoations from the paper

by Eric R. Fossum and Donald B. Hondongwa.

Corrections are requested as followed.

*******************************************************************

C. Other Contributions to the PPD Invention

The PPD structure, while invented for low lag ILT CCD application,

shares a strong resemblance to the Hynecek virtualphase CCD structure,

with the exception of the VOD.

*******************************************************************

(1) This comment is WRONG. Correctioms are requested as followed

*******************************************************************

The original PPD structure, while invented in 1975 by Yoshiaki Hagiwara in the

form of P+NPNsub junction photo seinsing element, the 1978 FT CCD application

by Hagiwara, and the Teranishi's 1983 low lag ILT CCD application,

shares a strong resemblance to the Hynecek virtualphase CCD structure,

with the exception of the VOD

The two inventions

were solving different problems with essentially the same device structure

and operating principles.

*******************************************************************

*******************************************************************

In 1975, Hagiwara at Sony filed a patent application

on bipolar structures for CCDs

in which a pnp vertical structure was disclosed, among several structures [24].

*******************************************************************

(2) This comment is WRONG. Correctioms are requested as followed

*******************************************************************

In 1975, Hagiwara at Sony filed a patent application

on a photo sensing vertically stacked P+NPNsub structure

with the floating N base region as the storage for the photo electrons

from which the photo electrons are to be transfered to a charge transfer device[24].

*******************************************************************

*******************************************************************

The top p layer was connected by metal to a bias used

to control full-well capacity

*******************************************************************

(3) This comment is WRONG. Correctioms are requested as followed

*******************************************************************

An example case is depicted in a figure in which

the top P+ layer was connected by metal to a bias used

to control not only full-well capacity but gamma corection

and high beam action picture-acquisition for highly intelligent

AIPS camera Hagiwara had been dreaming of.

Therefore from the figure, the P+ layer can be set, or pinned

to any external voltage value. Hagiwara had already in his mind

the concept of the pinned diode now universally ell known.

It should be noted that the patent claim does not say

any comments on the metal connection.

Therefore the p layer can be connected to anything anywhere.

In 1978, another example of a P+NPsub photo sensing structure

with the P+ layer connected to the Psub substrate

was demonstrated in one-chip FT CCD imager for 8 mm video camera

*******************************************************************

*******************************************************************

In an unusual paper,

*******************************************************************

(4) This comment is WRONG. Correctioms are requested as followed

*******************************************************************

In a review paper,

*******************************************************************

*******************************************************************

Hagiwara, in 1996, revisited the 1975 invention and claimed

it was essentially the invention of both the virtual phase CCD

and the NEC low-lag structures, as well as the basis

of the Sony so-called “Hole Accumulation Diode,” or

HAD structure [25].

*******************************************************************

(5) This comment is WRONG. Correctioms are requested as followed

*******************************************************************

Hagiwara, in 1996, revisited the 1975 invention and claimed

it was exaclty the same semiconductor photo sensing structure

vertical stacked picture element of both the virtual phase CCD

and the NEC low-lag structures, as well as the basis

of the Sony so-called “Hole Accumulation Diode,” or

HAD structure [25].

*******************************************************************

*******************************************************************

However, the 1975 application

did not address complete charge transfer, lag or anti-blooming

properties found in the NEC low-lag device, and does not seem

to contain the built-in potential step and charge transfer device

aspects of the virtual-phase CCD.

*******************************************************************

(6) This comment is WRONG. Correctioms are requested as followed

******************************************************************

Hagiwara's 1975 patent claim was intended only to claim rights

on the device structure. His patent does not restrict any applications

with any operational modes on his application. Howevee, for the

first time in the world he drew the electrically empty potential

well of the floating N base storage region for majrity charge

photo electrons in one of the patent figures.

This is the evidence that Hagiwara did address the complete

charge transfer by drawing in the N base photo electrons storage

an empty potential well which results no lag action picture.

*******************************************************************

Hagiwara repeats these claims

in a 2001 paper [26] and shows a VOD structure that is not

found in the 1975 patent application.

*******************************************************************

(7) This comment is WRONG. Correctioms are requested as followed

*******************************************************************

Hagiwara repeats these claims

in a 2001 paper [26] and shows a VOD structure

of the P+NPNsub vertically stacked one

which is not shown in the figures in the patent

becuse of its simplicity, but definedexactly

in the patent claim in Japanese.

Sony did not seem

to pursue the HAD structure until well after the

NEC paper was published.

*******************************************************************

(8) This comment is WRONG. Correctioms are requested as followed

*******************************************************************

Sony did pursue the HAD structure,

first in the 1978 demosntration of FT CCD imagers

with the SiO2 exposed P+NPsub photo senising elemnt

with the P+ and Psub connected without VOD.

then in the production model of ILT CCD iamgers

with conventioanl lateral

with the SiO2 exposed P+NPsub photo senising elemnt

with the P+ and Psub connected without VOD.

This product is called HAD sensor camera !

hen in the production model of ILT CCD iamgers

with the SiO2 exposed P+NPsub photo senising elemnt

with the P+ and Psub connected without VOD.

This product is called super HAD sensor camera !

*******************************************************************

*******************************************************************

until well after the

NEC paper was published.

*******************************************************************

(9) This comment is WRONG. Correctioms are requested as followed

******************************************************************

It is easy to publish a proto type in the technical

company, but HARD to produce as the product !

*******************************************************************

]

*******************************************************************

However, the “narrow-gate” CCD

with an open p-type surface region for improved QE also

disclosed in the 1975 application was reported in more detail

by Hagiwara et al. at Sony in 1978 [27].

*******************************************************************

(10) This comment is too short. Correctioms are requested as followed

******************************************************************

However, the “narrow-gate” CCD

with an open p-type surface region for improved QE also

disclosed in the 1975 application was reported in more detail

by Hagiwara et al. at Sony in 1978 [27].

It is not open P type surface, it it pinned to the substrate volatage

like the one in ILT aplication.

*******************************************************************

*******************************************************************

A similar structure was used extensively by Philips [28].

*******************************************************************

(11) This comment is too short.. Correctioms are requested as followed

******************************************************************

A similar structure was used extensively by Philips [28]

in 1983, five years after .....

28] G. Beck et al.,

“High density frame transfer image sensor,”

Japanese J. Appl. Phys., vol. 22 supplement 22?1,

pp. 109?112, 1983.

The PPD, as it is most commonly used today, bears

the strongest resemblance to the Teranishi et al. ILT CCD device.

*******************************************************************

*******************************************************************

Thus, these days Teranishi is considered as the primary

inventor of the modern PPD [29].

*******************************************************************

(12) This is a wrong conclusion. Correctioms are requested as followed

********************************************************************

Since the 1975 Hagiwara photo diode is idenical to the modern PPD,

Thus, these days Hagiwara is considered as the primary

inventor of the modern PPD[29]..

*******************************************************************

*****************************************

萩原良昭の出版図書の紹介

*****************************************

人工知能パートナー(AIPS)を支える

デジタル回路の世界

*****************************************

ISBN 978-4-88359-339-2 C3055

本体 9000円+税

B5サイズ 上製 475ページ (ハードカバー)

TEL: 042-765-6460(代) 青山社

*********************************************************

***********************************************

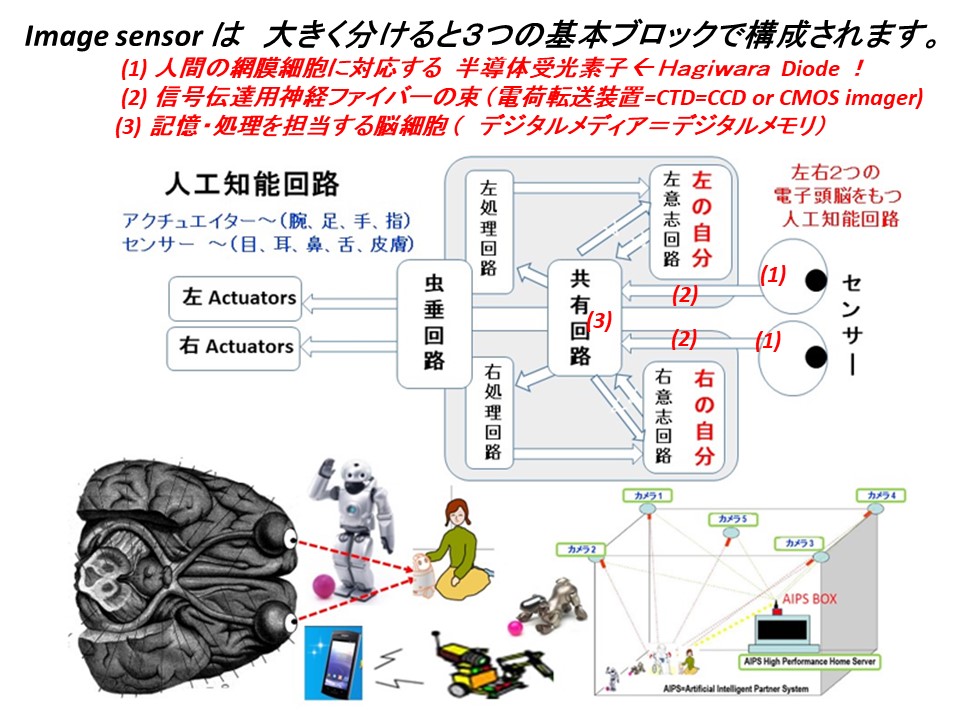

この 賢い AIPS image sensor は、

萩原が ソニー時代にその技術開拓に挑戦した

ソニーのHADセンサー と Play Station Processor

の 融合技術から生まれます。

その展望と夢(vision)について、

2008年7月にソニーを定年退社後、

ヨーロッパの国際集積回路技術の学会で

招待講演を受けて説明しています。

***********************************************

まずは、SONY の HAD sensor のご紹介です。

*********************************************************

.............SONY HAD sensor is the origin of our AIPS sensor................

*********************************************************

Please visit the following sites to learn about Sony HAD Sensor.

https://en.wikipedia.org/wiki/HAD_CCD

https://www.ptgrey.com/exview-had-ccd-ii-sensor-technology

https://en.wikipedia.org/wiki/Hole_accumulation_diode

https://www.sony.net/SonyInfo/News/Press_Archive/200002/00-007/

"HAD" technology for CTD (charge transfer device) sensor

that includes CCD,BBD,MOS and many kinds of other applications,

was invented by Yoshiaki Hagiwara at Sony in 1975

*********************************************************

実は、ここには、

SONY の HAD sensor に深く関係し、

萩原良昭が 1975年に 出願した

半導体受光素子の構造特許

の存在があります。

1975年萩原良昭申請のHADsensor基本特許

に深く関係するお話です。

******************************

SONYは HAD sensor を

自社ブランドとして 世界に紹介し、

超高感度、低雑音、残像なしで、

かつ 高速 action pictureも誠実に撮りこむ

超高性能のHAD sensor 搭載カメラ

を世界中に提供しています。

*********************************************************

.............SONY HAD sensor is the origin of our AIPS sensor................

*********************************************************

Please visit the following sites to learn about Sony HAD Sensor.

https://en.wikipedia.org/wiki/HAD_CCD

https://www.ptgrey.com/exview-had-ccd-ii-sensor-technology

https://en.wikipedia.org/wiki/Hole_accumulation_diode

https://www.sony.net/SonyInfo/News/Press_Archive/200002/00-007/

"HAD" technology for CTD (charge transfer device) sensor

that includes CCD,BBD,MOS and many kinds of other applications,

was invented by Yoshiaki Hagiwara at Sony in 1975

*********************************************************

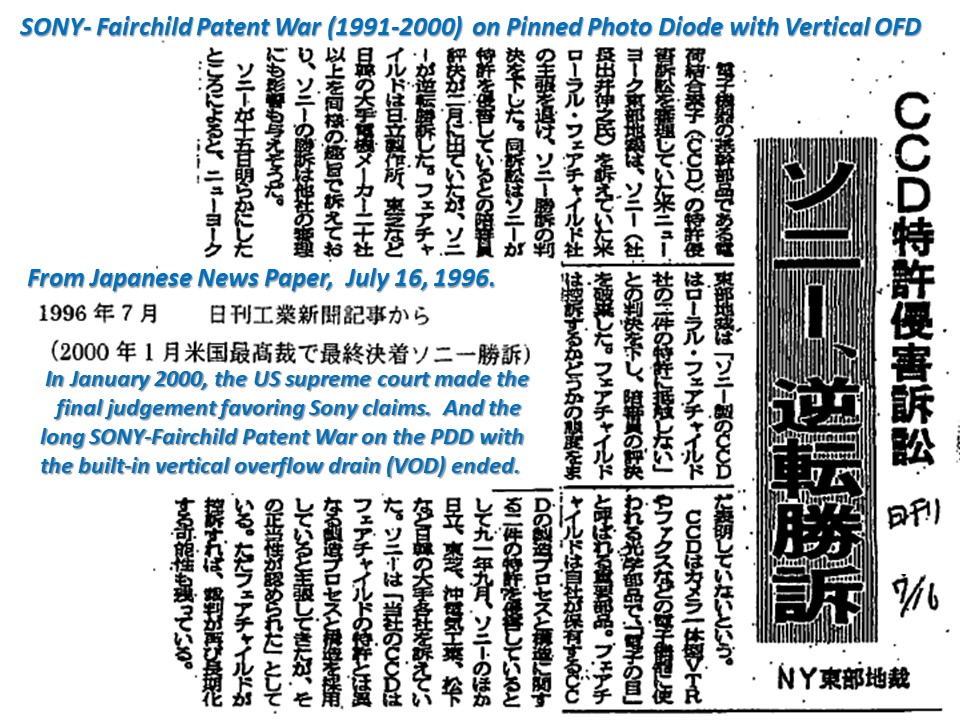

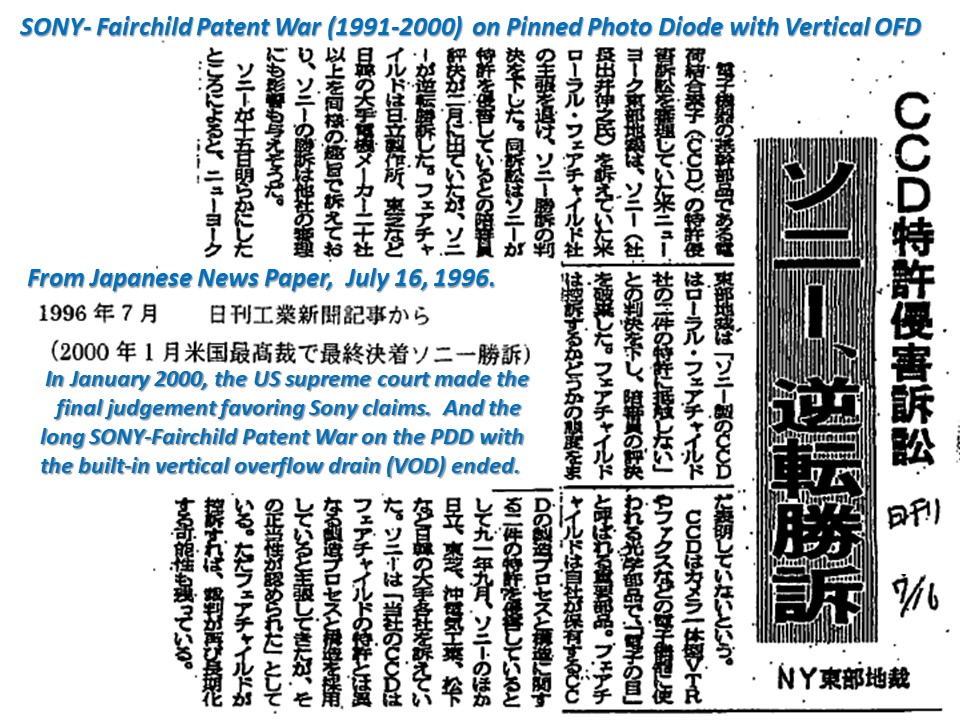

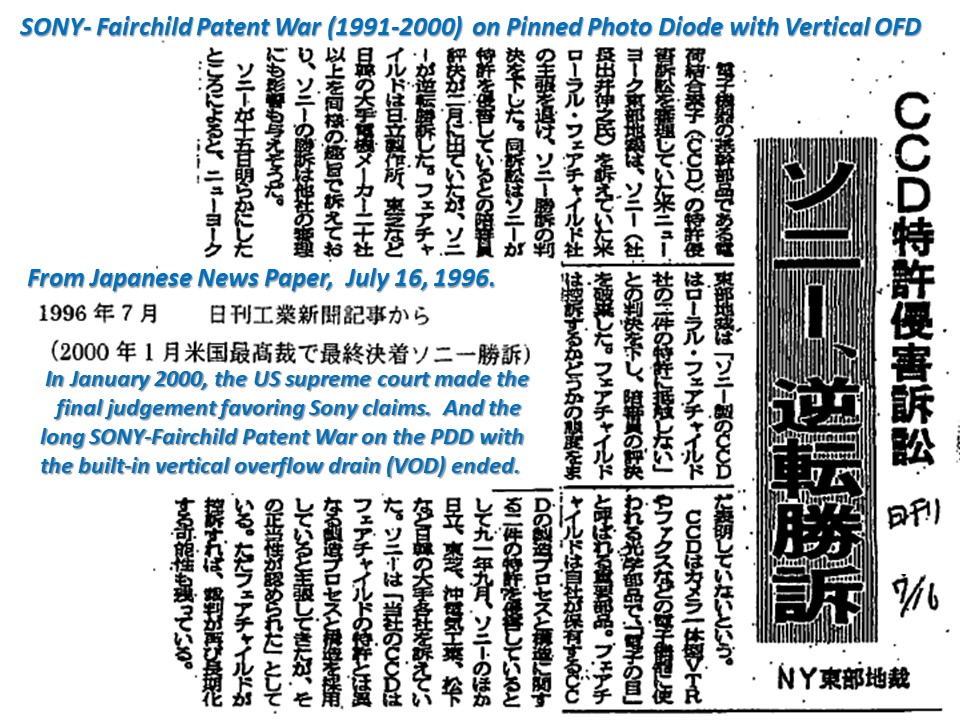

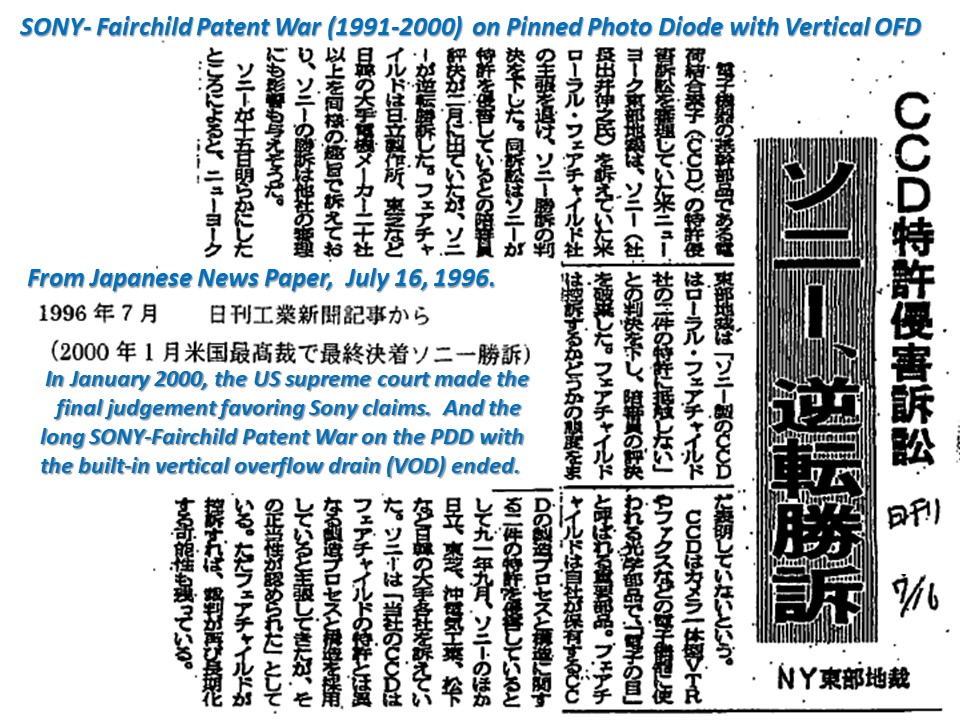

SONYの HAD sensor 誕生にまつわる

米国 Fairchild 社と SONY との特許紛争のお話

*********************************************************

*********************************************************

この紙面にも記載されていますが、米国 Fairchild 社は自社が保有

する2つの基本特許でSonyを訴えていました。Sonyはそれに対抗し

て、Sony 社員保有の 「神戸 CCD process 基本特許」と 「萩原

image sensor 基本構造特許」で対抗しました。その請求額は当時で

600億円~800億との話でした。 負けていたら、SONYの年間売り

上げが1兆円近くなる今ですから、その1%としても、毎年膨大な額の

特許料の支払いとなるところでした。

ILT CCD imager の技術開発では NECは SONYを抜き、学会

発表にも積極的に発表し、外国の技術者と情報シェアに努力してい

ました。当時、 DRAMで一人勝ちしていた日本の代表企業として、

NECは、勝ち負けの苦い感情を残す半導体戦争の経験を2度とす

ることのない道を探っていました。

一方、SONYは、ILT方式のCCDの量産立ち上げに、開発部隊総力

をあげて全力努力集中していました。暗黙を続けていました。。。

Sonyは早くから Type(1)は生産候補からはずしました。

Type(1)構造は、 従来構造のCCDのMOS容量型受光素子構造です。

低残像で、低雑音の映像を提供してくれますが、上部に金属端子があり

光感度が悪い構造となっています。

Sony は、1975年に萩原が考案した受光素子構造をまずは FT CCD image

sensor に採用しました。SONYはまず、 (2) と (3) の構造はchip全面に

ボロンイオンを打ち込み、その濃度と注入エネルギーを調整しならが条件

出しをしながら、感度と雑音で最適値を求めました。

受光部に P+NPsub 構造(3)を採用した FT 型 imager では、 P+ 層を

基板(Psub)と導通形としました。 萩原が1975年に申請した構造特許

では、その実施例では 上部のP+に金属コンタクトがあり、このP+領域が

受光素子の外部電圧に固定(pinning)されていることを提案する図ですが、

SONYで 1978年試作の FT 型 imager では、このP+を基板Pと導通

させることにより、P+層を基板(P)電圧に固定(pinning)した構造になってい

ます。1975年に萩原により考案されたこの構造は、まずプロセスが単純な

FT 型 CCD imager で 条件出しを実行し、 最適条件を見つけ出して

続いて、ILT型 CCD imager の受光部にも適用され開発を進めました。

最終的には、まず構造(3)の受光構造で、横型OFD機能を採用して

HAD sensor 採用の ILT型 CCD imageの生産を開始し、まず、

生産・販売・信頼性評価に注力し世界発のパスポートサイズのビデオ

カメラを商品化することに成功しました。

構造(3)で充分生産実績を進めて、KNOWHOWを積み、慎重に構造(4)の

生産に入りました。

その効果が出て、早期に、1975年の萩原構造特許で提案する構造(4)の受光

構造で、かつ、縦型OFD機能を採用して HAD sensor 採用の ILT型 CCD

image搭載のカメラを商品化することに成功しました。

萩原の1975年特許において、特許請求範囲本文では、その提案構造を

bipolar tranistor 構造と呼んでいます。 ここで bipolar transitorには

通常の電流増幅に static 動作をするのは周知です。しかし、この特許の

非常に短く簡潔な請求文を読んで、「これは bipolar transitor じゃない、

萩原は半導体物理とデバイス物理を理解していないでは?」と先輩に意見

されたことがあります。その時、bipolar transitor でも 電流 ON modeも

あれば、 電流 OFF mode もあり、 static mode もあり、 DRAMの

dynamic mode の様な、すなわち、 source 領域を floating 動作させる

dynamic mode があります。

この萩原特許で提案する P+NPNsub 構造特許の実施例を示す図5の

中には、萩原が わざと base 領域と呼ぶ領域があります。すなわち、

図の中のN層のことになります。このN層は DRAMの読み書きする

NMOS プロセスの NMOS transistor で、souece 領域(N+) と基板(P)

の間にできる N+Ps接合容量において 通常 N+ を floating 状態に

して dynamic mode で 動作させます。 従来の MOS imager も、

同様で、受光構造として N+P 接合容量を使ってN+ に信号電荷を

蓄積します。 埋め込み channel CCD では、埋め込み channel を

floating 状態にして、 daynamic mode で、 charge transfer 動作を

させます。 そういう周知情報の延長思考で容易に萩原提案の受光

構造、P+NPNsub junction capacitance type の 光電子(HAD電子)

の蓄積領域であるN層は floating であると連想できます。実際、

萩原特許の図6Bには、この dynaimic 動作を明示する為 N層には、

完全に空乏化した時の empty potenrtial well を示す電位曲線が

描かれています。 これが この構造が、今の学会用語では、pinned

diode sensor であることの必要条件である Low Lag 効果を実現する

半導体素子となっています。

、

NECが試作発表した センサー部にP+NPNsub構造でNPNsub接合

の、つまり bult-in NPNsub transistor の punch-thru mode で、

すなわち、 この寄生 NPNsub transistor の base N 領域の電荷

を、完全空乏化転送 mode で、すなわち、結果的にbase N 領域

が完全に空乏化し、majority carrier の光信号電子がすべて取り除

かれ、その結果、base N 領域には 電子の電位曲線が、埋め込み

チャネルのCCDのN層が完全空乏化する時に生じる曲線と同じ様

な形状、すなわち empty potential well の曲線形状ととなることを

特徴としていました。

これは日本とアメリカの貿易摩擦という大きな問題、今でもかかえて

いますが、その貿易摩擦問題のいう大きな戦争(war)の中の1つの

戦場(batle)でのほんの一瞬の出来事(incident) のお話です。半導体

戦争がまだ激しかった時代の話です。今は HAD sensor のブランド

名でSONYが一人勝ちしています。世界のビデオ市場の半分近くを

占める時代になりました。

1975年に萩原良昭は 半導体受光素子の構造特許を申請しました。

これは 半導体受光素子 ( image sensor element )

の製造技術・KnowHow にも かかわる

基本構造特許(特許料請求権利が生じる部分)です。

特許内の具体的な実施例には特許権は主張していませんが、

この基本構造の有効性を証明するために

いろいろ新規な応用例や、

この構造の新規な動作 modeなどの説明図が

具体的な実施例として提示されています。

この半導体受光素子の製造を助けるヒントとなる情報が含まれます。

それらは、公開情報となり、各社自由に使用することが可能です。

*****************************************

萩原良昭の出版図書の紹介

*****************************************

人工知能パートナー(AIPS)を支える

デジタル回路の世界

*****************************************

ISBN 978-4-88359-339-2 C3055

本体 9000円+税

B5サイズ 上製 475ページ (ハードカバー)

TEL: 042-765-6460(代) 青山社

*********************************************************

*********************************************************

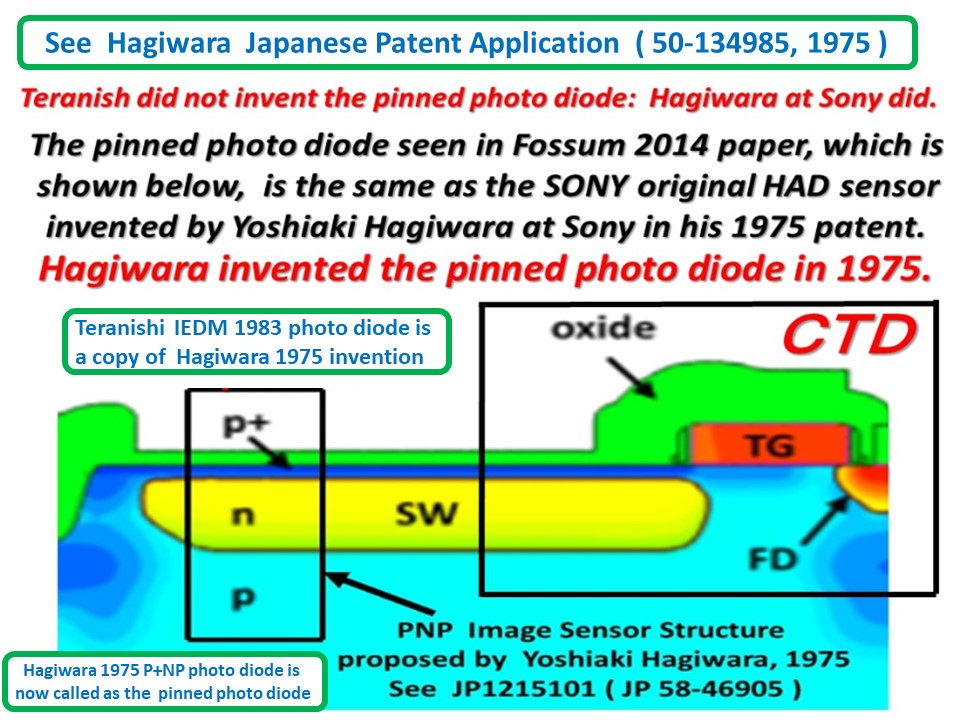

1975年萩原良昭申請のHADsensor基本特許について

**********************************************************

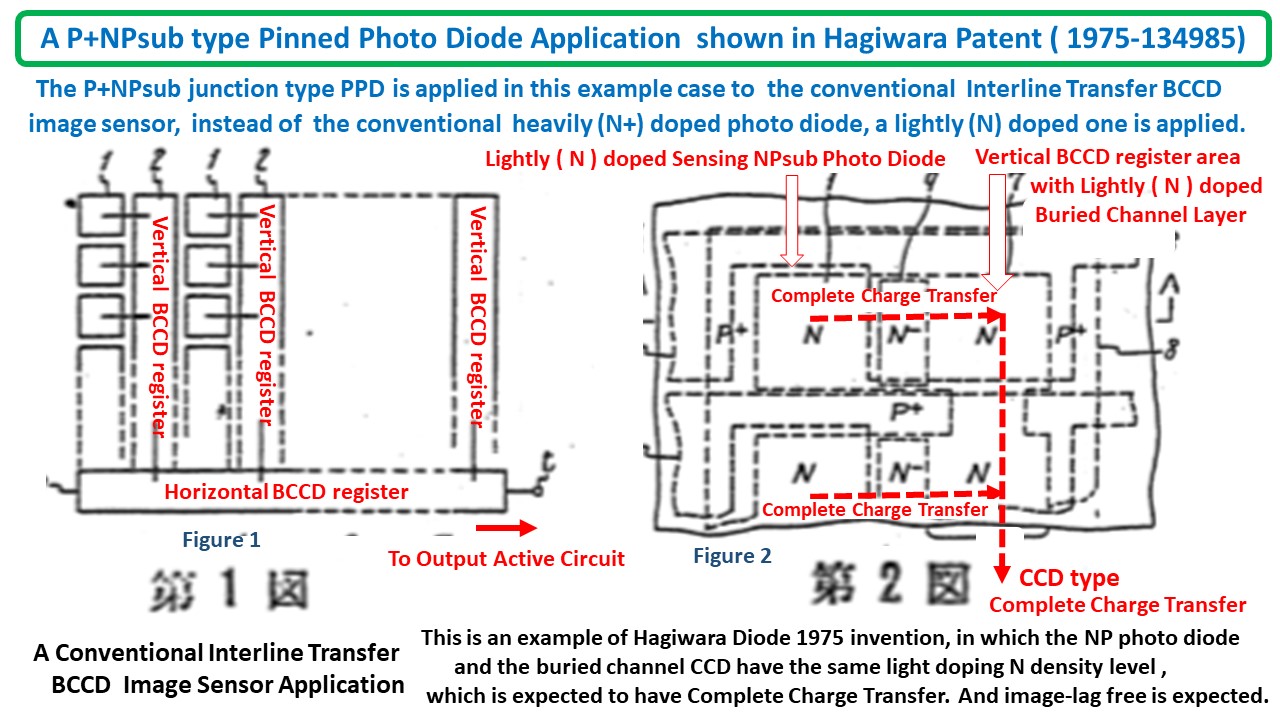

1975年に萩原良昭は 半導体受光素子の構造特許を申請しました。

上の図の1975年に特許出願した萩原考案の構造

と、下の図に示す、

寺西さんが1983年にIEDMで発表した受光構造

は同じものではないでしょうか????

Dear college students, professors and friends,

please judge for yourself. The truth shall make you free.

Yoshiaki Hagiwara

この上の図は 寺西さんが発明したことになっていますが、

彼はその構造特許を出しているのでしょうか?

この受光構造は pinned diode sensor と世間では

呼ばれていますが、1975年の萩原考案の構造特許と

同じではないでしょうか????

******************************

誰が本当の pinned photo diode ( HAD sensor ) の発明者でしょうか?

******************************

*****************************************

萩原良昭の出版図書の紹介

*****************************************

人工知能パートナー(AIPS)を支える

デジタル回路の世界

*****************************************

ISBN 978-4-88359-339-2 C3055

本体 9000円+税

B5サイズ 上製 475ページ (ハードカバー)

TEL: 042-765-6460(代) 青山社

*********************************************************

(1) Sony全体の開発部隊が総力をかけて本命である

Interline Transfer 方式 CCD one chip image sensor

の試作開発に専念する中、なかなかプロセスが複雑で、

きずが多く、完成 chip ができない状況が続いていました。

その頃、同時に Sonyのセット部門は、

次の 8mm ビデオの商品化プロジェクトが進んでいました。

CCDの試作品の完成がずるずると遅れる中、

ILT CCDの設計・評価も萩原が担当でしたが、

自発的に FT CCDの設計・試作・評価作業に挑戦し、

FT CCDは比較的工程数の少ないプロセスで

試作が可能なこともあり、早期に完成 chipができました。

1978年には、HAD 受光素子を採用した

FT CCD one chip image sensor の試作に成功し

VTRカメラ一体化8mmビデオをSONYは発表しました。

.

1978年の FT CCDでの HAD sensor の原理試作の成功から、

1980年に入り IT CCDでの HAD sensor の原理試作に成功

していましたが、Overflow 構造は絵素部の横につく方式でした。

なかなか、1975年の日本国特許の請求文通りに書かれた

HAD sensor搭載の Interline Line 方式 image sensor

の試作は難しかったと記憶します。

この一番下の 基板の Sub は 実施図にはありませんが、

特許請求文には P+NPNsub junction 構造を受光素子と

する固体撮像装置としています。この縦型VODがSONY

は遅れて試作・生産に成功し、HAD sennsor で1990年

になると市場を独占する勢いで事業化が進みました。

このHAD sensor の技術は学会発表よりも、開発・生産

と信頼性技術の構築を優先したことが幸いして高品質

高信頼性でかつこの図に見られる構造とその派生構造

改良構想で現在でも HAD sensor の brand で

世にいいものを送り出しています。

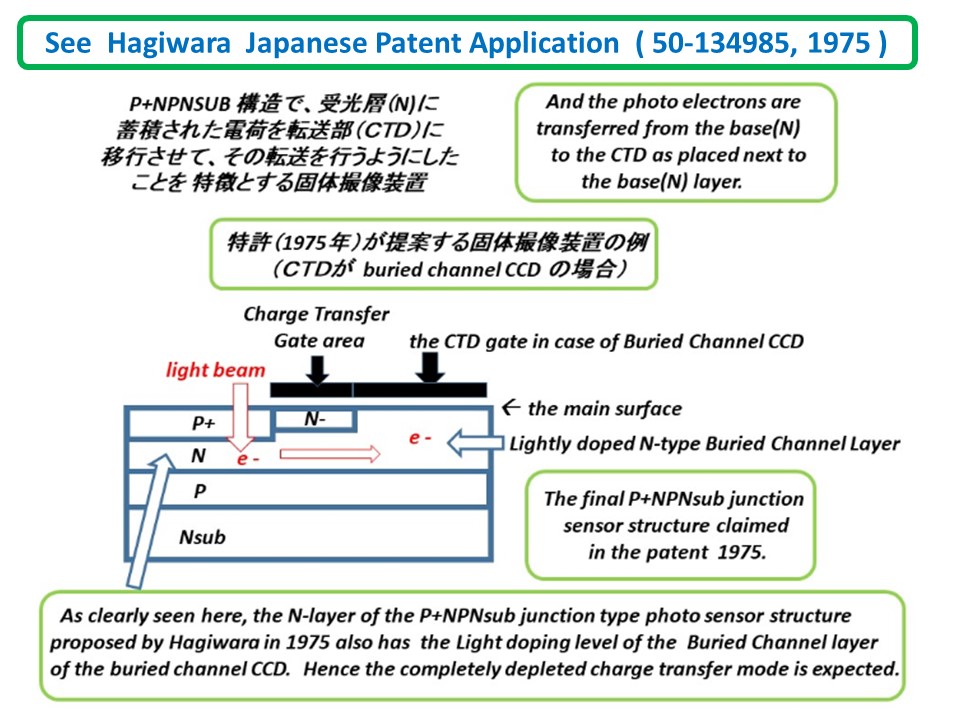

(1)実施例の図5には、 半導体基体(Nsub)は描かれていませんが、

この図はあくまで実施例の1つの特許の請求範囲を制限するものでは

ありません。 特許請求文には明確に 基体(Nsub), 第1領域(P)、

第2領域(N)、それに emitter 接合 (P+N接合)をつけるとあり

ます。図5図から、光信号電荷を蓄積する領域を第2領域としています。

また、N層の完全空乏化転送を示す Empty Potential Well の曲線図も

この特許の図6Bに挿入しています。この機能がこの HAD sensor

にはあることになります。

図6の事例ではNsub の存在はありまんが、請求文では

はっきりと基体(Nsun)と明記してNsubの存在が特許

請求文に記載しています。

*****************************************

萩原良昭の出版図書の紹介

*****************************************

人工知能パートナー(AIPS)を支える

デジタル回路の世界

*****************************************

ISBN 978-4-88359-339-2 C3055

本体 9000円+税

B5サイズ 上製 475ページ (ハードカバー)

TEL: 042-765-6460(代) 青山社

*********************************************************

SONY厚木工場の半導体部門に1971年の夏と

1973年の夏に自習生として訪問、品質評価室

の宇野主任が指導官となり当時のSONY半導体

特に、 Bipolar Transistor のプロセス flow を

学びました。 その時に学んだことを土台として

特許が PNP transistor の dynamic 動作、

すなわち、 base 領域の完全空乏化による、

CCD like の、隣接する CTDへの転送を

特徴とする固体撮像装置となっています。

CTDは MOSでも CCDでいいことは周知

としています。また PNPNsub 構造は本来

thyrister 構造となり、構造が複雑になること

に比例して期待されるそのoperation mode

も多様化することは簡単に理解できます。

構造だけ明確に特許請求文で定義すれば、

その構造に関係する動作 mode のほんどは

どんなに複雑なものでも新規なものでないの

なら 大学生が学ぶ教科書に掲載されています。

実際、 thyrister の動作原理は多様で受光時は

dynamic junction capacitor の sandwich と

機能し、過剰電荷の放流(drain)の場合は

P+N接合, NP接合、NPNsub のpunch thru

などの VOD 機能も 構造特許を取得して

いれば、他社から 動作特許を請求されても

高い特許料を支払わなくても逃げ切れること

になります。そういう意味で、Sony の HAD

sensor 技術が この Hagiwara1975特許

に基づくものなら HAD構造でSONYは

他社に特許料を支払うことはないはずです。

*******************************************************

最後に 1975年に出願した特許請求文 を

ここにそのまま掲示します。

*******************************************************

1975年11月10日特許申請

発明の名称 固体撮像装置

発明者 萩原良昭

******************************************************

特許請求の範囲

(1)半導体基体(Nsub)に、

(2)第 1 誘電型(P)の第半導体領域(Pregion)と、

(3)之の上に形成された第2の誘電型(N)の

第2半導体領域(Nregion)が形成されて

(4)光感知部(Nregion)と

之よりの電荷を転送する電荷転送部(CTD)とが

上記半導体基体の主面に沿う如く配置されて成る

固体撮像装置に於いて、

(5)上記光感知部の上記第2半導体領域(Negion)に

整流性接合(junction)が形成され、

該接合をエミッタ―接合(emiiter junction)とし、

上記第 1 及び第2半導体領域の接合を

コレクタ接合(collector junction)とする

トランジスタ(transistor)を形成し、

(6)該トランジスタ―のベース(base)となる

上記第2半導体領域(N)に光学像に応じた

電荷(HAD electron)を蓄積し、

ここに蓄積された電荷を

(7)上記転送部(CTD)に移行させて、

その転送(charge transfer action)を行うようにしたことを

特徴とする固体撮像装置 ( solid state image sensor )。

としています。

******************************************************

******************************************************

現在、Sony の HAD sensor と 一般に pinned diode sensor とは

次のような構造上の共通点があります。それが同一のものである

ことを判定するには詳細に両者の構造に精通する必要があります。

(1) 構造が HAD sensor は P+NPNsub 構造としている。

P+NP構造の受光部を採用して IT CCDの CTDを

具体的に使った実施例を提示している。

pinned photo diode は P+NPsub 構造をしている。

P+ の電圧は固定化 ( pinned ) 状態であること。

pinned photo diode では、P+領域は P type substrateと

導通しているが、HADsensor では、P+NPNsubのP+端子は

自由な外部電圧で固定化(pinned) してもよいことを

実施図で提示しているが、これは特許請求範囲を

狭め、制限するものではない。特許請求範囲には

金属コンタクトの言及はなくい。

また、P+NP の受光構造を SONYは 1978年に

frame transfer 方式 CCDの 受光部の構造に

採用し、この P+NP構造を受光構造として、

P+と基板Pとを導通させている、

(2) HAD sensor も pinned photo diode もともに、

CCD 転送の様に image lag free を可能とする

「完全空乏化転送」が可能となる構造をしている。

萩原のHAD特許1975には図6Bに中に

電荷蓄積領域N層内の完全空乏化状態を意味する

empty potential well の曲線図がある。

この図6Bが その evidence となり、HAD sensorは

image lag free を提供する受光構造であることが確認できる。

、

(3) 信号電荷の蓄積部のN領域が

外部金属コンタクトがない floating 領域であること。

(4) 信号電荷のN層の濃度が完全空乏化可能な濃度であること。

HAD sensor では、特許の実施例から見てとれる様に、

光電子を蓄積するN層の濃度は埋め込みチャネルCCDの

埋め込み層の濃度と同等の濃度としている。

蓄積部のN層と、埋め込みチャンネルCCDの埋め込みN層は、

同一層で、同一濃度としている。

埋め込みチャンネルCCDの埋め込みNと同様に

低い濃度のN層を蓄積部とするとしている。

完全空乏化可能となる低い濃度にすると言う意味になる。

(5) 以上のことから、 上記転送部(CTD)に移行させて、

その完全転送( complete charge transfer action)をを

行うようにしたことを特徴とする固体撮像装置

( solid state image sensor ) となる。

******************************

以上の考察から 1975年に萩原が発明した image sensor の

構造とすの重要動作 mode は、 pinned photo diodeを

定義する 動作 mode と 構造特徴を満たすことになる。

従って、1975年に萩原が発明した image sensorは、

pinned photo sensor そのものであると結論する。

*********************************************************

結論として、 現在 世界的に話題になっている

pinned photo diode と言われる半導体受光素子は

1975年にSONYの萩原が発明しSONYが申請した日本特許で

記述定義される半導体受光素子と、

構造面でも、その重要動作の特徴 modeにおいても

同一の半導体受光素子であると判断できる。

*********************************************************

従って、もとSONYの萩原良昭が

pinned photo diode の本当の発明者であり、

SONYはその pinned photo diode

は 1978年に frame transfer 方式の

CCD方式ですでに原理証明し、SONYでは、

萩原特許を武器に、HAD sensor ブランド名で

慎重にその製品の完成度と品質を保証するたまに

NECに試作発表では先を越されたが NEC以上に

IT 方式CCDでも 全日空ジャンボでの搭載など

世界で初めての商品化に成功している。

まだ、その受光部には 萩原考案のHAD sensorあ

構造は採用されていないが、当時、すべて同時に学会

活動しているが、 fram transfer 方式 CCD imager も

interline 方式 CCD imager 両方を 萩原が主体となり

設計開発したもので、その先には 1975年ni

萩原が構想し SONY original 特許の 萩原考案の

受光構造を interline 方式 CCDに採用するのは

時間の問題であった。

現在世の中で話題になっている pinned photo sensor は

萩原は観察します。

その特許の中にある empty potential well の曲線を

見たことのない技術者の誤解によるものであると信じます。

以下の内容は、上記の日本語記述の内容をもとに

より詳しく英文で記述したものです。

****************************************************

*****************************************

萩原良昭の出版図書の紹介

*****************************************

人工知能パートナー(AIPS)を支える

デジタル回路の世界

*****************************************

ISBN 978-4-88359-339-2 C3055

本体 9000円+税

B5サイズ 上製 475ページ (ハードカバー)

TEL: 042-765-6460(代) 青山社

*********************************************************

*********************************************************

.............SONY HAD sensor is the origin of our AIPS sensor................

*********************************************************

Please visit the following sites to learn about Sony HAD Sensor.

https://en.wikipedia.org/wiki/HAD_CCD

https://www.ptgrey.com/exview-had-ccd-ii-sensor-technology

https://en.wikipedia.org/wiki/Hole_accumulation_diode

https://www.sony.net/SonyInfo/News/Press_Archive/200002/00-007/

"HAD" technology for CTD (charge transfer device) sensor

that includes CCD,BBD,MOS and many kinds of other applications,

was invented by Yoshiaki Hagiwara at Sony in 1975.

Sony revealed a one-chip frame transfer CCD imager

with "HAD" technology in 1978 for the first time in the world.

Hagiwara's "HAD" technology , applied from original CCD

and back-illuminated CMOS image sensors, suppresses

fixed pattern noise that results from unwanted dark current

that occurs regardless of the amount of absorbed light.

By fabricating a hole-accumulation layer below the surface

of the image sensor, dark current can be suppressed at source.

By combining these two technologies, fixed pattern noise

can be substantially suppressed to improve signal-to-noise level

by 25 times and more.

In addition to improving image quality, image lag has also been

suppressed by optimizing pixel construction.

By adopting L-shaped gate for "HAD", electrons in the pixel

can be effectively transferred for lag-free image.

All of these achievements could not be possible without

Hagiwara's invention and his personal engineering efforts at Sony.

"HAD"means "Hole Accumulation Diode" officially,

but it also means "Hagiwara diode ",

honoring his invention in 1975.

"HAD" technology, invented in 1975 and developed

by Hagiwara at Sony is Sony's original creation.

Yoshiaki Hagiwara is the inventor of Sony HAD sensor.

Sony never paid any patent fees

to any other competing companies

for this "HAD" technology.

Confusingly, since HAD is a trade make of Sony,

the HAD technology has another name, that is,

the PPD ( pinned photo diode ) technoloy.

The name PPD is now more widely used,

specially in the technical world.

Confusingly, it is not well understood that

HAD and PPD are the same structure

originally invented by Hagiwara in 1975.

Yoshiaki Hagiwara is the inventor of pinned photo diode sensor.

*****************************************

萩原良昭の出版図書の紹介

*****************************************

人工知能パートナー(AIPS)を支える

デジタル回路の世界

*****************************************

ISBN 978-4-88359-339-2 C3055

本体 9000円+税

B5サイズ 上製 475ページ (ハードカバー)

TEL: 042-765-6460(代) 青山社

*********************************************************

********************************************************************

What is HAD/PPD? How does it work ?

********************************************************************

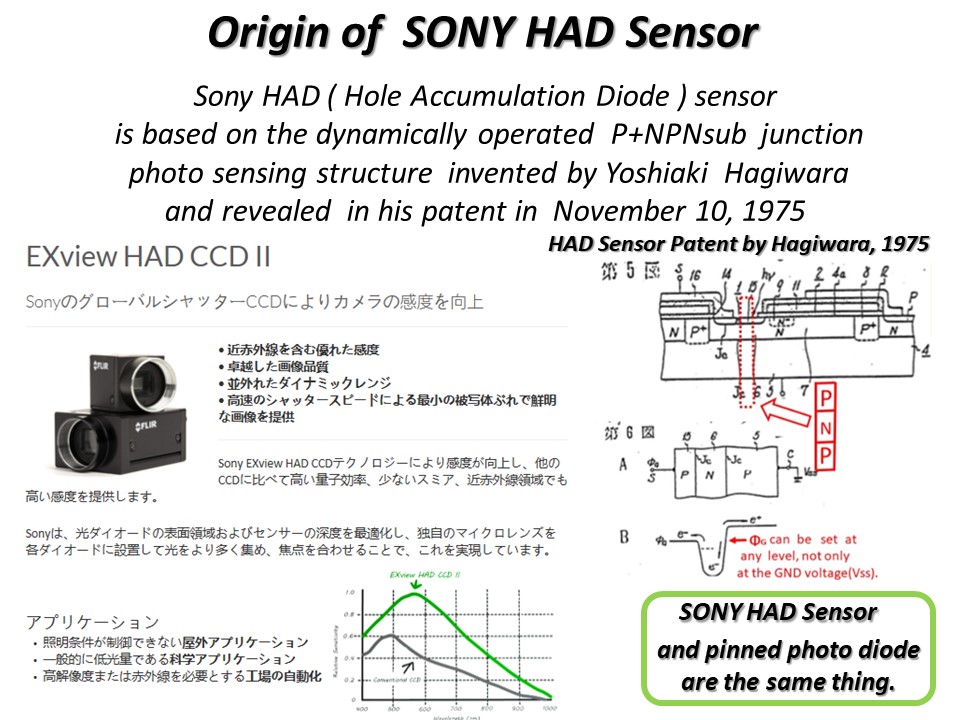

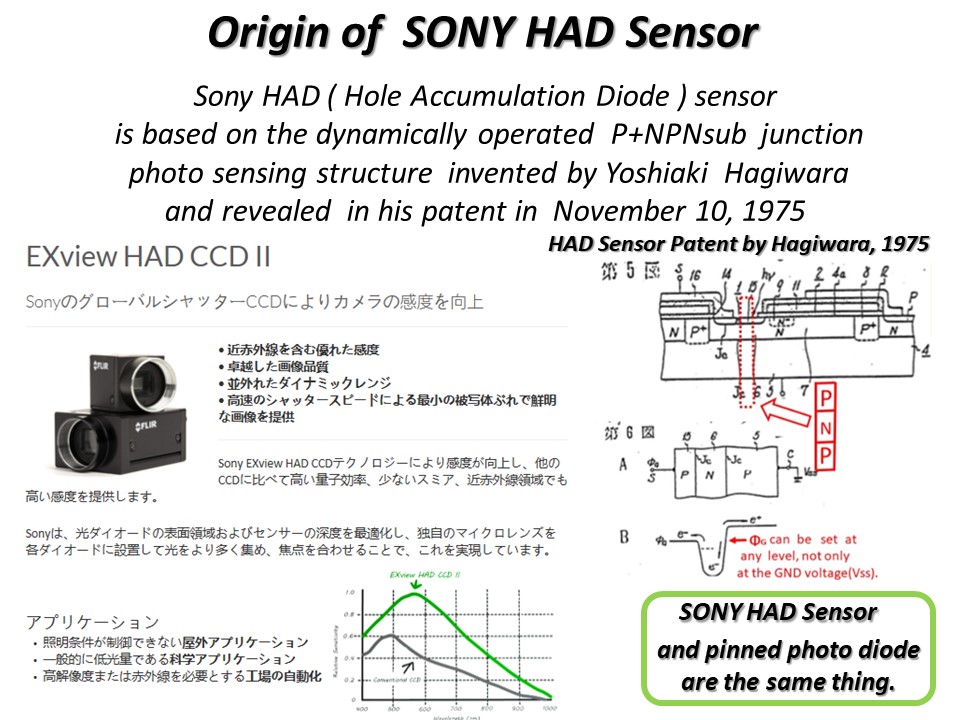

Sony HAD ( Hole Accumulation Diode ) sensor

is based on the dynamically operated P+NPNsub junction

photo sensing structure invented by Yoshiaki Hagiwara

and revealed in his patent in November 10, 1975

SONY HAD Sensor and

pinned photo diode are

the same thing.

Hagiwara invented in 1975

the pinned photo diode

widely used now.

Sony P+NPNsub (HAD) sensor

was also named later as

the pinned photo diode (PPD)

because the accumulated

majority carrier holes in the P+ layer

pins the P+ layer

voltage

at a fixed value by

some external voltage,

such as the substrate voltage

or any voltage from external metal wiring

by the metal contact on the P+ layer..

*********************************************************

***************************************************

Dear college students, professors and friends,

please read the following very interesting review paper.

***************************************************

***************************************************

" A Review of the Pinned Photodiode for CCD and CMOS Image Sensors"

by Eric R. Fossum and Donald B. Hondongwa , which was published in

IEEE JOURNAL OF THE ELECTRON DEVICES SOCIETY, VOL. 2, NO. 3, MAY 2014

*********************************************************

There are many false descriptions in this paper,

maybe simply because of lack of information ?

But it is a very good educational paper for college students

if the false descriptions are all corrected.

I belive poeple can say anything,

but the false comments shoud be corrected.

The truth shall make you free.

Yoshiaki Hagiwara in CalTech from 1967 to 1975.

***************************************************

" A Review of the Pinned Photodiode for CCD and CMOS Image Sensors"

by Eric R. Fossum and Donald B. Hondongwa , which was published in

IEEE JOURNAL OF THE ELECTRON DEVICES SOCIETY, VOL. 2, NO. 3, MAY 2014

*********************************************************

This paper does not describe about the potentile well

which was revealed by Yoshiaki Haiwara in Sony at age 26

in his Japansese patent in 1975.

Hagiwara drew an Empty Potential Well

in his patent in November 10, 1975 ,

which may be the evidence to prove the fact that

Hagiwara is the inventer of the pinned diode.

Dear college students, professors and friends,

please judge for yourself.

******************************************************************

Hagiwara at Sony in 1975 conceived the idea

of a photo sensitive dynamic device structure,

filed a Japanese patent in November 10, 1975 ,

explained in Japanese in the official patent claim paragraphs

and disclosed the PNP transistor structure on N substrate,

with the floating photo sensitive base N region ,

serving also as the the photo electons storage area,

with the empty potential well

waiting for the majority carrrier photo electrons,

with the built-in complete charge transfer operation mode

which results the final completely depleted empty potential well

in the N photo sensive floating base N region

of the dynamically operated PNP transistor on N substrate,

which is the origin of the pinned photo diode sensor.

Yoshiaki Hagiwara revealed ,

in his 1975 Japanese patent ,

this photo sensitive dynamic PNP transistor structure

with the floating photo sensitive N base region.

The structure for this unique operation mode

is now called as

the pinned diode as shown below.

.

.

Please compare the above picture with the figures below.

The Fig.5 and Fig.6 shown above

are included in Hagiwara's 1975 patent.

*************************************************************

The evidence of the fact is explained as below:

(1) In Fig.5 shown above is just one example of

the dynamic P+NPNsub structure described in Japanese

in Hagiwara 1975 Japanese patent claim,

Fig.5 shows a photo sensetive dynamic PNP transistor structure

with the floating N type base region

which serves as the majority carrier photo electrons storage area.

This observation alone may lead to the conclusion that

Yoshiaki Hagiwara in Sony at age 26 in 1975,

convieved for the first time in the world,

the photo sensetive dynamic PNP transistor structure

with the floating N type base region,

which is exactly the same structure

of the pinned photo diode,

now widely used in image sensors.

Dear college students , professors and friends,

please jude for yourself.

(2) Fig.5 also shows the CCD structure

with the lightly doped region

under the charge transfer gate.

This portion of the N-/N region

is intended to give a potential diectionality

for the photo electrons

to move in the right direction under the transfer gate.

The structure is made so that

the photo electrons can be transferred smoothly

to the left buried channel N layor storage area

under the same buried channel CCD gate.

Dear college students, professors and friends

please jude for yourself.

(3) Furthermore, Fig. 6B in his patent shows

an empty potential well,

which implies the potential well ,

being completely depleted

of the majory carrier photo electrons

in the floating N storage area in dynamic operation.

This may be considered as the evidence of

the complete-depletion-mode charge transfer operation

of the SiO2 exposed and dynamically operated base N region

of a photo-sensing P+NP transistor in the curent-cut off mode

with the floating N layer storage

for the majority carrier electrons.

CCD is important because of

its dynamic operation mode of

the empty potential well

which is the evidence of

the complete charge transfer of

CCD capacitor structure.

The pinned diode (P+NP structure) is important because of

its dynamic operation mode of

the empty potential well

which is the evidence of

the complete charge transfer of

the floating transistor base N of

the emiiter junction capacitor structure.

The P+NP structure on the N substrate with base N floating

was originally invented by Yoshiaki Hagiwa of Sony in 1975

So it may be concluded that

Yoshiaki Hagiwara is the inventor of the pinned diode.

Dear college students , professors and friends,

please judge for yourself.

***************************************************************************

*************************************************************************

The first Pinned PD , in the form of P+NP sensor element

on Nsub strruncture with the floating N layer for complete

charge transfer , was invented and filed in a Japanese patent

by Hagiwara at Sony in 1975, and was used in his FT CCD

imager in 1978 with P+NPsub sensor element, in which

both P+ and P are connected.

Later Teranish in NEC disclosed his ILT CCD PD's .

Soon after, Sony introduced on the market,

the HAD sensor video camera

with the P+NPNsub image sensing structure.

HAD is Hole Acumulation Diode in brief,

which was first revealed in the form of

the emitter junction (diode) of

a photo sensitive dynamic PNP transistor structure

invented by Haiwara in the 1975 patent.

Sony now enjoying the big sensor business with the back

illuminated CMOS imager with the HAD sensing element

which was Hagiwara's invention.

Confusingly enough, HAD sensor and the pinned PD,

Teranish's ITL CCD PD's, and

Haiwara's P+NP transistor structure on the Nsub

are all the same thing.

The VOD punch thru mode operation

of the P+NPNsub structure

was well understood in 1975 in public.

However , the well known P+NPNsub structurre,

this time with the floating base N region

in the complete depletion mode built-in,

resulting in the complete charge transfer of

the majority carrier photo electrons

from the floating base N region

was revealed by Hagiwara, in his 1975 patent.

The pinned diode and the HAD sensor are

the same thing which is a P+NPNsub structure

with the floating N base region.

So who is the true inventor of the pinned diode ?

Dear college students , professors and friends,

please judge for yourself.

And what is the truth ?

**********************************************************

I belive poeple can say anything,

but the false comments shoud be corrected.

The truth shall make you free.

Yoshiaki Hagiwara from 1967 to 1975 in CalTech.

***********************************

*

**************************************************

Hagiwara of Sony invented the pinned diode sensor in 1975

**************************************************

テレビがアナログからデジタルハイビジョンテレビになり、

高画質で高精彩な画像を家庭に提供しています。

さらに、家庭のデジタルテレビはますます賢くなります。

家庭用の小型ゲーム機感覚で、たとえば、

任天堂のDSやSONYのPlayStationの感覚で、

家庭ごとに、人工知能搭載のコンピュータが、

もうすぐ、近い将来、登場することでしょう。

それを萩原は AIPS BOX と呼びました。

萩原は、2008年にSONYを60歳で退社したのと同時に、

神奈川県に、 NPO法人

「特定非営利活動法人AIPSコンソーシアム」

を設立しました。 その活動目標は、家庭で使う、人工知能搭載の、

高速並列処理コンピュータと、それに従って、 real timeで、

敏速に動く、ロボットの実現のための技術開発に貢献することです。

老人を集め、ほそぼそと活動して来ましたが、

もう活動仲間が、私を含め70歳~80歳となり、

いつポックリ行くかもしれませんので、

「葬式」だけは生きている間に、

後始末で若者にも迷惑にならない為にもと考え、

10周記念を最後に、このNPO法人を

閉鎖することにしました。

しかし、みんな元気なうちは続けようと、

個人グループ同好会の形で、楽しく活動を続けています。

この人工知能搭載の家庭用 AIPS BOXと、それで動く

ロボットの目(電子の目)には、 固体撮像素子、すなわち、

Image Sensor なる半導体部品が不可欠です。人間の

目よりも感度がいい、「賢い電子の目」です。

それを実現すべく、萩原はSONYに1975年2月に米国の

大学、 CalTechを 卒業して、入社しました。

入社後、数か月で出願した特許があります。

図1 (萩原特許1975の実施図)

**************************************************

まず、当時は特許はあまり今ほど注目されるものでは

ありいませんでした。この2つの図は1975年の時代では

特許請求した内容以外にも、新規的なほかのデバイス構造

要素が見てとれます。今なら各社確実に特許にする内容です。

(1) センサー部のTOPのP層に金属コンタクトがある。

実際はこれは実施例の1つで、特許の請求文には含まれません。

金属コンタクトの構造の内容はまったく請求文には触れておらず、

したがって、金属コンタクトはなくてもいいことになります。

ただこのP領域が floating になってはこまります。

この特許は その下の N層が floating 動作されることを意図しています。

当初、センサーに金属コンタクトがあり、この構造で

センサーを造るのは難しいのではと思い、素子分離

のP+の拡散とつないでプロセスを簡素化して

Interline 方式ではなく、FT方式で、SONYでは

最初に試作し、新聞発表しました。

別にPNP構造で PNP transistor にたとえて、

emitter 側のPを、collector側のPにつないでも

十分、 受光素子として使えることを確認しましした。

当然、この構造なら Interline 方式でも試作可能です。

この萩原特許を知っている技術者なら、すぐこの構造を

Inerline 方式でも使えること確信できます。

このHADセンサー搭載の IT方式のCCD imager も、、

このFT型のCCD imagerの受光部分と同じ、PNP構造で 、

HADセンサーの名前は後でつけたものです。

IT方式のCCD imager でも、HADセンサーの、

PNP transistor の emitter 側に対応する P層を、

collector側のP層に直接つないでいます。

t

しかし、最終裏面構造のHADセンサーにしますと、裏面から光を

受けるので、この金属コンタクトを、 製造に採用されるかは別ですが、

つけることは可能です。でも 1978年発表の FT CCD の時と同様に

やはり金属コンタクトは取ったほうがいいか。。。

1975年の萩原特許では金属特許をつけることは特許請求範囲では

まったく言及していませんでした。

特許請求範囲と特許の本文はわかりにく日本語になっているので、

実施図を見るだけで、本文の正確な文章を読まず、

「萩原さんの特許の実施例ではセンサー部に金属コンタクトがある。

こんなもの造れるかよ。やはり、まだ入社そこそこの新米技術者で

実践経験が少ないので無理ないけどね。」と同僚や先輩に

言われたことが何度もありました(涙)。

本当は P+NPNsub サイリスタ―構造を 有効に活用して、

Nsub に流す方法もあるのは知っていたけど、これも Bipolar

技術で punch thru の怖さを 実感していたので正直あまり

関心を持てませんでした。

CCDが本格量産に入り、私は その後、DRAM,SRAMを

Sony内での事業化に挑戦しましたが、DRAMは試作開発に

とどまり、社外発表はできませんでしたが、 ISSCCの学会で、

世界発の 8 M bit の DRAMを 設計担当の 宮司さんが

考案のアイデアでしたが、この CMOS imager でも 使える

bit line 信号線を読み出し時に floatingにすることにより、

高速にデジタル情報ですが高速増幅できる原理を使って

他社にさきがけて発表できました。この宣伝効果は大きく、

intel社からも cache memory 用のSRAMの受注を受け、

多くの日本の会社がDRAMの生産でおおもうけしている中、

SONYでもうけていました。

その後、ソニーのマイコン事業の設計の仕事を手伝いました。

ソニーは 8 bit と 16 bit マイコンを生産していました。

日立のH8マイコンの性能が良く、ソニー内のユーザ^も、

日立のマイコンなどを採用することになり、商売は先細りに

なりました。

その頃、SONYが ゲーム機 PS1 の事業を始めました。

へえ、誰が? すごい、 という感じで友達に聞くと、

久夛良木さんだよ、とのことでした(拍手)。

彼は1975年の入社同期でした。入社時の配属は違いましたが、

私が入社時からお世話になっていた吉田室長の情報処理研究室に

私が CCDの開発生産のため移動して出た後、すぐ情報処理研究室

に配属になりました。同じソニー厚木テックの中にあり、時々古巣の

情報処理研究室に遊びに行っていましたが、そこで 彼がやっていた

joystick などを使って テレビに映った顔を自由に real time で

動かすデモを見せてもらったことがあります。

コンピュータを使って 映像を自由に操作し楽しめるものを造りたい

との夢を話していました。私はその半導体チップ側の人間で、ビデオ

カメラやデジタル処理用のプロセッサーやメモリーチップの開発者

でしたが、映像を使って、カメラを使って、デジタル回路を使って、

人間にやさしいコンピュータ支援システム AIPSと今は呼びますが

久夛良木さんの話を聞いて、俺も頑張らなきゃと感じました。

2000年に初孫が生まれ、私も50歳を過ぎたころには、

もう現役で仕事は難しく、技術管理系や技術研修係の

仕事を担当しながら、半導体技術企画室長などの立場で、

2000年に入り、2008年定年まで、 東芝の斎藤さん、

日本IBMの西原さん立ちと私は久夛良木さんの半導体

関係をサポートする仕事を最後にSONYを定年退職しました。

私が現役技術者として image sensor を 担当したのは、

まだ中研時代の吉田さんが率いる情報処理研究室のメンバーで

ほんの数人で CCD imager の設計・評価測定部隊でした。

1980年代になり、厚木テックで本格的な量産実験の時期となり、

1990年になるとソニー国分工場で生産が本格化するまでは、

SRAM事業やマイコン事業を担当していた私でしたが、

たいへん気になり、もとのCCDの職場の仲良し仲間から

話を聞き、いろいろアドバイスをできる範囲でしたがしていました。

考案してから40年が過ぎることになります。

この構造でも表面のP+ 接合領域は重要な役目をはたしています。

上部酸化膜と半導体基板の接触界面の原子レベルの結晶体の

乱れによる dark 電流を低減できます。

話がそれました。

ごめんなさい、もとの話にもどします。

1975年の特許出願の話でしたよね?

この2つの図は、1975年の時代では

特許請求範囲に入っていないが、新規的なデバイス構造要素が、

今なら、各社確実に特許にする内容があります。

(1) センサー部のTOPのP層に金属コンタクトがある。

実際はこれは実施例の1つの特許の請求文には

金属コンタクトの構造の内容はまったく触れておらず、

特許請求していません。