**********************

The AIPS ( Artificial Intelligent Partner System ) Home Page 005

**********************

●海外版の日本国特許検索サイトでは、

https://www4.j-platpat.inpit.go.jp/eng/tokujitsu/tkbs_en/TKBS_EN_GM101_Top.action

Japanese Patent Number の欄に Document Number を 入力してください。

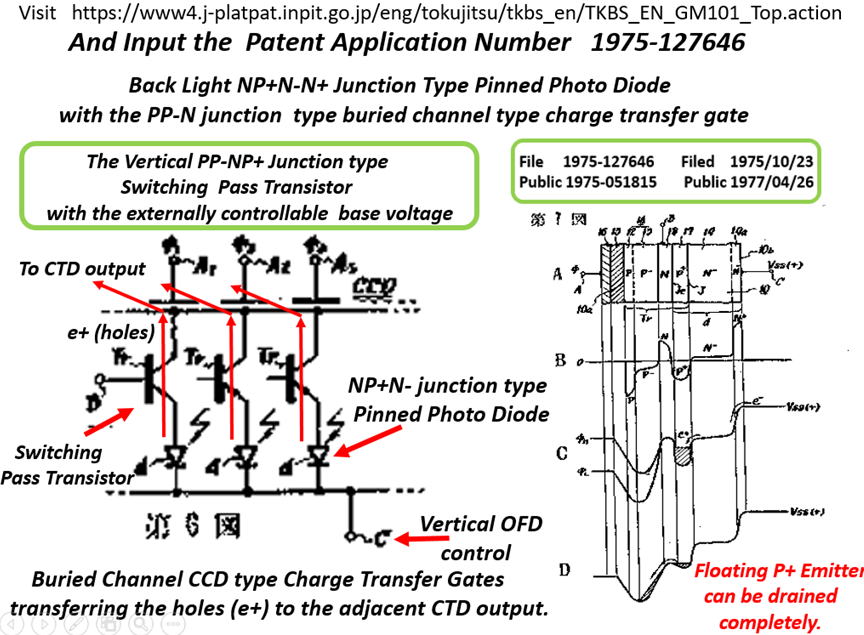

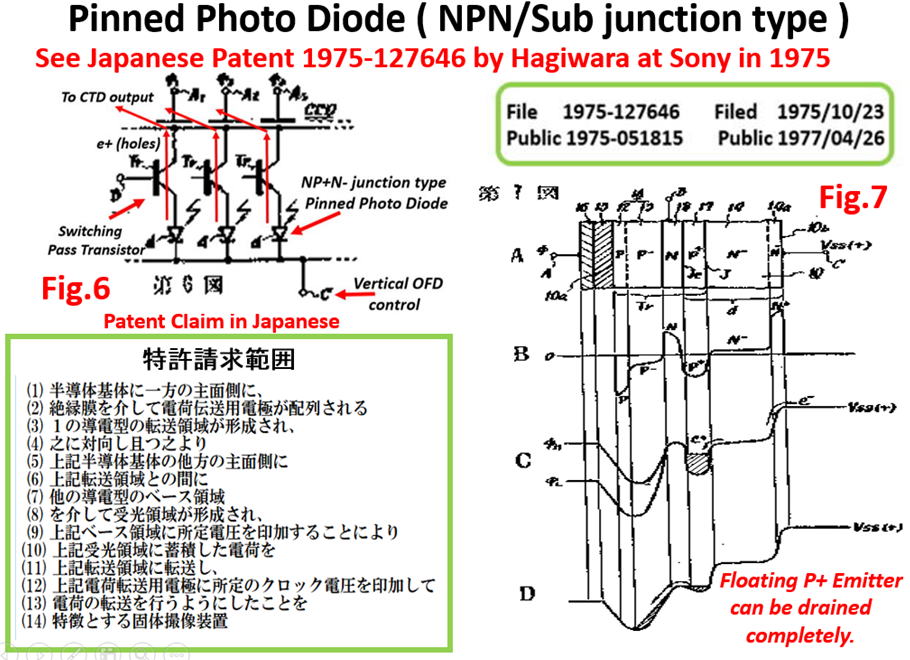

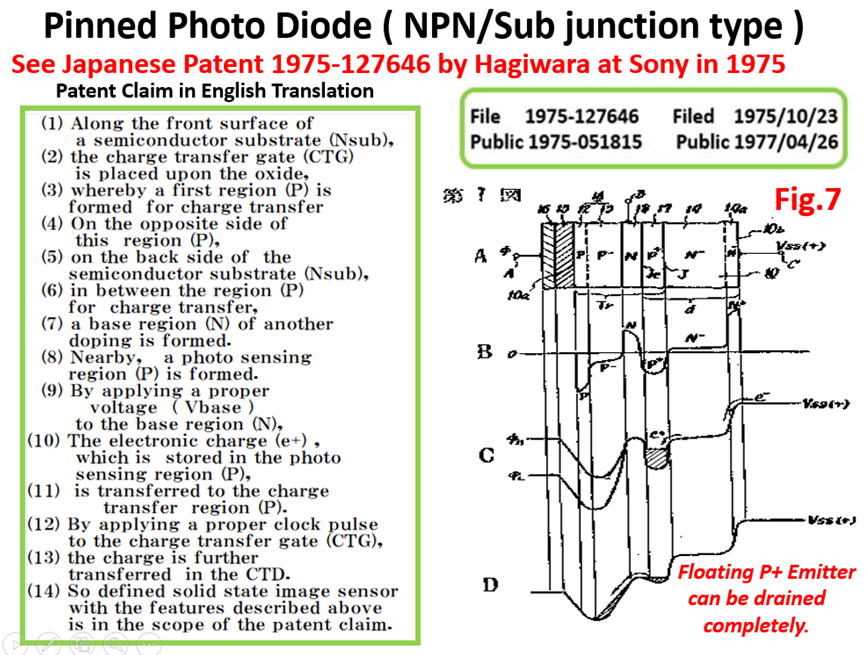

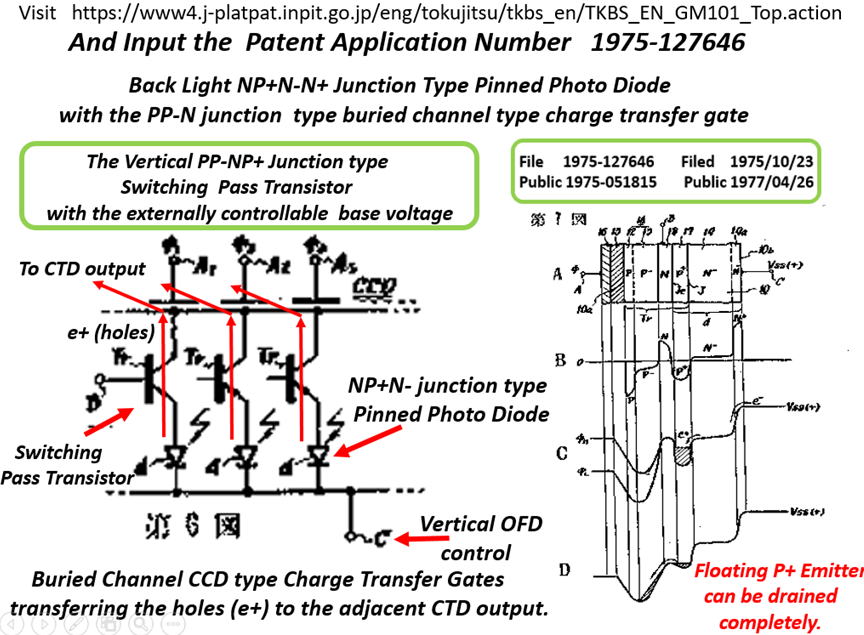

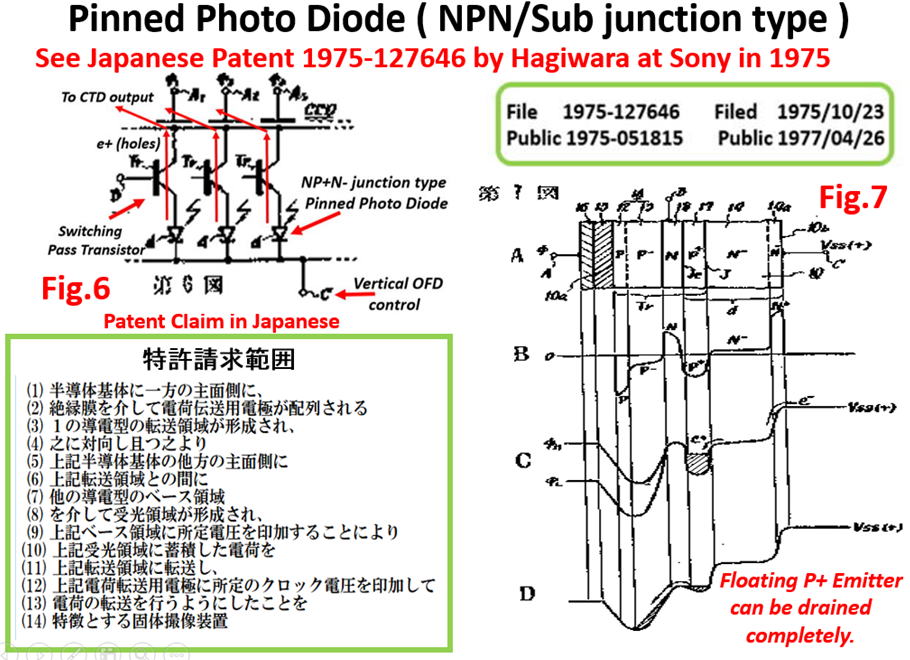

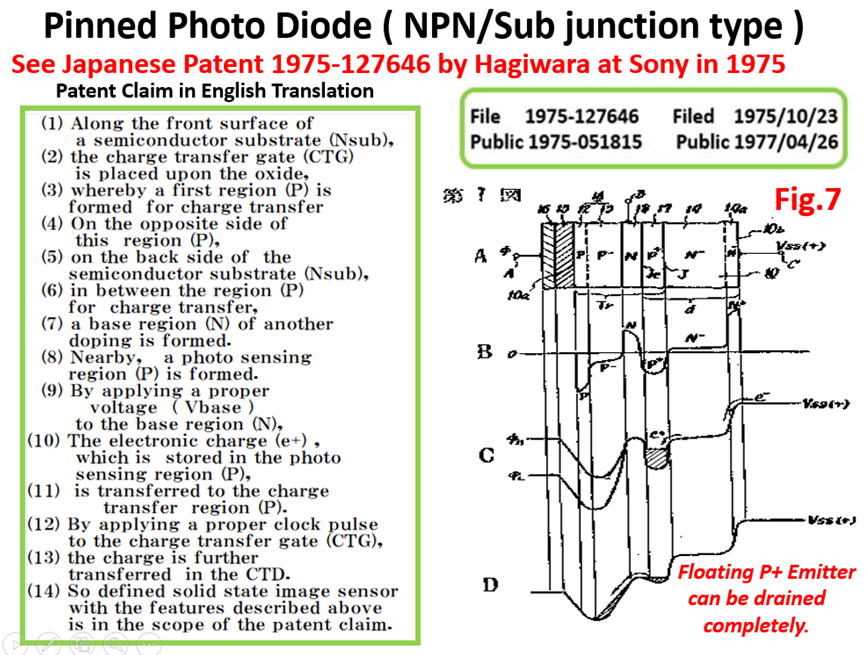

(3) つぎに、1975-127646 と入力しますと、

萩原がSONY時代に申請した、1975年日本国特許の、

裏面照射型にも応用可能で、表の電荷転送部との間に

制御用Switch Tr がついた、PP-NPNN+ 接合(thyristor)型の

Pinned Photo Diodeの発明特許の詳細が閲覧できます。

この特許は世界ではじめて Bipolar Transistor (PP-NP接合)

のCollector 領域(P) を浮遊状態( floating base )の光信号電荷

の蓄積部とした、まったく新規なBipolar Transistor (PP-NP接合)

の dynamic 動作を提案したものです。従来のBipolar Transistor

(PP-NP接合)の信号電流増幅動作以外にも、光感知素子として

需要な応用例があることを提案した、全く新規な光感知構造を

持つ固体撮像装置に関する基本構造特許となります。

この特許の詳細説明は以下の資料を参照してください。

Pinned Photo Diode was invented by Hagiwara of Sony in 1975 (PDF)

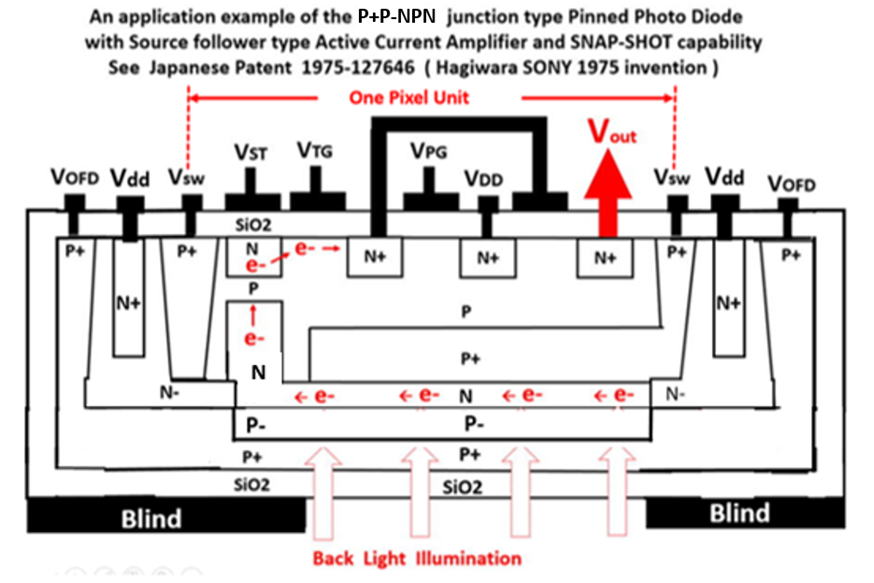

この構造は 電荷転送装置(CTD)としてCMOS Imager を

採用した場合でも、Snap-shot 方式で撮像動作可能です。

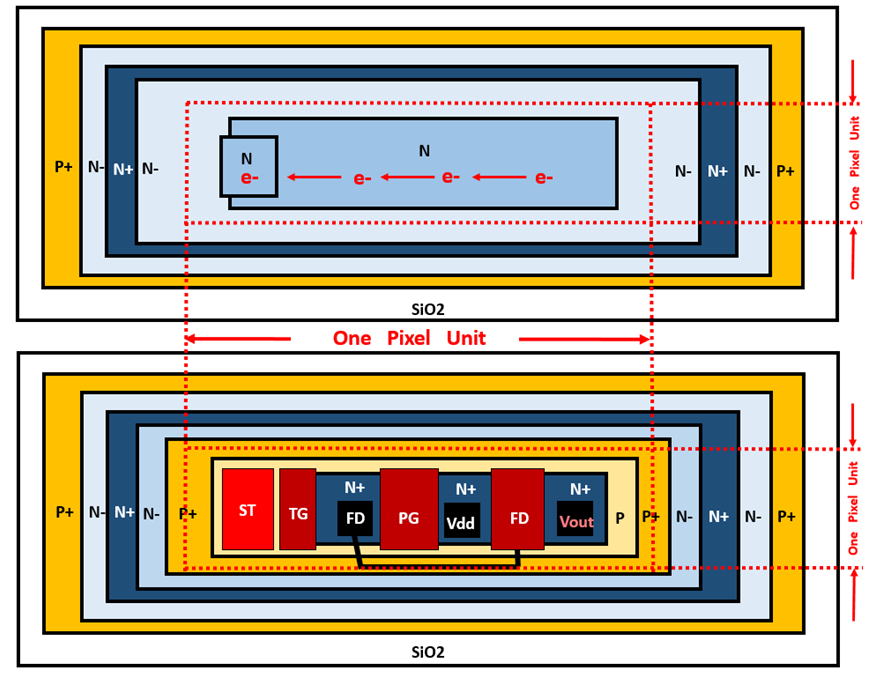

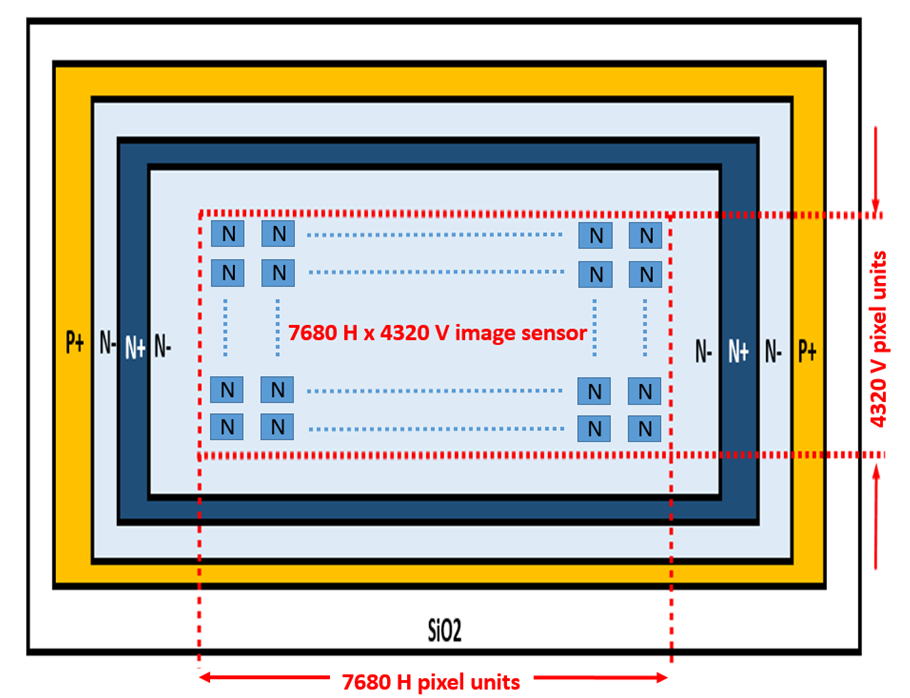

(1) これは、裏面照射型の、 N+N-P 型のPinned Photo Diode です

そのN+端子が外部制御可能なVOD(vertical overflow drain)として機能します。

(2)P+NP 型の Pass Switching Bipolar Transistorとして機能します。

このPass Switching Bipolar Transistorの emitter 側の端子を P+と

表記していますが、あくまで便宜上の表記です。このP+領域は受光部

であり、光信号電荷(hole)の蓄積領域P+を意味します。その濃度は

相対的に薄く設定が 可能で、浮遊 emitter端子 として動作します。

(3)信号電荷(hole)は表側のP型の埋め込み型CCDの転送電極に

一時的に蓄積が可能です。従って、Snap-shot方式で動作可能です。

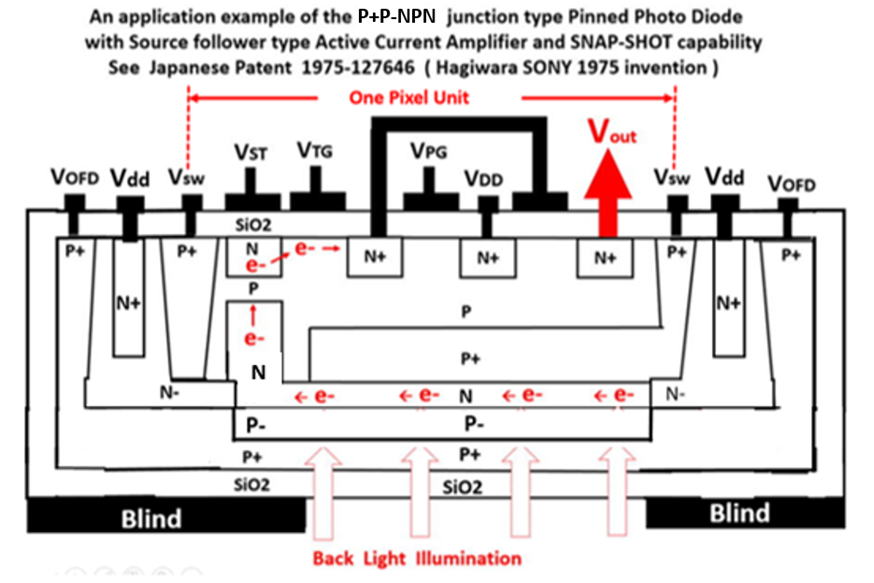

CMOS Image Sensor に Snap-shot 機能 を持たせるには、従来、

一時記憶用の Buffer Memoryが各絵素ごとに必要でしたが、その

機能を、表側の埋め込みチャネル型電荷転送電極容量で実現して

います。

(4)後は、電荷転送装置として、FT 型のCCD Imager 転送方式でも、

IT型のCCD Imager 転送方式にしようが、CMOS Imager 方式で

転送しようが自由です。最大のメリットは、Active Source Follower

Amp 回路を各絵素に装備したCMOS Imager 方式にも適用できる

構造です。これこそ、人工知能の電子の目の網膜構造の究極の姿

かも知れないと、そう当時、27歳だった萩原は、そのような夢を見て

いました(笑顔)。今のSONYの半導体技術では実現可能ですね!

この 特許の中で提示した実施例では CCD Image sensor としていました。

しかし、特許はあくまで受光部構造に関する特許であり、転送部はどの

方式を採用しようが自由です。今なら、CMOS Image Sensor方式にも

採用可能です。下の図はその場合の実施例の1つを提案したものです。

現在の半導体技術では実現可能でしょう(笑顔)

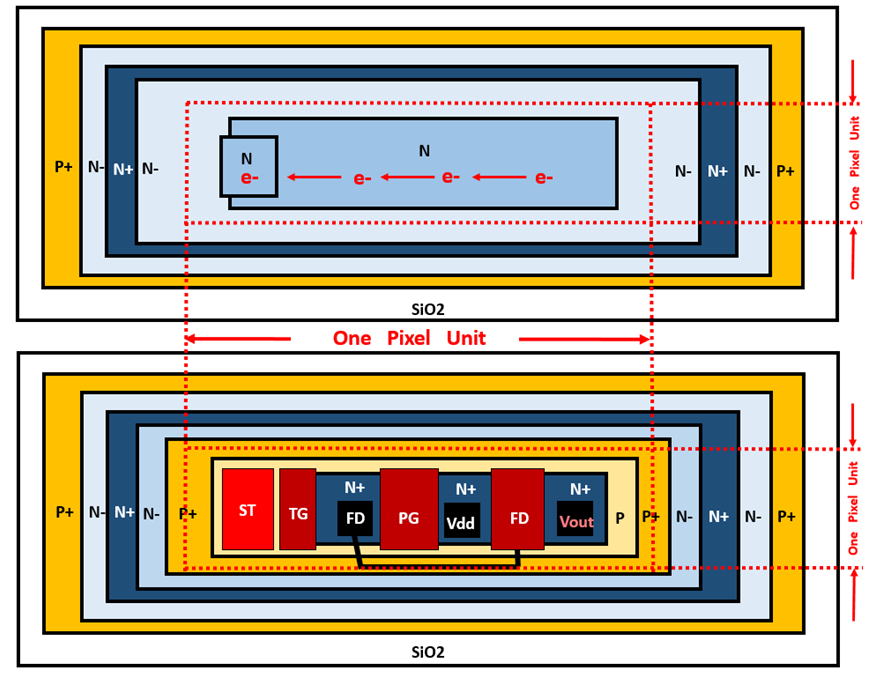

今の半導体微細化技術では、1つの画素面積( One Pixel Unit)

の中に、1975年代でCCD 出力部で既に採用されていた、Source

Follower 型の 従来の電流増幅出力回路がそのまま入ります。

もともとこの特許はそういうものも入ればいいなあと思いながら

申請した特許でしたが、まさか本当に入るとは当時の27歳だった

萩原は自分が生きている間に実現するとは思っていませんでした。

この裏面照射型の CMOS Image Sensor が実現可能となりました。

下の図の例では Snap Shot 機能を持たせる為に CCD 構造の

電荷一時蓄積電極(VST)を採用してみました。このVST電極

から電荷転送用電極(VTG)に電荷が転送されるところのみ、

CCD転送方式を採用した実施例になります。電荷一時蓄積

電極(VST)下のN領域は便宜上、相対濃度としてNと表記されて

いますが、比較的薄い濃度、すなわち、埋め込み型のBCCDの、

埋め込みチャネルの濃度としています。従って、完全空乏化

が可能です。周辺の「お城の堀」のN+ 領域は、もっともっと濃度の

濃いN+領域です。ここでは、Junction FET の原理を使っています。

受光部のN層と、その周りのN-層は、完全空亡化されいています。

この大きな Silicon Chip 1枚全体が、大きな Dynamic Junction

FET 型の Image Sensor 構造でもあります

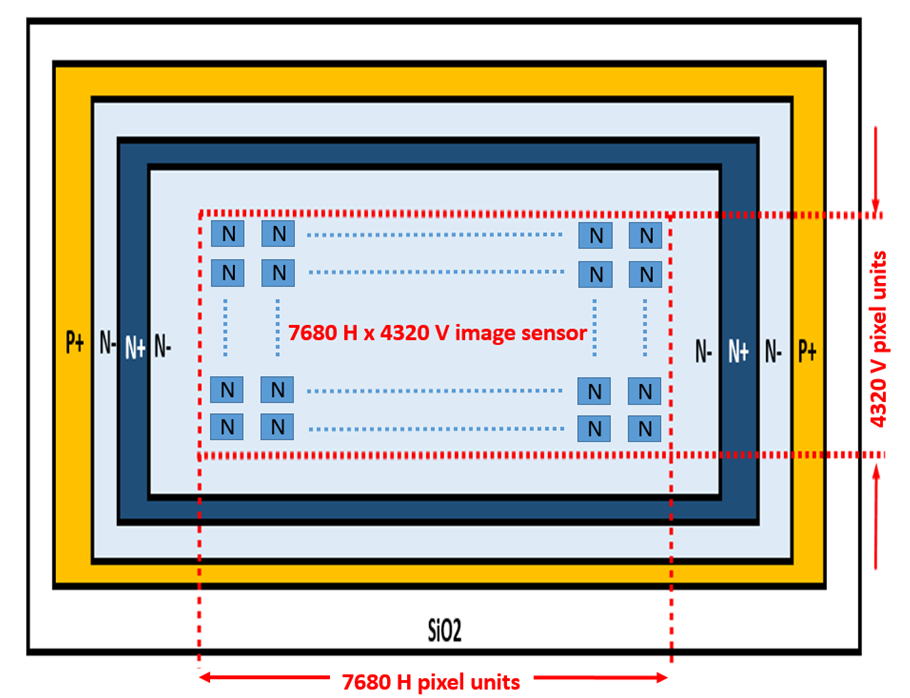

上図では、単純にひとつの絵素単位(one pixel unit )しか描いていませんが、

水平方向に 7680H 画素で、垂直方向に 4320V 画素 を 行列形式に 並べて

高解像度の image sensor 構造とします。

昔は NTSC方式のアナログテレビの時代でした。画素数も少なく、

35 万画素=(720H x 480V = 345600 pixels)で、水平解像度

の目安すとなる水平画素数も 720H~ 0.7 K画素程度でした。

当時、CCDは埋め込みチャネル方式を採用すると 99.999%もの

転送効率が期待できました。

すなわち、最大でも、0.001 x ( 720 + 480 ) = 1.2 % の電荷の

転送残りしかありません。絵素情報の混入(混色)問題は実用範囲

であるとのカメラシステム開発技術者からもサポートが得られた

時代でした。

この特許の詳細説明は以下の資料を参照してください。

Pinned Photo Diode was invented by Hagiwara of Sony in 1975 (PDF)

**********************

これは70歳じじいのぶつぶつぼやきの独り言でした。

**********************

**********************

The AIPS image sensor watching at its inventor, Yoshiaki Hagiwara.

return to TOP Page

**********************