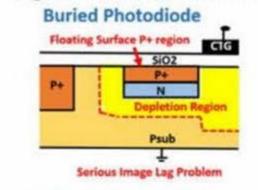

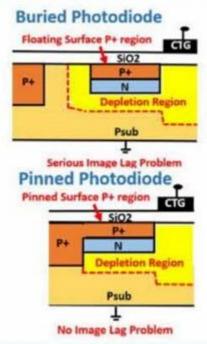

# Difference of Buried Photodiode and Pinned Photodiode

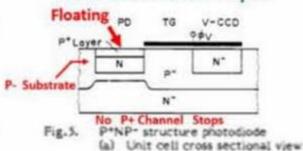

### Figure 5 does not have the P+ channel stop nearby.

#### NEC IEDM1982 Paper

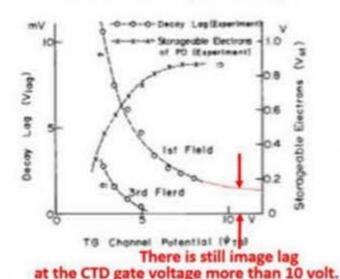

Fig.6. Storageable electrons vs. transfer gate channel potential, and decay lag vs. transfer gate channel potential in the P\*NP\* structure photodiode

# NEC IEDM1982 Paper reported Image Lag

Figure 6 shows that there is still image lag at the CTG gate voltage of > 10 volt.

### A long P+ Surface Stripe also has a serious RC delay.

#### Pinned Photodiode Must Have the Grounded P+ Channel Stops Nearby.

The resistivity  $\rho$  of the P+ hole accumulation layer is given by  $\rho = R *W *d/L$

In the 2/3 inch optical lens system, we have the optical image size of 8.8 mm (H) x 6.6 mm (V) which was a common size in 1980s. Hence, we then have L = 6.6 mm = 6600  $\mu$ m

The short wave blue light cannot penetrate more than  $d = 0.2 \mu m$  into the silicon crystal in depth. Hagiwara reported in SSDM1978 paper Qd =  $2 \times 10^{13} cm$ , which gives Nd = Qd/d =  $1 \times 10^{18} cm$ .

For Nd =  $1 \times 10^{18}$  cm<sup>-3</sup> we have  $\rho = 0.04$  ohm cm = 400 ohm  $\mu$ m

RC = {Lp / (W\*d) } {EW\*L/Xo} = EpL2/(d Xo)

We have  $\varepsilon = 216$  e/volt  $\mu$ m for silicon oxide and  $e = 1.6 \times 10^{-19}$  Coulomb

$RC = (216) (1.6 \times 10^{-19}) (400)(6600)(6600) / (0.2)/(0.1)$  sec

RC = 30.1  $\mu$ sec while one frame is 1/60 sec = 16.7 msec and the Vertical CCD register clock period is 16.7/500 = 33.4  $\mu$ sec

Hence RC delay time may not be ignored and surface P+ may be floating?