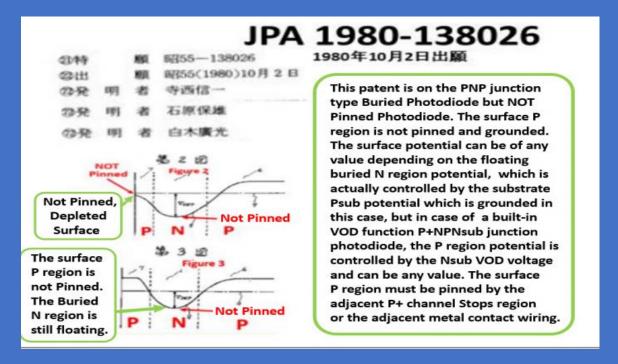

## NEC\_Teranishi\_Patent\_JPA1980-138026\_is\_NOT\_Pinned\_Photodiode.

NEC\_Teranishi\_Patent claimed that if the buried N charge storage region is completely depleted of the signal charge, there is no image lag problem. NEC\_Teranishi\_Patent claimed that both Figure 2 and 3 are possible in the NEC PNP double junction Buried Photodiode. If the surface P region was pinned, the case shown in Figure 2 would be impossible to be included in the NEC Teranishi Patent JPA1980-138026.

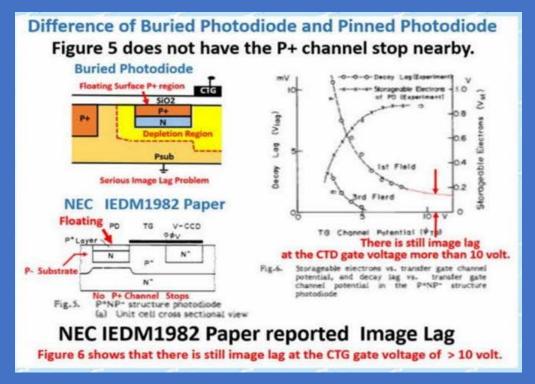

Apparently. the surface P region of the NEC PNP double junction Buried Photodiode is NOT pinned. The NEC Teranishi PNP double junction Buried Photodiode is NOT Pinned Photodiode. Surface potential Vs can be floating. This is the reason why Teranishi reported the serious image lag problem in the NEC IEDM1982 conference paper.