# Story of Pinned Buried Photodiode Yoshiaki Hagiwara

■What is the difference between CCD Image Sensor and CMOS Image Sensor?

What is CCD Image Sensor? Who invented it? Who developed it? What is CMOS Image Sensor? Who invented it? Who developed it?

What is the difference between Buried Photodiode and Pinned Photodiode?

What is Buried Photodiode? Who invented it? Who developed it? What is Pinned Photodiode? Who invented it? Who developed it?

In the historical invention and development efforts of image sensors, what is the true contribution of Charge Coupled Device (CCD)?

# Story of Pinned Buried Photodiode Yoshiaki Hagiwara

●CCD Image Sensor と CMOS Image Sensor の違いは何か?

CCD Image Sensorとは何か? だれが発明し、だれが開発したか? CMOS Image Sensorとは何か? だれが発明し、だれが開発したか?

●Buried PhotodiodeとPinned Photodiodeの違いは何か?

Buried Photodiodeとは何か? だれが発明し、だれが開発したか? Pinned Photodiodeとは何か?だれが発明し、だれが開発したか?

●Image Sensor の発明と開発史における電荷結合素子、すなわち、 Charge Coupled Device (CCD) の貢献は何だったのか?

## Story of Pinned Buried Photodiode Yoshiaki Hagiwara

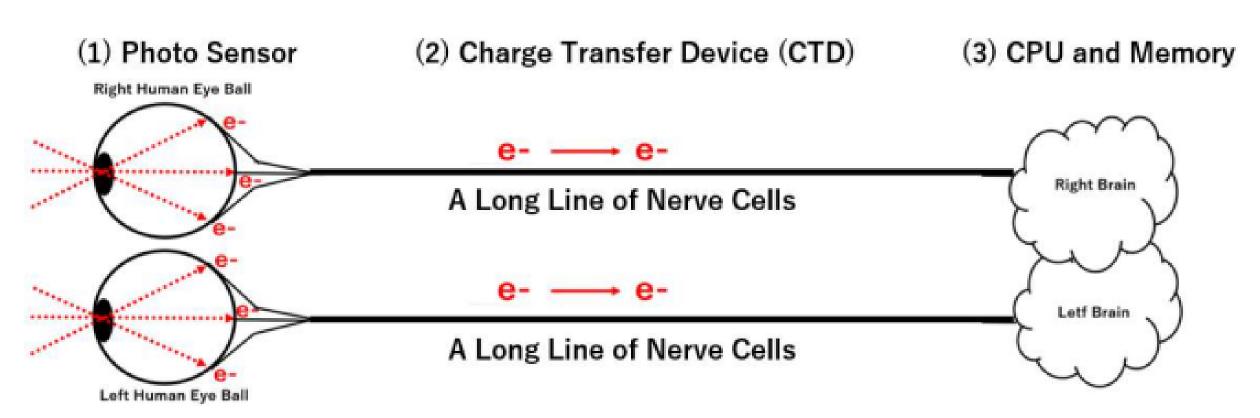

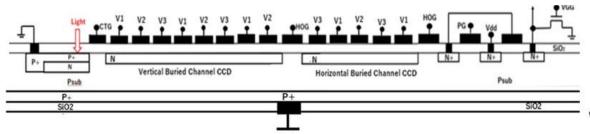

Figure 1. Artificial Intelligent (AI) Image Sensor Structure with Three Basic Parts.

# Story of Pinned Buried Photodiode Yoshiaki Hagiwara

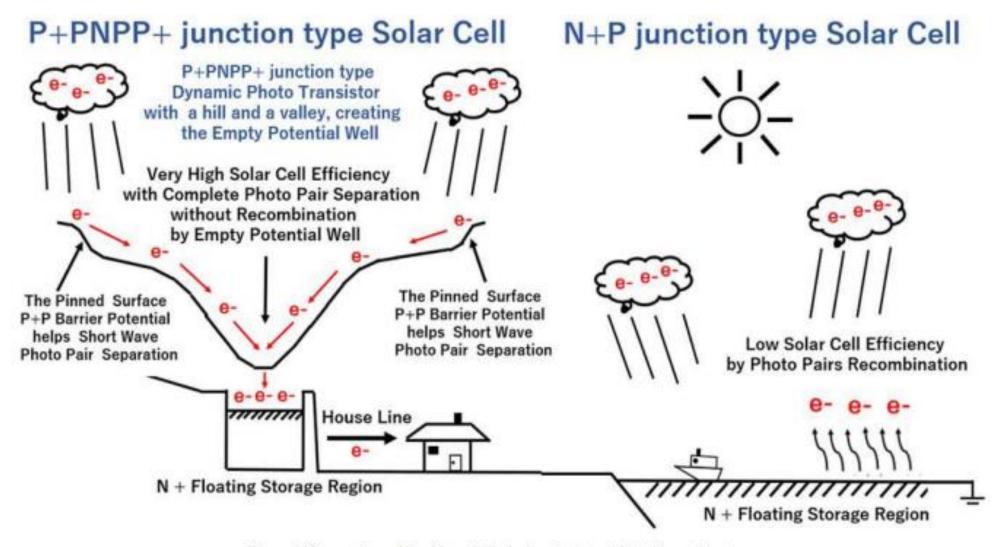

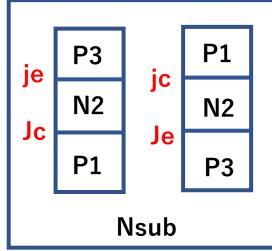

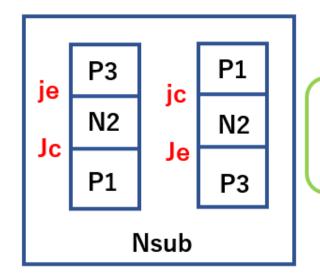

Figure 2. Comparison of Double and Triple Junction type Photo Sensor Structures.

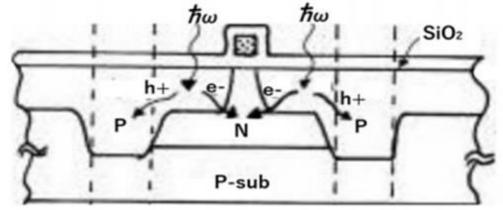

Before the invention of Charge Coupled Device(CCD) in 1970, the most of image sensors had the N+P single-junction type light-detecting picture-element (pixel).

The N+P single junction type photo sensor is still now widely used in solar cells with a poor light-energy to electron-energy conversion efficiency of about less than 20%.

Before 1970, it was well known that an MOS dynamic photo capacitor could also be used as a light-detecting picture-element (pixel). However, the surface metal of the MOS electrode does not pass the illuminated light thru. But buried channel type Charge Coupled Device (CCD) was very attractive because it can transfer the analog photo charge packet with a charge transfer efficiency up to 99.999%. In the analog TV era, the picture resolution was 800H by 500V, and the 99.999% charge transfer efficiency was enough since the number of the charge transfer required in the image sensor was only 800H + 500V = 1300times of the CCD charge transfers and the charge loss was only 1300 x 0.001 % = 1.3 %. Since human eyes do not recognize any picture noise and distortion of less than 3% and the camera sensitivity is defined as the signal to noise ratio (S/N), the over-all CCD charge transfer noise of about 1.3 % was very small. And CCD had a very important contribution for realizing a very high light-sensitive solid-state video camera in the analog TV era.

- However, for the digital TV era of 6000H by 4000V picture resolution, the 99.999% CCD charge transfer efficiency is no longer enough since the maximum number of the charge transfer required becomes 10000 and the charge loss is now over 10000 x 0.001 % = 10 %. Human eyes can recognize picture noise and distortion over 3%.

- ●Now, with the low-power digital CMOS circuit and with the correlated double sampling (CDS) scheme, and also with the in-pixel source-follower current-amplifier circuit and with the in-pixel or in-column A/D converter circuit, the digital CMOS type charge transfer device completely took over the role of the analog CCD type charge transfer device.

- ■But as well known, the low-power digital CMOS circuits and the A/D converters in the modern CMOS image sensors have nothing to do with the light detecting element.

- Then, what is the actual semiconductor device that has the super-light sensitive feature? The semiconductor device that has the super-light sensitive feature was actually used since 1987 when Sony successfully developed and produced the passport-size portable 8 mm video camera with the electrical shutter function capability for the first time in the world. The 1987 is the year when the film cameras began to be replaced completely by the very highly light-sensitive, all-solid-state and also mechanical-parts-free video cameras.

●Then, what is the actual semiconductor device that has the super-light sensitive feature?

The semiconductor device that has the super-light sensitive feature was actually developed in 1978 for the first time in the world by Sony and Sony also developed successfully for the first time in the word one-chip CCD video camera in 1980 using the same unique device with a very high super-light-sensitive feature.

However, Sony did not disclose the details of this unique photo sensor structure with the very high super-light-sensitive feature because Sony was under competitions with many strong rival companies. Sony was afraid of the possibility that they would easily copy the unique device and would also invent a better device against Sony.

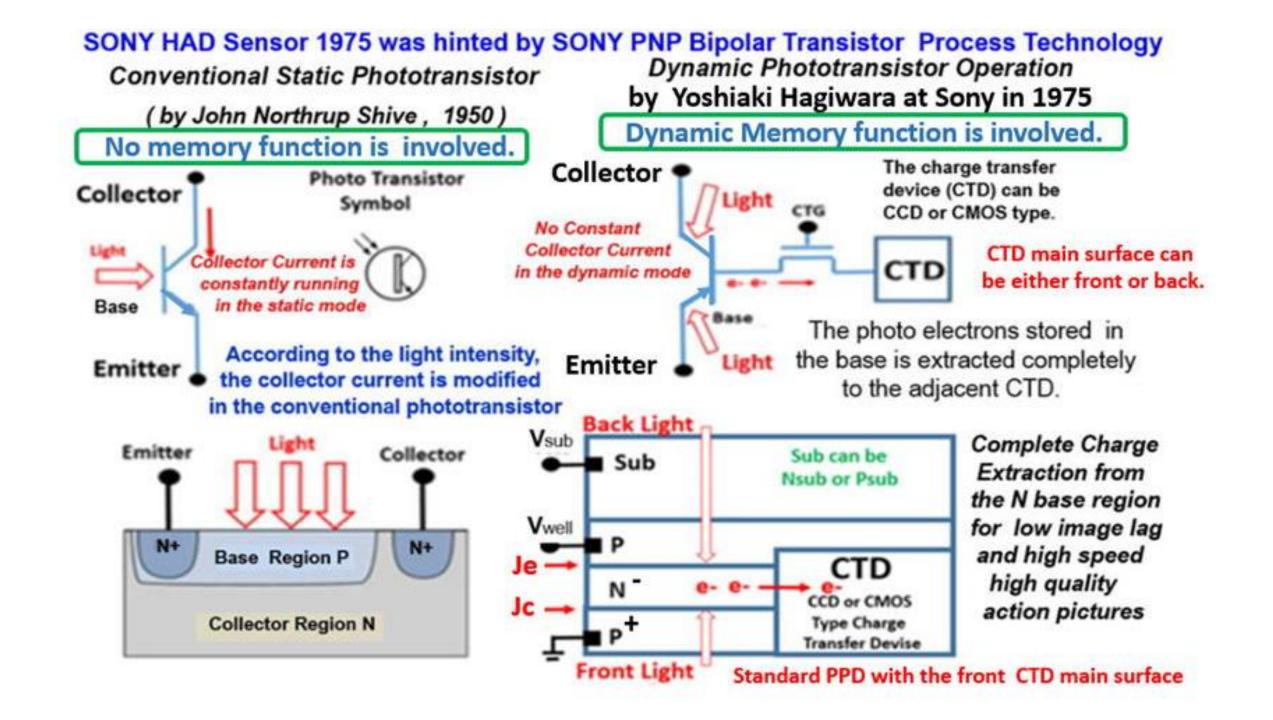

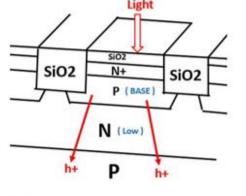

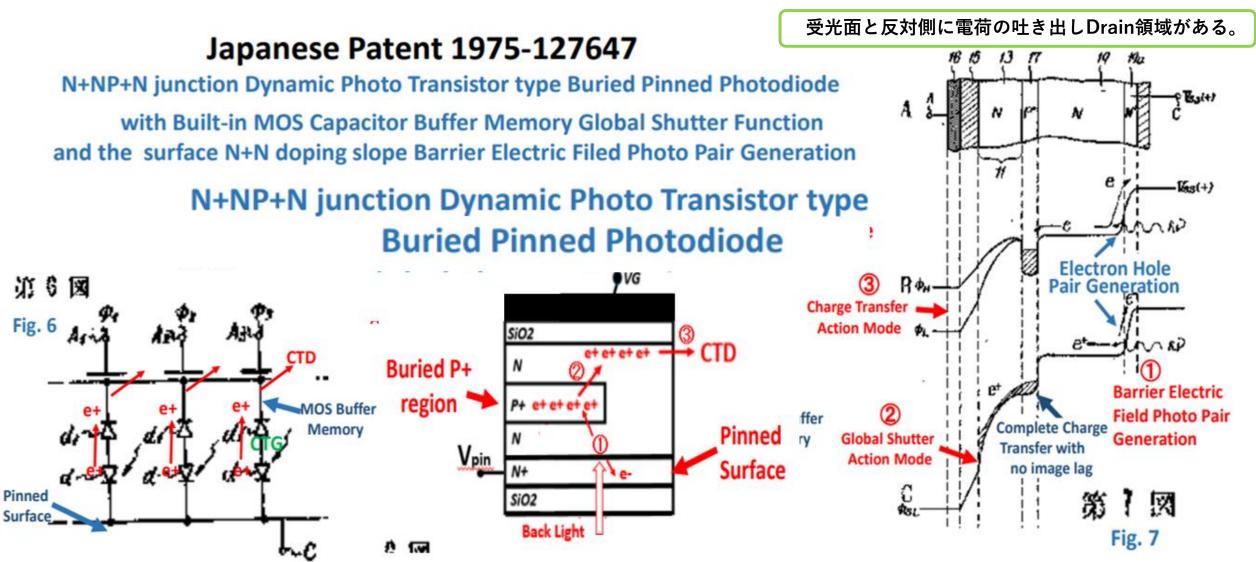

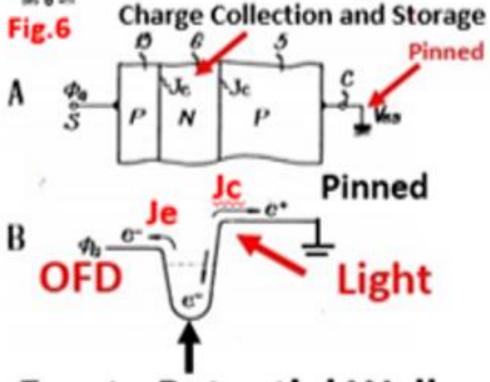

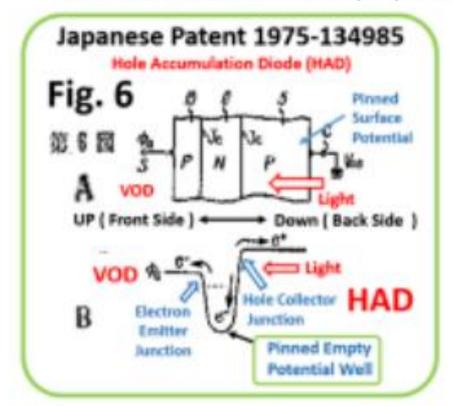

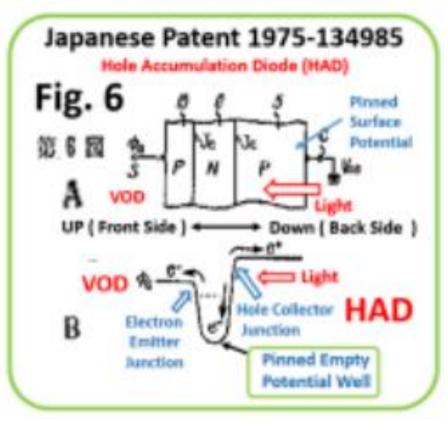

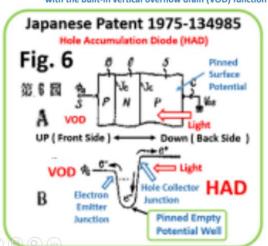

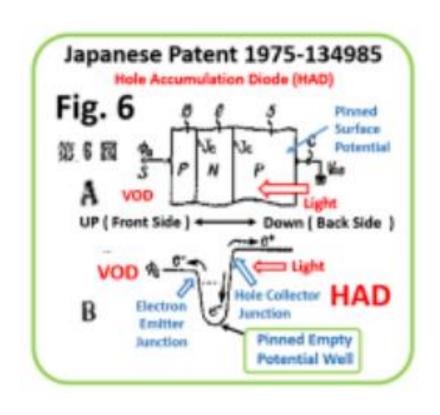

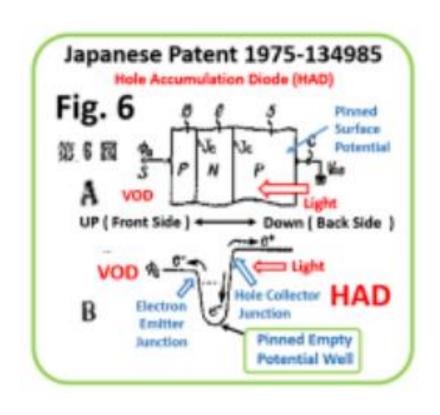

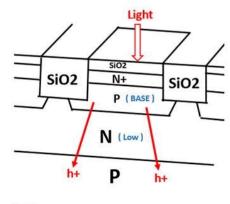

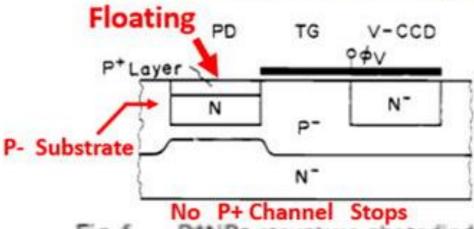

●The actual semiconductor device that has the super-light sensitive feature is Sony's hole accumulation diode (HAD) which is the NPNP triple junction type Pinned Buried Photodiode with the in-pixel vertical overflow drain (VOD)punch-thru action mode, which was invented in 1975 by Yoshiaki Hagiwara at Sony. See JPA1975-127646, JPA1975-127647 and JPA1975-134985. The first PNP double junction Pinned Buried Photodiode was developed and reported at SSDM1978 by Hagiwara team at Sony.

What is the actual semiconductor device that has the super-light sensitive feature, no image lag problem and no surface dark current noise problem but with the pinned surface and the in-pixel vertical overflow drain (VOD) function realizing the electric shutter function capability for fast action and snapshots pictures?

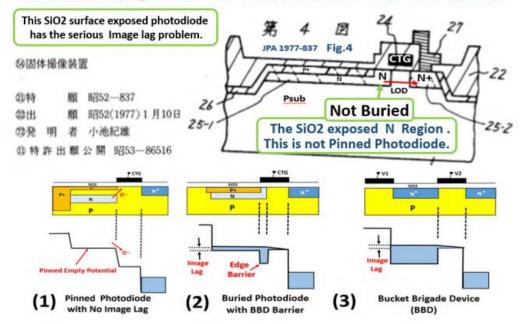

#### What is the difference between Pinned Photodiode and Buried Photodiode?

| Surface             | Buried Photodiode<br>with Floating Surface<br>and Serious Image Lag<br>by Ohmic RC Delay | Pinned Buried Photodiode with Pinned Surface,<br>connected directly to the metal or adjacent P+ Channel Stops<br>with No Image Lag of RC=0 delay time<br>and also with the Pinned Buried Empty Potential Well |                                      |

|---------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Junction            | Double PNP junction Photodiode                                                           |                                                                                                                                                                                                               | Triple PNPN junction Photodiode      |

| VOD                 | Х                                                                                        | Х                                                                                                                                                                                                             | 0                                    |

| No<br>Image Lag     | Х                                                                                        | 0                                                                                                                                                                                                             | 0                                    |

| Electric<br>Shutter | X                                                                                        | X                                                                                                                                                                                                             | 0                                    |

| Development         | NEC Dec 1982                                                                             | Sony Sep 1978                                                                                                                                                                                                 | Sony Oct 1987 ( Hamazaki Sony Team ) |

| Invention           | Phillips June 1975                                                                       | Sony Oct 1975 (JPA1975-127647, 1975-127647 and 1975-134985)                                                                                                                                                   |                                      |

What is the actual semiconductor device that has the super-light sensitive feature, no image lag problem and no surface dark current noise problem but with the pinned surface and the in-pixel vertical overflow drain (VOD) function realizing the electric shutter function capability for fast action and snapshots pictures?

What is the difference between Pinned Photodiode and Buried Photodiode?

| Surface             | Floating Surface<br>Serious Ohmic RC delay | Pinned Surface<br>Metal or P+ channel stop and R = 0        |                                      |

|---------------------|--------------------------------------------|-------------------------------------------------------------|--------------------------------------|

| Junction            | Double PNP junction Photodiode             |                                                             | Triple PNPN junction Photodiode      |

| VOD                 | х                                          | х                                                           | 0                                    |

| No<br>Image Lag     | х                                          | 0                                                           | 0                                    |

| Electric<br>Shutter | х                                          | х                                                           | 0                                    |

| Development         | NEC Dec 1982                               | Sony Sep 1978                                               | Sony Oct 1987 ( Hamazaki Sony Team ) |

| Invention           | Phillips June 1975                         | Sony Oct 1975 (JPA1975-127647, 1975-127647 and 1975-134985) |                                      |

JPA1976-65705 (Priority Patent 7506795 Netherland, filed on June 9, 197

川名喜之さんの貢献は、Bipolar Transistorの高性能化を実現した事です。

シリコン基板の裏面をエッチングして薄くすることにより、 Bipolar Transistor の ON 抵抗値 R の値を低減することです。

これはPNPトランジスタの Collector 端子を、外部の固定電圧値にピン留めすることが目的です。一番に固定ピン留めすることが重要だと理解したのはもとSONYの川名喜之さんの発明でした。しかし川名喜之さんは当時特許出願もせず、単純に製造技術のKNOWHOWとして社外秘として黙々とお仕事をSONのためにされておられました。その発明のお陰で、SONYは、民生用のON抵抗値Rの少ない世界一の性能を持つ、高性能パワートランジスターを、SONYは生産していました。

それを米国のTexas Instrument 社は注目し、SONYとTI社の技術提携が成立しました。 SONY 49 %で TI 51 %の出資での、世界初の半導体国際合弁会社が設立されました。

Emitter 端子と Collector端子が 抵抗値 R=0で動作することは重要な概念です。 しかしSONY以外の企業ではその認識が生産技術者には一般に欠如していた時代でした。 イメージセンサーの生産技術でもSONYだけが自然にその経験を継承され今に至ります。

#### http://koueki.jiii.or.jp/innovation100/innovation\_detail.php?eid=00059&test=open&age=stable-growth

発明公開の公式HPには「NECの寺西氏がPinned Photodiodeである」と記載されているがこれは事実誤認である。 「東芝の山田氏がVODの発明者である」とあるが記載されているがこれも事実誤認である。

#### 概要

撮像デバイスの研究開発は、19世紀後期のテレビジョン研究がスタートである。機械式、撮像管、固体撮像素子(以下「イメージセンサー」と呼ぶ)と発展し、社会に大きなインパクトを与えつつ、大きく発展してきた。

真空管の一種である撮像管は、サイズが大きい、割れ物である、消費電力が大きい、画像にゆがみがある、高価である、などの欠点があり、固体化が望まれていた。1960年代半ばにイメージセンサーの開発がスタートした。そのときは、MOS(Metal Oxide Semiconductor)型が中心であった。

1970年にBoyleとSmith(当時Bell研究所)が C C D(Charge-Coupled Device、電荷結合素子)を発表した<sup>1</sup>。構造が単純であり、イメージセンサーのような大規模なアレイ構造を製造するのに適していること、矢継ぎ早に C C D に改善が加えられたことから、イメージセンサー開発の中心は C C D になった。1970年後半からは開発の中心は日本に移った。1978年、山田哲生(当時 東芝)は、強い光が入射したときに縦線の偽信号を発生させるブルーミングを抑制する縦型オーバーフロードレイン構造を発明した<sup>2</sup>。1979年には寺西信一(当時 N E C)が、白傷や暗電流を大幅に低減し、残像や転送ノイズを解消する埋込フォトダイオード(Pinned Photodiode)を発明した<sup>3</sup>。これらの結果、C C D はまずムービーを、引き続きコンパクトデジタルスチルカメラを主な市場として量産されていった。

1990年代になると、CMOSの微細化が進み、4個ほどのトランジスターを画素内に配置することが可能になり、さらには、埋込フォトダイオードをCMOSイメージセンサーに適用することでCCDと同等以上の低ノイズが達成でき、世界の多くの機関で熱心に開発が進められた。2000年に米田智也ら(当時 キヤノン)が、強い光が入射したときに発生するシェーディングを抑制する構造を発明した4。2001年に鈴木亮司ら(当時 ソニー)が、裏面照射型に関する発明をした5。これらの技術開発によりCMOSイメージセンサーが主役になり、低消費電力という特性のお陰もあり、携帯電話に搭載され、生産量を爆発的に増加させていった。2010年に梅林拓ら(当時 ソニー)が、イメージセンサーに画像処理回路を積層する構造を発明し6、高速化と多機能化を飛躍的に推し進めた。

2014年には携帯電話用を中心に約38億個もの生産が行われた。パソコンカメラ、デジタルスチルカメラ、ゲームなどのコンシューマー用途、監視用、車載用、放送用カメラなどの社会インフラとして、さらには医療、科学用などあらゆるところでイメージセンサーが使われるようになった。

もとSONYの萩原良昭が真のOFD機能付きの Pinned Buried Photodiodeの発明者である。 See JPA1975-127646, JPA1975-127647 and JPA1975-134985

Japanese | English

#### Sony's Representative Inventions Supporting Stacked Multi-Functional CMOS Image Sensors

Sony Corporation Sony Semiconductor Solutions Corporation

#### Pinned Photodiode Adopted for Back-Illuminated CMOS Image Sensors

The history of Sony's inventions of image sensors goes back to the CCD era. Above all, Pinned Photodiode is a technology that contributes to improving the performance of back-illuminated CMOS image sensors, and the history of inventions and product development are as below.

In 1975, Sony invented a CCD image sensor that adopted a back-illuminated N+NP+N junction type and an N+NP+NP junction type Pinned Photodiode (PPD) (Japanese patent application number 1975-127646, 1975-127647 Yoshiaki Hagiwara). In the same year, inspired by such structure, Sony invented a PNP junction type PPD with VOD (vertical overflow drain) function (Japanese Patent No. 1215101 Yoshiaki Hagiwara). After that, Sony succeeded in making a principle prototype of a frame transfer CCD image sensor that adopted the PNP junction type PPD technology, having a high-impurity-concentration P+ channel stop region formed near a light receiving section by ion implantation technology for the first time in the world, and its technical paper was presented at the academic conference, SSDM 1978 (Y. Hagiwara, M. Abe, and C. Okada, "A 380H x 488V CCD imager with narrow channel transfer gates", Proc. The 10th Conference on Solid State Devices, Tokyo, (1978)). In 1980, Sony succeeded in making a camera integrated VTR which incorporated a one-chip frame transfer CCD image sensor that adopted the PNP junction type PPD. President Iwama in Tokyo, Chairperson Morita in New York, at the time held a press conference respectively on the same day, which surprised the world. In 1987, Sony succeeded in developing a 8 mm video camcorder that adopted, for the first time in the world, the interline transfer CCD image sensor, which incorporated "PPD having a high-impurity-concentration P+ channel stop region formed near the light receiving section by ion implantation technology" with VOD function, and became the pioneer of the video camera market. The PPD technology that has been nurtured through such a long history is still used in back-illuminated CMOS image sensors.

川名喜之さんは萩原が 1975 年 Sony 入社時から大変お世話になった恩人です。2021 年 6 月 2 1 日に死去されました。ご冥福をお祈りします。

川名喜之さんは 1932 年 3 月 1 日生まれで、東京大学を卒業後ソニーに入社し、1950 年後半にはソニーの新卒現役若手技術者として、Bipolar Transistor のデバイスプロセス技術の開発に従事されました。その時にシリコンチップの裏面を薄くして、Bipolar Transistor の ON-抵抗を減らし 大幅に Bipolar Transistor の電流特性を大幅に改善し、世界一の特性を持つ Bipolar Transistor を開発生産商品化が実現しました。米国 Texas Instrument 社がその SONY の Bipolar Transistor の開発生産技術に注目し、SONYとの技術提携が成立し、米国 Texas Instrument 社が 5 1 %出資で SONY が 4 9 %出資の TI Japan 社が、日本ではじめての国際合弁会社として設立しました。萩原が 1975 年に入社した当時、川名喜之さんは故岩間和夫社長が陣頭指揮をとるSONYのTOP極秘開発プロジェクトのCCDプロセス開発部の統括部長として勤務されていました。

From: Kawana Yoshiyuki <kawana@asahi-net.email.ne.jp>

Sent: Saturday, March 27, 2021 7:16 PM

To: hagiwara.yoshiaki@aiplab.com; 'seiichi-watanabe' <seiichi-watanabe@hinets.jp>

Cc: hagiwara@ssis.or.jp; hagiwara.yoshiaki@aiplab.com; hagiwara-yoshiaki@aiplab.com

Subject: RE: IEEE Life Fellow 講演会の件 萩原2020\_02\_11

萩原さん、

1978年当時NEC寺西さんの論文では始めN+Pダイオードでフォトダイオードを構成していたことが分かります。次に寺西さんは P+NP接合のフォトダイオードを採用し、残像が減ったと報告しています。このP+NPダイオードは論文を見る限り、pinned photodiodeではありません。N+Pダイオードはpinnedに出来ません。その延長でP+NPダイオードもこの論文ではpinnedになっていないのではと思います。

一方ソニーは1975年当時からMOSトランジスタをphoto-sensorとして使っていましたので初めからpinnedでした。こういう違いもあるのかなと思いました。

From: Kawana Yoshiyuki <kawana@asahi-net.email.ne.jp>

Sent: Sunday, March 28, 2021 3:43 PM

To: hagiwara.yoshiaki@aiplab.com; 'seiichi-watanabe' <seiichi-watanabe@hinets.jp>; 'Naohisa Ohta' <naohisa@kmd.keio.ac.jp>; narabu@gakushikai.jp; '鈴木俊治' <toshiharusuzuki11@gmail.com>; 'Tsugio Makimoto' <makimoto@tsugio.jp>; mukai@ssis.or.jp

Cc: hagiwara-yoshiaki@aiplab.com; hagiwara.yoshiaki@aiplab.com

Subject: RE: IEEE Life Fellow講演会の件 萩原2020\_02\_11

萩原さん、

コメントありがとうございます。1982年は1975年よりも7年経っています。振り返ってみるべきと思います。

SCOT

From: Kawana Yoshiyuki <kawana@asahi-net.email.ne.jp>

Sent: Wednesday, March 31, 2021 12:03 PM

To: seiichi-watanabe <seiichi-watanabe@hinets.jp>; hagiwara-yoshiaki@aiplab.com

Cc: seiichi-watanabe@hinets.jp

Subject: RE: 公益社団法人発明協会イノベーション100記事修正検討要請(追加資料)。

渡辺さん、

Overflow drainに関する特許紛争の提示ありがとうございます。ここでは発明協会の記事にある山田哲生さんの発明より早い 1975年の萩原良昭の特許が有効であったと証明されました。ご参考にしてください、という意味ですね。

当然、1979年発明とされる寺西信一さんの埋め込みフォトダイオードより早い1975年出願の萩原特許を見直してください、というのは変わらずお願いします、ということですね。

From: Kawana Yoshiyuki <kawana@asahi-net.email.ne.jp>

Sent: Sunday, April 4, 2021 8:14 PM

To: seiichi-watanabe <seiichi-watanabe@hinets.jp>; hagiwara-yoshiaki@aiplab.com

Cc: seiichi-watanabe@hinets.jp

Subject: RE: 公益社団法人発明協会イノベーション100記事修正検討要請(追加資料確認依頼)

渡辺さん、

発明協会への資料送付ありがとうございます。

発明協会からの返事が待たれますが、no responseのこともあるかもしれません。しかし、明らかに発明協会の見落としと思います。その場合には再度対応を検討することになるでしょうね。

SCOT

From: Kawana Yoshiyuki <kawana@asahi-net.email.ne.jp>

Sent: Saturday, April 17, 2021 7:38 AM

To: seiichi-watanabe <seiichi-watanabe@hinets.jp>; hagiwara-yoshiaki@aiplab.com

Cc: seiichi-watanabe@hinets.jp

Subject: RE: FW: 公益社団法人発明協会イノベーション100記事修正検討要請(追加資料確認依頼)

渡辺さん、萩原さん、

発明協会から意外な返事をいただきました。萩原さんの言われる通り、発明の優先の判断は学会によるべきものではないと思います。特許庁は自ら判断する能力がないと言ったことになりますね。特許を認可するかどうかは先願調査を含めて特許庁の判断によっているのではありませんか。特許庁は自らの役割を否定していると思います。

もう一度特許庁の役割に準じて<u>学会ではなく自らの判断を示してほしいです</u>。それを要求したらどうでしょうか。それでも不満足な 返事ならまた対応を考えましょう。

From: Kawana Yoshiyuki <kawana@asahi-net.email.ne.jp>

Sent: Thursday, April 22, 2021 11:37 AM

To: hagiwara-yoshiaki@aiplab.com; 'seiichi-watanabe' <seiichi-watanabe@hinets.jp>

Subject: RE: 従来のsingle接合型 Solar Cell の問題点をまとめてみました。

萩原さん、

ご存知の通り、1982年のIEEEの寺西さんの論文は埋め込みphotodiodeを述べていますが、PPDではありませんね。先に述べた通り、そのために残像が取り切れないのではと考えます。

From: Kawana Yoshiyuki <kawana@asahi-net.email.ne.jp>

Sent: Wednesday, April 28, 2021 8:07 PM

To: hagiwara-yoshiaki@aiplab.com; 'seiichi-watanabe' <seiichi-watanabe@hinets.jp>; narabu@gakushikai.jp; 'Naohisa Ohta'

<naohisa@kmd.keio.ac.jp>; tkst@ca2.so-net.ne.jp; hiromichi.matsui@restargp.com

Cc: hagiwara@ssis.or.jp; hagiwara-yoshiaki@aiplab.com

Subject: RE:ご無沙汰しております。萩原の近況報告とおねがいです。萩原2021\_04\_28

萩原さん、

お休み中でも研究に熱中するのは素晴らしいです。

ご説明理解いたしましたが、寺西さんの功績についてまだ理解できていません。埋め込みフォトダイオードでは電荷蓄積層が空乏化される状況ならば残像はなくなるとされますが、実験結果はそうなっていません。電荷蓄積層に蓄積された電子はフォトダイオードがpinされていなければ、瞬時にはなくなりません。そこが大切と思いますがどうですか。

SSIS半導体歴史館の掲載記事の訂正後の記載DRAFT(希望案)

#### 1975-1985 Improvement of photodiode for image sensor

(Phillips, Sony, Hitachi, NEC, Toshiba)

~ Discrete Semiconductor/Others ~

#### Photodiodes are used for photodetectors of image sensors.

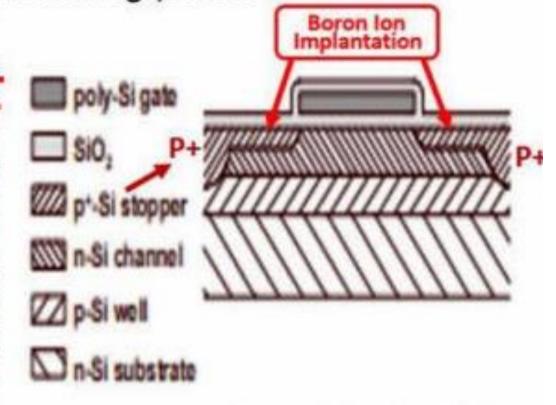

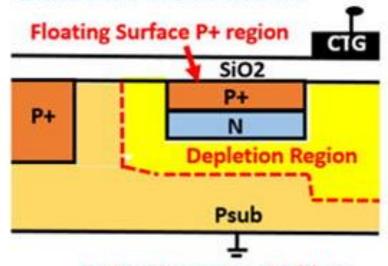

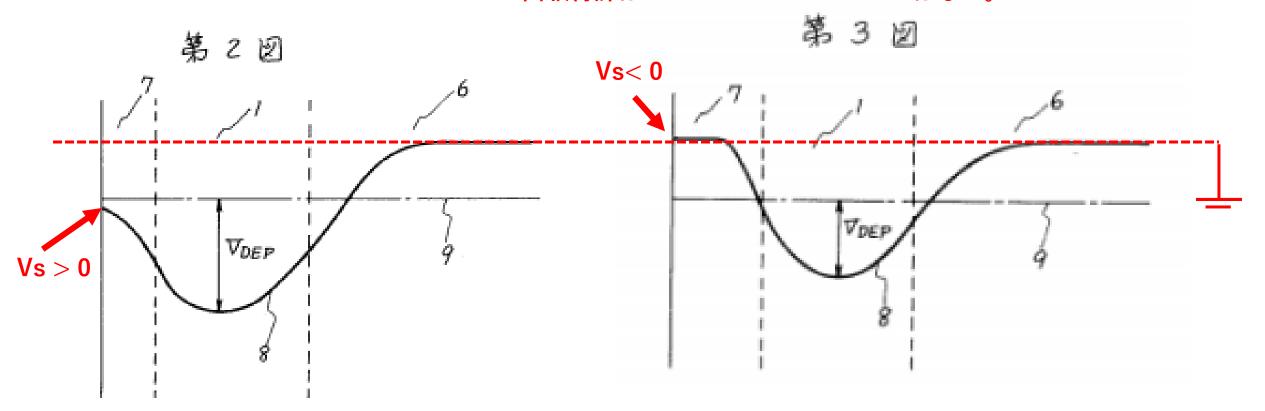

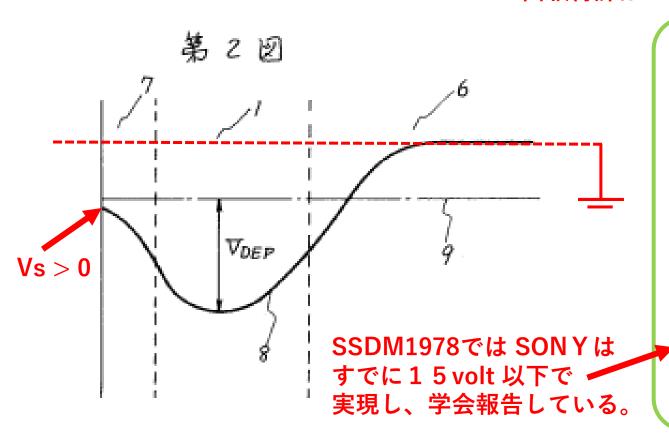

On June 9, 1975, Philips [1] proposed a double junction type Buried Photodiode for the first time in the world and used it in CCD image sensors. By providing an oxide-covered silicon P type surface region for the light incident section, the MOS sensor electrode that normally covers the entire light receiving surface of the photodiode can be eliminated to improve the light sensitivity greatly. Then, on Oct 23, 1975, Sony proposed a double junction type [2] and a triple junction type [3] Pinned Buried Photodiode. While Buried Photodiode with the floating surface is known to have the serious image lag problem, Pinned Buried Photodiode invented by Sony with the pinned surface hole accumulation region has the complete charge transfer capability and suffers no image lag problem.

In the same year, on November 10, 1975, inspired by such structure, Sony invented a PNP junction type Pinned Buried Photodiode with vertical overflow drain (VOD) function [4]. It is a basic proposal for a pinned buried photodiode with the electrical shutter function capability with a P+ layer on the surface of the light receiving part and the complete charge transfer capability achieving the no-image-lag feature. The vertical overflow drain (VOD) function capability is essential to achieve the electrical shutter function for fast action and snapshot motion pictures. This invention opened the new era of the completely mechanical-parts free and filmless video cameras.

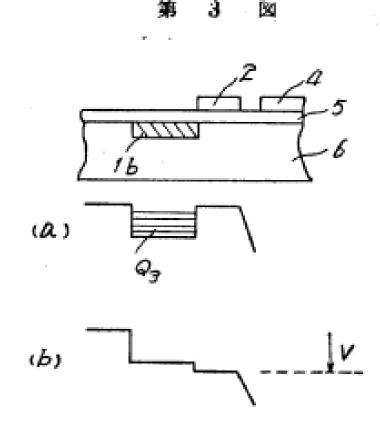

Next, proposals were made by Hitachi [5] to use the P+ layer as the substrate potential. In 1977, Hitachi presented a structure in which the high-concentration surface P+ layer is connected to a P-type substrate (well) and pinned it to the same potential but the charge N+ storage region is partially exposed to the silicon surface and, being floating, has the serious image lag problem. This photosensor was not Pinned Buried Photodiode.

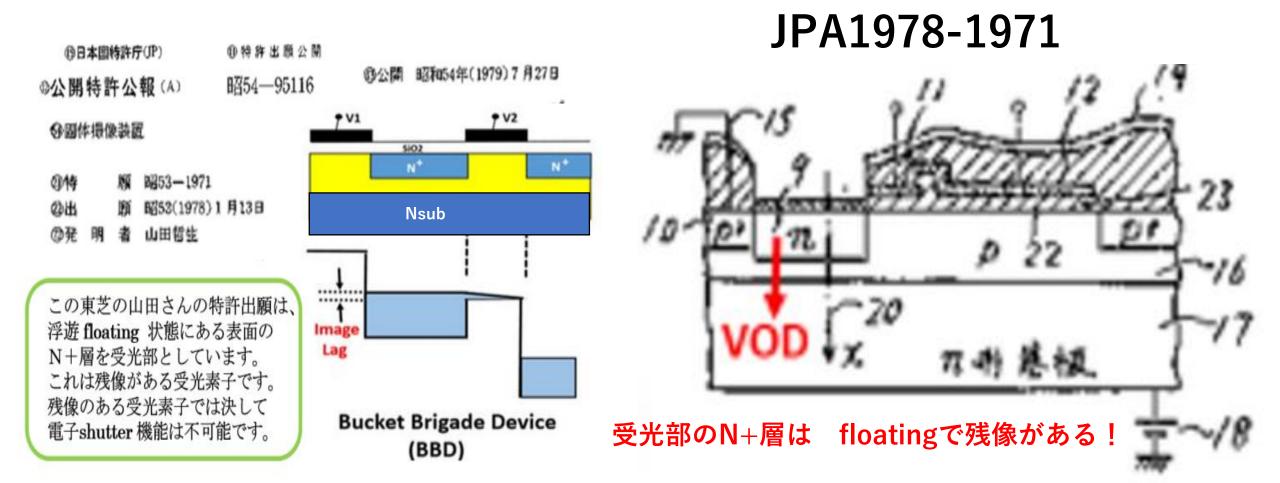

In 1978, Toshiba [6] also proposed an N+PNsub double junction type photodiode with the floating surface and the VOD function. However, it did not deplete the charge storage N layer completely and suffered the serious image lag problem.

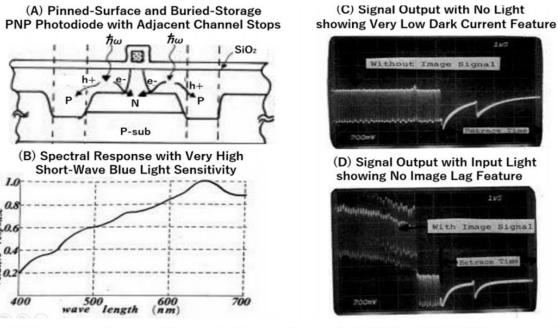

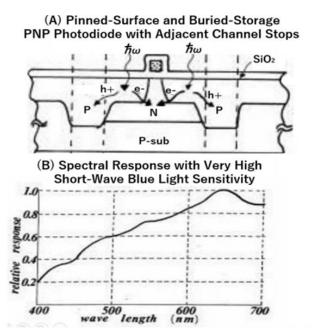

In 1978, Sony [7] announced an FT (Frame Transfer) -CCD image sensor, using the P+NP double junction type Pinned Buried Photodiode with the excellent blue light sensitivity, no surface dark current problem and the completely charge transfer capability of no image lag feature.

Sony succeeded for the first time in the world in prototyping a VTR-integrated color movie camera using a 2 / 3-inch 280,000-pixel FT-CCD image sensor that developed this technology in 1980 and held Sony Press Conference in Tokyo and in New York on the same date of July 1, 1980. The design methods based on this operation principle of the pinned buried photodiode focusing on this buried N-layer potential were then widely studied and have been standardized as the Pinned Buried Photodiode for today's CCD and CMOS image sensors [8].

The Pinned Photodiode is a Buried Photodiode in which the entire buried N layer is covered with a P layer. The part of the P layer on the light incident surface is heavily doped P+. Meanwhile there were many conference papers and patent applications reported which were very similar in the first glance but quite different from the Hagiwara 1975 invention and 1978 paper of the completely Pinned Buried Photodiode.

In 1980, NEC [9] filed a Japanese patent on Buried Photodiode and explained in detail the relationship between the electric potential of the N layer of a photodiode in which the P layer was pinned to the substrate potential and the potential of the transfer gate to an external circuit.

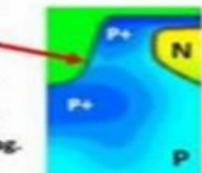

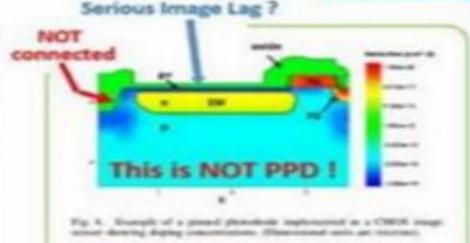

NEC claimed in the NEC IEDM1982 paper [10] that a principle of operation that completely transfers the signal charges would be achieved while keeping the potential of the depleted N layer higher than the channel potential of the transfer gate by a required value or higher, realizing image lag free operation. But NEC reported the serious image lag problem in the Buried Photodiode presented in the NEC IEDM1982 conference paper. NEC did not explain clearly the cause of the image lag problem. NEC did not explain the importance of the Pinned surface potential, which is very important to suppress the image lag problem.

Now it is very clear that, unless the surface P+ hole accumulation region is pinned by the adjacent P+ heavily doped channel stops region, the light incident P+ surface hole accumulation region would become floating, being surrounded and isolated electrically from the substrate ground potential by the deletion region extended by the deeply biased buried N storage region and causing the serious image lag problem.

Sony developed the first Pinned Buried Photodiode in 1978 and used it in a FT CCD image sensor. NEC also developed Buried photodiode in 1982, used it in an ILT CCD image sensor for the first time in the world. But the NEC Buried Photodiode reported in the NEC IEDM1982 paper had evidently the floating surface Buried Photodiode with a serious image lag problem, which was not evidently a Pinned Photodiode.

Kodak [11] also developed Pinned Buried photodiode in 1984, used it in an ILT CCD image sensor for the first time in the world and named this structure Pinned Photodiode. This device has features such as high light sensitivity, wide dynamic range, image lag free, much smaller dark current due to reduced influence of GR center on the light receiving surface, and no white scars. However, Kodak used the LOCOS isolation which induced the thermal oxide stress causing the yield problems of the serious dark current noise and defects of white spots. Sony 1978 Pinned Photodiode did not use the LOCOS isolation to improve the image sensor yield by suppressing the surface dark current problem.

In 1987, Sony 【12】 developed a 2 / 3-inch, 380,000-pixel CCD image sensor using a new type of photodetector, now called a Pinned Photodiode (Sony named it HAD: Hole Accumulation Diode), and installed it in the 8mm VTR integrated video camera "CCD-V90", using high energy ion implantation technology without using the LOCOS isolation technology to form the adjacent P+ heavily doped channel stops directly connected to the light illumination surface of the surface P+ hole accumulation region, which was originally developed in 1978 by Yoshiaki Hagiwara and reported for the first time in SSDM1978 conference in September 1978 【7】.

In the 1990s, the era of passport size video cameras demands compact CCD image sensors with large numbers of pixels (1/2 inch or smaller with 400,000 pixels or more). As a result, Pinned Photodiodes came to be widely used in CCD image sensors by manufacturers. In 1995, Kodak adopted them for CMOS image sensors. Pinned Photodiodes became the primary photodetector for CCD / CMOS image sensors. The Pinned Photodiode (also known as Buried Photodiode) technology was established as a widely used standard technology by active proposals of photodiode improvements from the late 1970s to the early 1980s.

#### References:

- [1] J. Santen, JPA1976-65705 with priority claimed by Patent 7506795 filed in Nederland on June 9, 1975.

- [2] Y. Hagiwara, JPA1975—127646 on N+PNP Pinned Photodiode with Global Shutter Buffer Memory

- [3] Y. Hagiwara, JPA1975-127647 on N+PN Pinned Photodiode with Global Shutter Buffer Memory

- [4] Y. Hagiwara, JPA1975-134985 on P+NPNsub Pinned Photodiode with VOD with no image lag

- [5] N. Koike, I. Takemoto, Patent JPA1977-837 on P+NP floating N storage of image lag problem.

- [6] T. Yamada, JPA1978—1971 on N+PNsub floating surface VOD function of image lag problem.

- [7] Y. Hagiwara, M. Abe, and C. Okada, "A 380H x 488V CCD imager with narrow channel transfer gates", Proc. The 10th Conference on Solid State Devices, Tokyo, (1978): Japanese Journal of Applied Physics, vol. 18, Supplements 18-1, pp. 335-340, (1979)

- [8] I. Kajino, M. Shimada, Y. Nakada, Y. Hirata and Y. Hagiwara, "Single Chip Color Camera Using Narrow channel CCD Imager with Over Flow Drain", Technical Report of The Institute of Image Information and Television Engineers, vol. 5, no. 29, pp. 32-3S, (1981) Version 2020/12/1

- [9] N. Teranishi, Y. Ishihara, H. Shiraki, Japanese Patent JP1980-138062

- [10] N. Teranishi, A. Kohono, Y. Ishihara, E. Oda, and K. Arai, "No image lag photodiode structure in in the interline CCD image sensor", 1982 International Electron Devices Meeting Digest of Technical Papers, pp. 324-327, (1982)

- [11] B. C. Burkey, W. C. Chang, J. Littlehale, T. H. Lee, T. J. Tredwell, J. P. Lavine, E. A. Trbk, "The Pinned Photodiode for an Interline-transfer CCD Image Sensor", IEDM1984, Digest of Technical Papers, paper (2.3), (1984).

- [12] M. Hamasaki, T. Suzuki, Y. Kagawa, K. Ishikawa, K. Miyata and H. Kambe, "An IT-CCD imager with electronically variable shutter speed", Technical Report of The Institute of Image Information and Television Engineers. vol. 12, no. 12, pp. 31-36, (1988)

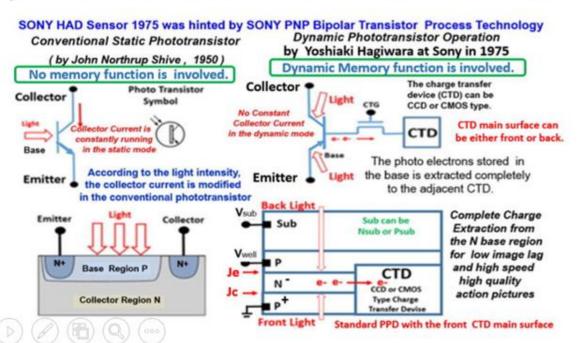

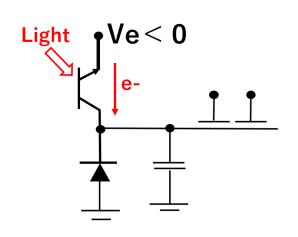

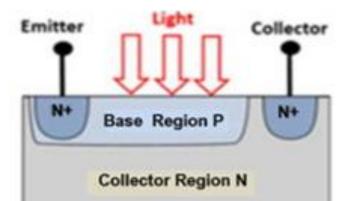

Double 接合型の受光素子自身は、すでに 1950 年に static photo transistor として John Northrup Shive が発明している。Philips 社からも CCD Image sensor の受光素子として 1975 年 6 月 9 日に発明特許が出願されている。また in-pixel 型の垂直 OFD (VOD) も Fairchild 社の James M. Early 氏により、1975 年 12 年 3 日に米 国特許 USP3896485 として出願されている。

しかし、Double 接合型および Triple 接合型の受光素子の 1 種で、Pinned Buried Photodiode と呼ばれる受光素子で、残像のない特長と縦型 OFD (VOD)機能の両方 を兼ね備え、その結果、電子シャッター機能を持つ受光素子は、1975年10年23日 にソニーの萩原良昭氏が世界で初めて発明した。萩原が1975年に世界で初めて 発明した、この縦型 OFD(VOD)機能が組み込まれた Pinned Buried Photodiode は別称、ソニーの HAD (Hole Accumulation Diode)とも呼ばれる。

その受光素子には過剰電荷を掃き出す垂直 Overflow Drain(VOD)機能が組み込まれていることを特許明細書 (JPA1975-134985 参照)に明示した。

また実施例図には埋め込み層の信号電荷が完全電荷転送された後に形成される Empty Potential Well 曲線が描かれ、残像のない特性を持つことも明示している。

受光面の表面 P+層が外部端子電圧により完全にピン留め固定されている状態を世界で初めて明示した。それが 残像のない特性を示す Pinned Photodiode の世界最初の1975年10月23日の発明考案特許となる。

その Pinned Buried Photodiode を搭載したフレームトランスファー型 CCD イメージセンサーの原理試作をソニーが世界で初めて成功させ、1978 年の SSDM1978 の 学会で萩原良昭氏が Pinned Photodiode 技術が記載されている世界最初の論文を発表した。

その Pinned Buried Photodiode を搭載したフレームトランスファー型 CCD イメージセンサーの原理試作をソニーが世界で初めて成功させ、1978 年の SSDM1978 の 学会で萩原良昭氏が Pinned Photodiode 技術が記載されている世界最初の論文を発表した。

実は、Double 接合型の受光素子(Static Photo Transistor )は既に 1950 年に John Northrup Shive が発明している。Emitter 端子と Collector 端子は外部電圧に連結 され、一方の端子電圧はピン留め固定され、もう一方端子電圧には出力抵抗が連結さ れ、その出力抵抗に流れる電流が floating base に照射する光量の影響を受けて変 動する原理を利用して受光素子である。これも 広い意味で、Photo Transistor も、 Photodiode としても機能するので、Pinned Photodiode の一種であるがイメージセ ンサーの学会用語としては区別する。

また電子 shutter 機能は、VOD 機能付きの Pinned Buried Photodiode でなければ実現は不可能である。その事実は理解するには、非常に専門性が高く、一般には全く理解されていないのが現状である。

ソニーの萩原良昭氏は、世界で初めて1975年に、電子 shutter 機能を持つ受光素子を発明考案した。これは VOD 機能を持つ受光素子で、現在、Pinned Buried Photodiode、と呼ばれる受光素子で、triple 接合型の dynamic photo thyristor 構造の punch thru 効果を利用したものである。これも萩原の 1975 年の発明である。

CMOS Image Sensor には Rotary Shutter 効果を防ぐ為に、Global Shutter (Snap Shot)機能を実現する為に不可欠な、in-pixel Buffer Memory 素子を 組み込んだ受 光素子を萩原は発明考案した。JPA1975-127646 と JPA1975-1276467 を参照。

オランダ・フィリップス社のヨハネス・ヘリト・フアン・サンテン氏とマルニクス・ フイラウメ・コレト氏の2名が、CCD型電荷転送装置に採用することを目的とした、 Double 接合型の受光素子を世界最初に1975年6月9日に考案発明した。VOD 機能はついていない。残像のない特長を明示する必要のある Pinned Photodiode で もない。受光面のP+層がNECのIEDM1982の論文と同様に完全にピン留めされて いる保証のない受光構造である。しかし、Image Sensor Array に採用された、double 接合型の埋め込み Photodiode 型の受光素子としては、世界最初の出願特許である。

従って、日本の発明協会のWE Bサイトには、「NEC の寺西氏が Pinned Photodiode の発明者」となっているが、Pinned Photodiode と埋め込み Photodiode の違いなどに関しても理解が不十分で説明もなく、明らかに事実誤認の掲載記事である。

また英国女王賞と日本の紫綬褒章でも、「NEC の寺西氏が NEC の寺西氏が Pinned Photodiode の発明者である」となっているが、これも明らかに事実誤認である。

オランダにおける特許 7506795 の出願者であるサンテン氏とコレト氏の2名は日本語特許出願 JPA1976-65705 の中で、1975 年 6 月 9 日優先権主張をしている。

問題はこの特許は構造特許である事である。受光部の動作に関する記載がない。学会でもまだ、Pinned Photodiodeの正確な定義が、1975年当時確立していない。

その残像のない特長は、暗電流特性の向上など性能や動作を重視して、名称を初めて 定義した KODAK 社の IEDM1984 の学会発表の論文まで判断を待つ必要があった。 この2人の特許出願者には残像に関する認識がまったく特許の中に見られないこと で論外とされたと思われる。Pinned Photodiode は、必ず、double 接合型の完全な 埋め込み受光部をもつ、Buried Photodiode であるが、double 接合型の完全な埋め 込み受光部をもつとされる Buried Photodiode でも、Pinned Photodiode でない場合 がある。この事実は、なかなか専門外の一般には理解が困難である。

イメージセンサーの学会でもこのオランダにおける特許 7506795 の特許の存在は 知られていたと思われるが、この特許出願には残像の関する記載が全く皆無である。 特許の説明文にも実施図にも明示されていない事が理由で、イメージセンサーの学 会でも吟味審査されたと推察する。結論として、「特許 7506795 は、Buried Photodiode 構造特許であるが、Pinned Photodiode 特許ではない」と結論され、学会でも水面 下の特許戦争の論点から早くからはずれた存在であったかもと知れない?

ではなぜ、現在、IEEE の学会でも、日本発明協会でも、「NEC の寺西氏が Pinned Photodiode の発明者である」として誤解し、日本半導体歴史館の公式 HP でも、「NEC の寺西氏が世界ではじめて残像に関する動作原理を解明した」と過大評価しているのであろうか?それは萩原の 1975 年の 3 件の日本語特許の存在が、英語圏の学識者にまったく、その詳細が知られることがなかったことが原因だったと推察する。

Fossum の 2014 年の論文の中でも、発明協会の HP でも、日本歴史館の HP におい ても、萩原の 1975 の 10 月 23 日の特許出願の JPA1975-127646 と JPA1975-127647 の引用がない。その事実から見ると、萩原の 1975 の 10 月 23 日の 2 件の特許出願の 存在すら気が付いておらず、見落としている可能性が大きい。少ない情報下での、間 違った事実誤認により、「NEC の寺西氏が Pinned Photodiode の発明者である」と して誤解されたと思われる。イメージセンサーの専門家でも、必ずしも、半導体デバ イス物理の専門家でない場合が多く、理解が困難で、専門性の高い論点で、重要な誤 解を招くことが多い。この場合は、非常に深刻な誤解があると思われる論点である。

論点(1)サンテン氏とコレト氏の2名の出願特許は VOD 機能付の Pinned Photodiode ではない。Pinned Photodiode 自身でもない? PNPsub 接合型の受光素子構造の発明であるが、表面の表面 P 層が必ずピン留めされ電位が固定となるとは限らない??その論点で一般に広く今まで注目される事はなかったのかも?

- 論点(2) NEC の寺西氏の出願特許も 実は Pinned Photodiode ではない。 受光面が基板と同電位にピン留めされていない事がその証拠である。

- 論点(3) NEC の寺西氏の IEDM1982 の論文も Pinned Photodiode ではない。 論文の中で重大な残像がとりきれてない事を報告している。

論点(4) Fossum の論文では、「残像がない事が、Pinned Photodiode の絶対必要条 件である」と論説しているが、「表面の P+層がピン留めされていないと、残像が生 じる | ということを理解していない?また「萩原の SSDM1978 の論文には残像の記 載がない、 また、1975-134985 特許にも残像の記載がない」と論説した。 しかしこれは事実誤認である。また、出願特許 JPA1975-127646 と JPA1975-127647 の存在を Fossum は知らず、引用もせず、当然、理解もしておらず、情報不 足から、間違った結論を Fossum は出すに至ったと思われる。

論点(5) IEEE の学会も、それに追従する発明協会の公式 HP でも、また、日本半導体歴史館の HP の記載に於いても萩原 1975 年出願の JPA1975-127646 と JPA1975-127647 の存在が知らず、情報不足からか、間違った結論を出すに至ったと思われる。

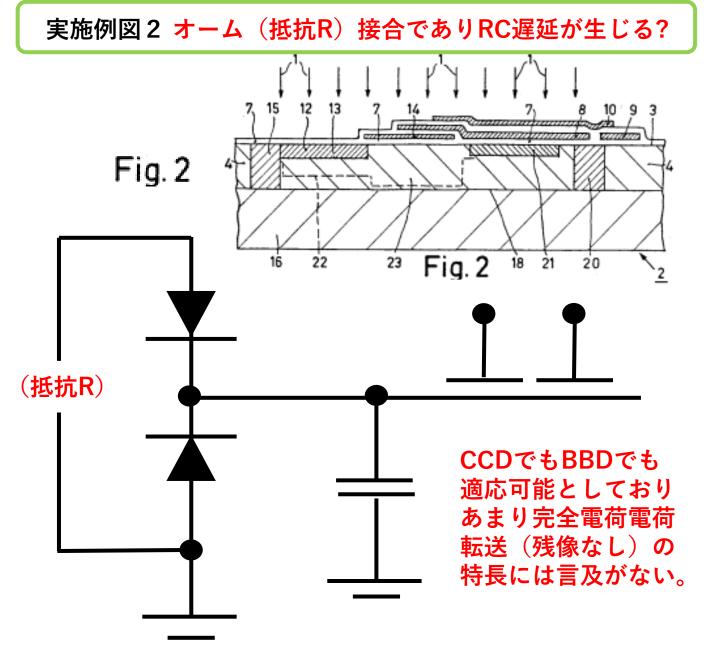

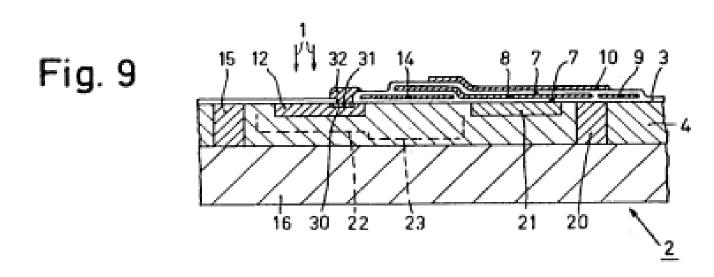

### JPA1976-65705 (Priority Patent 7506795 Netherland, filed on June 9, 1975)

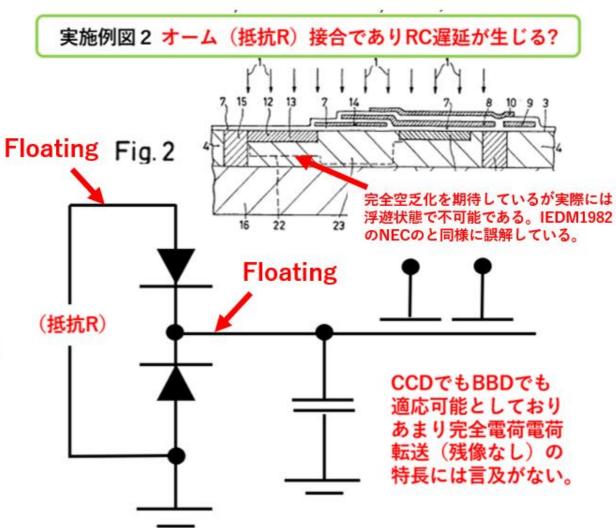

p 形表面領域 /3 および p 形 基板 14 との オーム接続に代え、 p 形領域 /2 の電気接続には整流接続を備えることもできる。

<u> 新 9 凶 は</u> か か る 装 置 の 実 能 例 即 ち 第 3 実 能 例 の 断面図である。本例装置はその大部分が第1実施 例で説明した装置に対応するので、便宜上同じ数 字を用いて示してある。第 / 実施 例による装 置と の重大な相違点は、p形姿面領域はをp形領域は には最早や接続せず、p形飯娘パから横方向に分 離し、これは図示しないり形指状部のも同じであ る。各 p 形 額 域 /2 に n 形 表 面 額 域 3/ を 配 款 し と の n 形表面領域 3/ は適切な単圧を供給するための 撥成32を傾える。 p形 領域/2 と共に 軽流 p-n接 ·ることができる。 削配注入した電子は先に説明し た態様でゲート電板14の下に集めることができる。 かかる構造の利点は、放射線の吸収によつて発生 した電子がトランジスタの利得率だけ増強される ので、装置の感度がかなり増大することである。

### JPA1976-65705 (Priority Patent 7506795 Netherland, filed on June 9, 1975)

p 形表面領域 13 および p 形 基板 16 との オーム接続に代え、 p 形領域 12 の電気接続には整流接続を備えることもできる。

朝ヲ図はかかる装置の実施例即ち窮ヲ実施例の 断面図である。本例装置はその大部分が第1実施 例で聪明した装置に対応するので、便宜上同じ数 字を用いて示してある。第 / 実施 例による装 置と の 重大 左相連点は、 p形 姿面 領域 /2 を p形 領域 /5 には最早や接続せず、p形飯娘パから横方向に分 離し、これは図示しないり形指状部々も同じであ る。各 p 形 領域 /2 に n 形 表面 領域 3/ を配 散 し こ の n 形表面領域 3/ は適切な 単圧を供給するための 撥成32を傾える。 p形 領域/2 と共に 軽流 p-n接 ·ることができる。 削配注入した電子は先に説明し た態様でゲート電板14の下に集めることができる。 かかる構造の利点は、放射線の吸収によつて発生 した電子がトランジスタの利得率だけ増強される ので、装置の感度がかなり増大することである。

### 実施例図9 従来の1950年発明の Static Photo Transistor 構造

John Northrup Shive, 1950

#### LPD (µm) **Drift Field Transistor Light Penetration Depth in Silicon** 10 **VB** N 0.1 Si Crystal 0.01 λ(µm) Incident Light Wave Length 0.4 0.6 0.5 0.7 Figure 6 of JAP 1975-134985 Figure 7 of JAP 1975-127647 Pinned **Pinned** $\propto$ Grounded High Blue Light QE No Surface Dark Current Control Light Surface High Blue Light QE Dark Current **Empty Potential Well** with No Image Lag No Image Lag Global Shutte **Function** Hagiwara invented PNP junction type PPD in 1975 with **Empty Potential Well** (1) blue light 100% QE, (2) No Surface Dark Current and with No Image Lag (3) No Image Lag, Complete Charge Transfer features.

### JPA1975-127646

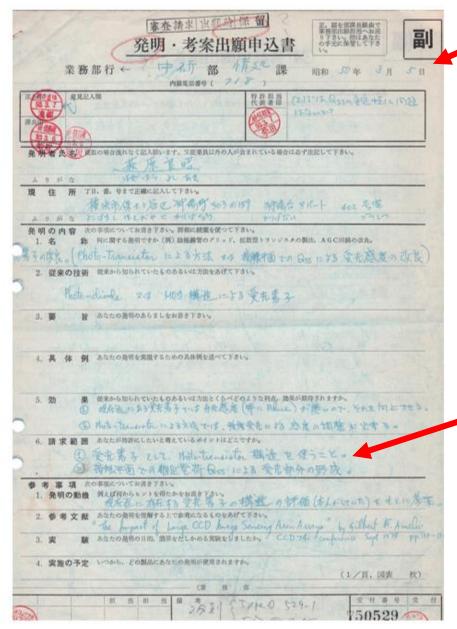

JPA1975-134985 特許は すでに 1975年3月5日に 発明考案された記録が存在する。公式に特許として 出願登録されたのは1975年10月23日である。

### 受光素子として Phototransistorを使うこと

The N+PNP junction type Dynamic Photo Transistor Structure

Pinned Photodiode and Sony Hole Accumulation Diode (HAD)

with the vertical overflow drain (VOD) function

invented by Hagiwara at Sony in 1975

Hagiwara's Lab Note at Sony in February 1975

# Toshiba Yamada-san Patent on the double junction Photodiode with Substrate Overflow Drain Function

This is not a Pinned Photodiode.

Japanese | English

### Sony's Representative Inventions Supporting Stacked Multi-Functional CMOS Image Sensors

Sony Corporation Sony Semiconductor Solutions Corporation

### Pinned Photodiode Adopted for Back-Illuminated CMOS Image Sensors

The history of Sony's inventions of image sensors goes back to the CCD era. Above all, Pinned Photodiode is a technology that contributes to improving the performance of back-illuminated CMOS image sensors, and the history of inventions and product development are as below.

In 1975, Sony invented a CCD image sensor that adopted a back-illuminated N+NP+N junction type and an N+NP+NP junction type Pinned Photodiode (PPD) (Japanese patent application number 1975-127646, 1975-127647 Yoshiaki Hagiwara). In the same year, inspired by such structure, Sony invented a PNP junction type PPD with VOD (vertical overflow drain) function (Japanese Patent No. 1215101 Yoshiaki Hagiwara). After that, Sony succeeded in making a principle prototype of a frame transfer CCD image sensor that adopted the PNP junction type PPD technology, having a high-impurity-concentration P+ channel stop region formed near a light receiving section by ion implantation technology for the first time in the world, and its technical paper was presented at the academic conference, SSDM 1978 (Y. Hagiwara, M. Abe, and C. Okada, "A 380H x 488V CCD imager with narrow channel transfer gates", Proc. The 10th Conference on Solid State Devices, Tokyo, (1978)). In 1980, Sony succeeded in making a camera integrated VTR which incorporated a one-chip frame transfer CCD image sensor that adopted the PNP junction type PPD. President Iwama in Tokyo, Chairperson Morita in New York, at the time held a press conference respectively on the same day, which surprised the world. In 1987, Sony succeeded in developing a 8 mm video camcorder that adopted, for the first time in the world, the interline transfer CCD image sensor, which incorporated "PPD having a high-impurity-concentration P+ channel stop region formed near the light receiving section by ion implantation technology" with VOD function, and became the pioneer of the video camera market. The PPD technology that has been nurtured through such a long history is still used in back-illuminated CMOS image sensors.

歴史館の記述には事実誤認があります。SONYの開発努力に関する記載が不当です。世界ではじめての Pinned Buried Photodiodeの特許は 1975-127646 と 1975-127647 です。この引用がありません。

受光面と反対側に電荷の吐き出しDrain領域がある。 **Japanese Patent 1975-127646** N+NP+NP junction type Buried Pinned Photodiode with Built-in MOS Capacitor Buffer Memory Global Shutter Function and the surface N+N doping slope Barrier Electric Field Photo Pair Generation Fig. 6 N+NP+NP junction type **Buried Pinned Photodiode Barrier Electric Field Photo Pair** harge Transfer SiO<sub>2</sub> Generation **Action Mode** MOS Buffer Memory ③ CTD N Pinned P+ Surface N-Vpin Global Shutter Fig. 7 N+ **Action Mode**

**Back Light**

Pinned Surface

歴史館の記述には事実誤認があります。SONYの開発努力に関する記載が不当です。世界ではじめての Pinned Buried Photodiodeの特許は 1975-127646 と 1975-127647 です。この引用がありません。

受光面と反対側に電荷の吐き出しDrain領域がある。

Double Junction Pinned Photodiode with Buried Base N Region for Photo

**Empty Potential Well**

with Complete Charge Transfer and No-Image-Lag Feature

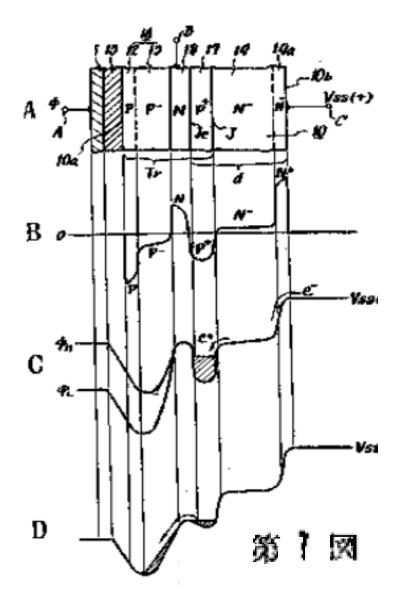

## Original Japanese Patent Claims JPA1975-134985

特性健康の範囲

PNP double junction photodiode in a substrate wafer resuting in a PNPNsub triple junction type dynamic photo thyristor

In a semiconductor substrate (Nsub) the first region (P1) is formed. Then the second region (N) is formed upon it forming the collector junction (Jc). Then on the second region (N), the emitter Junction (Je) is formed. The photo charge is stored in the base region (N) and then transferred to the adjacent charge transfer device (CTD).

萩原は1975年の JPA1975-134985特許で、世界で初めて、垂直(Vertical)型過剰Overflow信号電荷の掃き出し機能を持つDrain (VOD)機能を考案して(SONYのHADセンサーの)特許出願しています。

#### Japanese Patent 1975-134985

Hole Accumulation Diode (HAD)

P+NPNsub junction Dynamic Photo Thyristor type Pinned Photodiode with the built-in vertical overflow drain (VOD) function

受光面と反対側に電荷の吐き出しDrain領域がある。

Fig.3 Conventional Buried Channel CCD type MOS Capacitor type Photodiode Structure Meta SiO<sub>2</sub> 第3回 , Fig. 3 N Psub Fig.4 Surface VOD type Schottky Barrier type Photodiode Metal Fig.4 Psub Pinned Photodiode Fig.5 N Psub Fig.5 Surface VOD type Pinned Photodiode

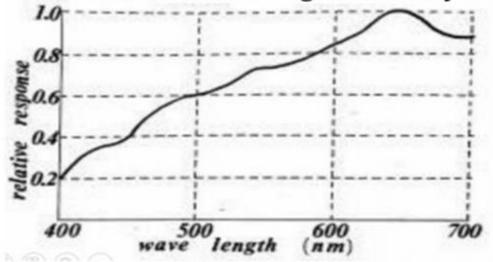

(A) Pinned-Surface and Buried-Storage PNP Photodiode with Adjacent Channel Stops

(B) Spectral Response with Very High Short-Wave Blue Light Sensitivity

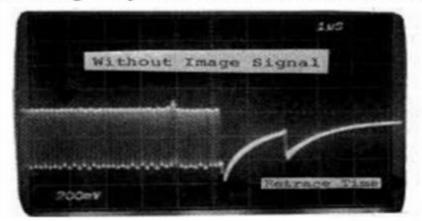

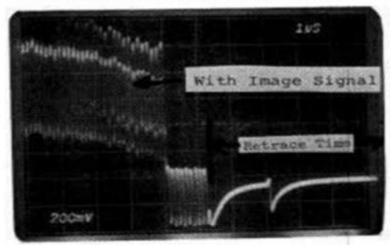

(C) Signal Output with No Light showing Very Low Dark Current Feature

(D) Signal Output with Input Light showing No Image Lag Feature

Yoshiaki Hagiwara, Motoaki Abe and Chikara Okada, "A 380H x 488V CCD Imager with Narrow Channel Transfer Gates", Proceeding of 10<sup>th</sup> Conference on Solid State Devices, Tokyo 1978, Japanese Journal of Applied Physics, Volume 18 Sup 18-1, pp. 367-369.

萩原は1975年の JPA1975-134985特許で、世界で初めて、垂直(Vertical)型過剰Overflow信号電荷の掃き出し機能を持つDrain (VOD)機能を考案して(SONYのHADセンサーの)特許出願しています。

### Japanese Patent 1975-134985

Hole Accumulation Diode (HAD)

P+NPNsub junction Dynamic Photo Thyristor type Pinned Photodiode with the built-in vertical overflow drain (VOD) function

構造体は上下を反対に 逆さまにしても 同一の同じ構造です。

### 特許請求範囲

(1)半導体基体(Nsub)に、第1電導型の第1 半導体領域(P well) と、(2) 之の上に形成された 第2導電型の第2半導体領域(N) とが 形成されて (3) 光感知部(N)と 之よりの電荷を転送する電荷 転送部(CTD)とが(4)上記半導体基体(Nsub) の主面に沿う如く配置されて成る(5)固体撮像 装置に於いて、上記光感知部 (N) の上記第2 半導体領域(N)に整流性接合(Je)が形成され、 該接合(Je)をエミッタ接合とし、(6)上記第1 (P well)及び第2半導体領域 (N) 間の接合を コレクタ接合(Jc)とする (PNP)トランジスタを形成 し(7) 該 トランジスタのベースとなる上記第2半 導体領域(N)に光学像に応じた電荷を蓄積し ここに蓄積された電荷を上記転送部(CTD)に 移行させてその転送を行うようにしたことを 特徴とする固体撮像装置。

特許請求範囲には受光面が Emitter 接合とは記載されていない。 表面照射型でも裏面照射型でもこの特許は有効です。 歴史館の記述には事実誤認があります。SONYの開発努力に関する記載が不当です。世界ではじめての Pinned Buried Photodiodeの特許は 1975-127646 と 1975-127647 です。この引用がありません。 萩原は1975年の JPA1975-134985特許で、世界で初めて、垂直(Vertical)型過剰Overflow信号電荷の 掃き出し機能を持つDrain (VOD)機能を考案して(SONYのHADセンサーの)特許出願しています。

(1) Wrong?

In 1975, Sony proposed using a PNP transistor as the photodetector [3]. By providing a P+ layer (emitter) for the light incident section, the sensor electrode that covers the entire light receiving surface of the photodiode can be eliminated to improve the light sensitivity greatly. It was a basic proposal for a pinned photodiode with a P+ layer on the surface of the light receiving part, with the buried charge collecting storage (base) with the complete charge transfer mode with no image lag feature.

#### Japanese Patent 1975-134985

Hole Accumulation Diode (HAD)

P+NPNsub junction Dynamic Photo Thyristor type Pinned Photodiode with the built-in vertical overflow drain (VOD) function

#### 特許請求範囲

(1)半導体基体(Nsub)に、第1電導型の第1 半導体領域(Pwell)と、(2)之の上に形成された 第2導電型の第2半導体領域(N)とが形成されて (3)光感知部(N)ととよりの電荷を転送する電荷 転送部(CTD)とが(4)上記半導体基体(Nsub) の主面に沿う如く配置されて成る(5)固体撮像 装置に於いて、上記光感知部(N)の上記第2 半導体領域(N)に整流性接合(Je)が形成され、 該接合(Je)をエミッタ接合とし、(6)上記第1 (Pwell)及び第2半導体領域(N)間の接合を コレクタ接合(Jc)とする(PNP)トランジスタを形成 し(7)該トランジスタのベースとなる上記第2半 導体領域(N)に光学像に応じた電荷を蓄積し ここに蓄積された電荷を上記転送部(CTD)に 移行させてその転送を行うようにしたことを 特徴とする固体操像装置。

特許請求範囲には受光面が Emitter 接合とは記載されていない。 表面照射型でも裏面照射型でもこの特許は有効です。

構造体は上下を反対に 逆さまにしても 同一の同じ構造です。

歴史館の記述には事実誤認があります。SONYの開発努力に関する記載が不当です。世界ではじめての Pinned Buried Photodiodeの特許は 1975-127646 と 1975-127647 です。この引用がありません。

萩原は1975年の JPA1975-134985特許で、世界で初めて、垂直(Vertical)型過剰Overflow信号電荷の掃き出し機能を持つDrain (VOD)機能を考案して(SONYのHADセンサーの)特許出願しています。

世界をリードするSONYでは、残像問題は MOS・CCD容量型受光素子と萩原の1975年の発明で解決ずみでした。SONYは残像のない高性能ビデオカメラの実現と商品化はSONYの重点課題でした。

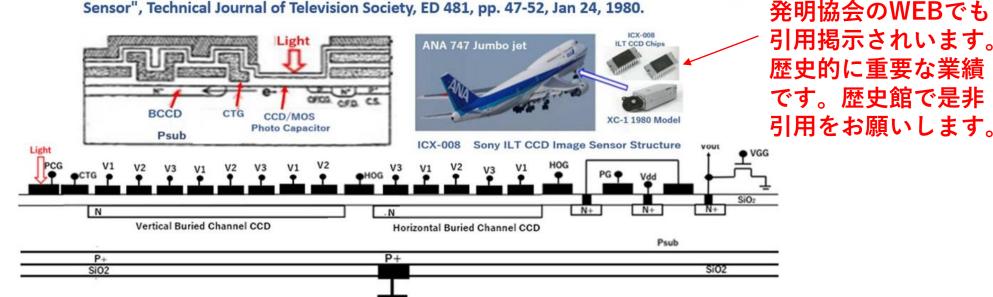

Sony developed the CCD/MOS dynamic photo capacitor type photon detecting device and the CCD type Charge Transfer Device (CTD) for an interline CCD image sensor in 1980 with the complete charge transfer of no image lag feature for fast action pictures.

Y. Kanoh, T. Ando, H. Matsumoto, Y. Hagiwara and T. Hashimoto, "Interline Transfer CCD Image Sensor", Technical Journal of Television Society, ED 481, pp. 47-52, Jan 24, 1980.

歴史館の記述には事実誤認があります。SONYの開発努力に関する記載が不当です。世界ではじめての Pinned Buried Photodiodeの特許は 1975-127646 と 1975-127647 です。この引用がありません。

萩原は1975年の JPA1975-134985特許で、世界で初めて、垂直(Vertical)型過剰Overflow信号電荷の掃き出し機能を持つDrain (VOD)機能を考案して(SONYのHADセンサーの)特許出願しています。

世界をリードするSONYでは、残像問題は MOS・CCD容量型受光素子と萩原の1975年の発明で解決ずみでした。SONYは残像のない高性能ビデオカメラの実現と商品化はSONYの重点課題でした。

Sony used the P+NP double junction type Pinned Photodiode for 380H x 488V in 1978 and 570H x488V one chip color FT CCD Image Sensors in 1980.

Yoshiaki Hagiwara, SSDM1978 'Paper and Japanese Patent No. 1215101 (Japanese Patent Application JPA 1975-134985)

Yoshiaki Hagiwara, Motoaki Abe and Chikara Okada, "A 380H x 488V CCD Imager with Narrow Channel Transfer Gates". Proceeding of the 10th Conference on Solid State Devices, Tokyo 1978;

Japanese Journal of Applied Physics, Volume 18(1979) Supplement 18-1, pp. 335-340.

I. Kajino, M. Shimada, Y. Nakada, Y. Hirata and Y. Hagiwara," Single Chip Color Camera Using Narrow channel CCD Imager with Over Flow Drain", Technical Report of The Institute of Image Information and Television Engineers, vol. 5, no. 29, pp. 32-3S, (1981).

Sony 1980 Video Movie has in one body an 8 mm VTR and One Chip FT CCD Image Sensor with the PNP Double Junction type Pinned Photodiode developed by Hagiwara in 1978

世界発のPinned Buried Photodiode搭載のビデオカメラとVTRの一体化のビデオムービーカメラです。 1980年7月1日に新聞発表しています。 歴史的に重要な業績です。 歴史館で是非引用をお願いします。

(1) 歴史館の記述には事実誤認があります。SONYの開発努力に関する記載が不当です。世界ではじめての Pinned Buried Photodiodeの特許は 1975-127646 と 1975-127647 です。この引用がありません。

世界をリードするSONYでは、残像問題はMOS・CCD容量型受光素子と萩原の1975年の発明で解決ずみでしたがSONYはライバル会社の追従を恐れて沈黙を続けていました。

Yoshiaki Hagiwara, Motoaki Abe and Chikara Okada, "A 380H x 488V CCD Imager with Narrow Channel Transfer Gates", Proceeding of 10<sup>th</sup> Conference on Solid State Devices, Tokyo 1978, Japanese Journal of Applied Physics, Volume 18 Sup 18-1, pp. 367-369.

メカ・フリーでかつ、Filmless で 残像のない高速アクション撮影が可能な電子shutter機能を実現する事は 盛田会長と岩間社長が打ち出した、1970年のCCDの発明以来のSONYの極秘商品目標でした。

(1) 歴史館の記述には事実誤認があります。SONYの開発努力に関する記載が不当です。世界ではじめての Pinned Buried Photodiodeの特許は 1975-127646 と 1975-127647 です。この引用がありません。

世界をリードするSONYでは、残像問題はMOS・CCD容量型受光素子と萩原の1975年の発明で解決ずみでしたがSONYはライバル会社の追従を恐れて沈黙を続けていました。

The N+PNP junction type Dynamic Photo Transistor Structure

Pinned Photodiode and Sony Hole Accumulation Diode (HAD)

with the vertical overflow drain (VOD) function

invented by Hagiwara at Sony in 1975

Hagiwara's Lab Note at Sony in February 1975

In 1975 at Sony, Yoshiaki Hagiwara filed three Japanese patents JPA1975-127646, JPA1975-127647 and JPA1975-134985 on the Pinned Surface Photodiode with the VOD function which is later called as Sony Hole Accumulation Diode (HAD). Hagiwara did not file a patent on the SiO2 device isolation but this lab note shows that Hagiwara had an idea of forming the Shallow Trench Isolation by the Local Oxidation Method, which was hinted by the LOCOS isolation in 1970s.

メカ・フリーでかつ、Filmless で 残像のない高速アクション撮影が可能な電子shutter機能を実現する事は 盛田会長と岩間社長が打ち出した、1970年のCCDの発明以来のSONYの極秘商品目標でした。

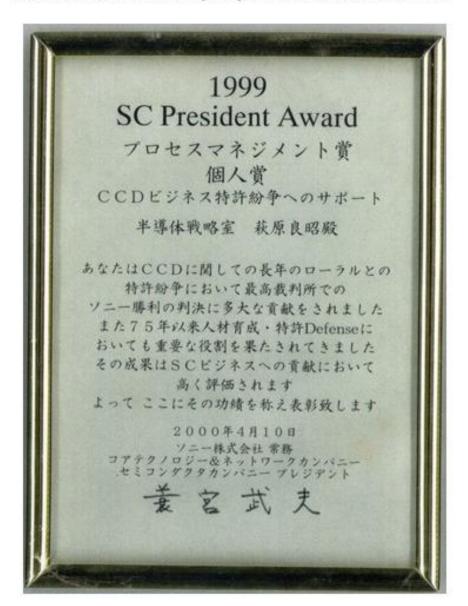

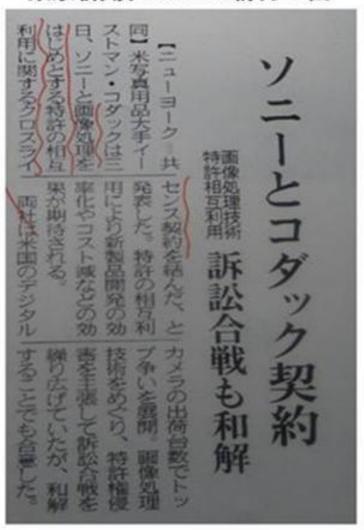

# Newspaper describing Sony Victory on Sony-Fairchild Patent War

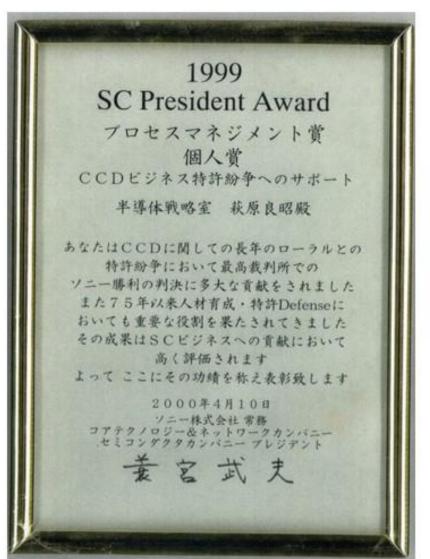

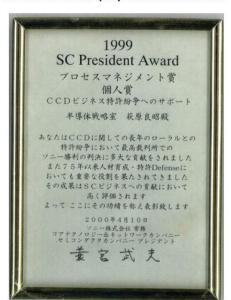

### Semiconductor Company President Award 1999

Thank You Message from

Sony Chairman Ohga

to Yoshiaki Hagiwara

for the contribution

to Sony Victory

on Sony-Fairchild Patent War

### Newspaper describing Sony Victory on Sony-Fairchild Patent War

#### Semiconductor Company President Award 1999

Thank You Message from

Sony Chairman Ohga

to Yoshiaki Hagiwara

for the contribution

to Sony Victory

on Sony-Fairchild Patent War

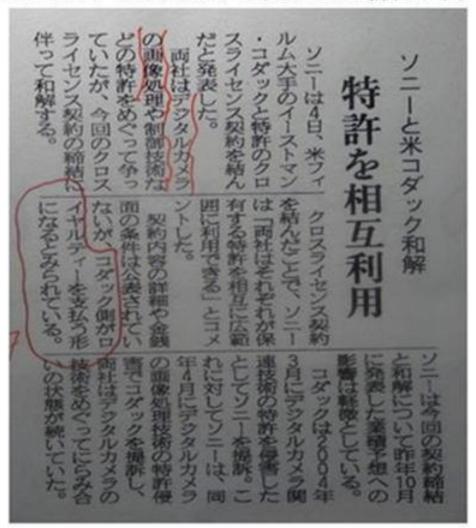

### フジサンケイビジネスアイ、2007.1.4 朝刊 3 面

東京新聞、2007.1.4 朝刊 3 面

KODAK Sony Patent Agreement on Image Sensor and Digital Camera 2007.1.4

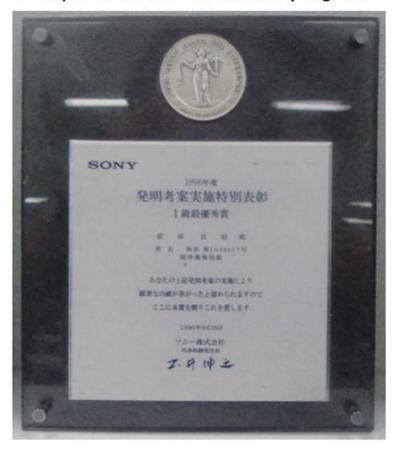

Sony Central Research Center Crystal Award 1978 on Space and Time Analysis of Image Sensor Signal

Semiconductor Company President Award 1999

Thank You Message from Sony Chairman Ohga to Yoshiaki Hagiwara for the contribution to Sony Victory on Sony-Fairchild Patent War

Newspaper describing Sony Victory on Sony-Fairchild Patent War

1996

Electric Shutter Basic Patent Award from Sony President Idei to Yoshiaki Hagiwara for Japanese Patent 1977-128885 by Hagiwara

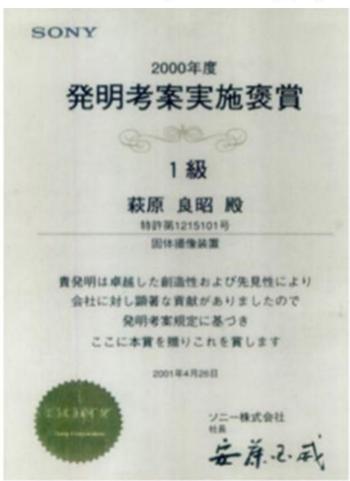

2000

Patent Award from Sony President Ando on the invention of Pinned Buried Photodiode (Hole Accumulation Diode) defined in JPA1975-134985 (Patent 12155101) by Hagiwara.

Albert J.P. Theuwissen, Jan T.J. Bosiers, Edwin Roks, "The Hole Role", an invited paper at IEDM2005, Washington DC, Techn. Dig., 2005.

But in the case that parts of the depleted n-type CCD channels are not covered by gate material, their surface potential is undefined ! Such a structure will suffer from charge transport issues during operation, because charge can be trapped in local potential pockets. The effect can be solved by defining the potential in the open areas through an extension of the p channel stopper. A simple self-aligned implant of 2x1013 /cm2 boron ions is sufficient to extend the channel stop areas to the gate edge and consequently fix the potential in the open areas [2]. The result after this self-aligned implant is shown in Figure 3. The presence of enough holes plays a crucial role in fixing the potential for the regions "beyond control" of the gates. (Is this structure the mother of the pinned-photodiode or buried diode or hole-accumulation device ?)

Figure 3. Cross section of a buried-channel CCD on n-Si substrate including light windows and pinned interface potential in the non-covered CCD channels (the cross section is made perpendicular to the CCD channel).

Y. Daimon-Hagiwara et.al., Proc. 10th Conf. on Solid-State Devices, Tokyo, 1978, pp.335-340.

### Fossum 2014 misleading paper invited the serioous misunderstandigs.

This Fossum 2014 paper did not quote Hagiwara 1975 patents completely and with a limited knowledge, made misleading and false comments not based on truth

### Indeed, Hagiwara invented PPD with VOD and the virtual charge transfer in 1975

Signific structures for CVDs in which a purp nortical structure.

true disclosed, attemp several witestams, (24). The mp y later

was connected by norsil to a bise need to countil hill-well.

appealty and the which have layer was proposed for carrier

storage. Its at amount paper, Hugways, in 1996, revisited the

HCS investive and claimed it was creentially the investion of

both the virtual plane CCD and the NEC low-lag intertures.

as well as the basis of the Sony severalised "Brite Accomplainess

Diods," or WAD concruer (2%) However, the 1975 profession

C. Otlan Cosmitations to the PPO bea

Sony HAD (PPD+VOD) does not use LOCOS A Review of the Pinned Photodiode for Not True

CCD and CMOS Image Sensors

Eric R. Franzer, Station 2022, and Domaid B. Honsbergers, Station Montes and

Doubtful? M are address complete charge mander, has or and blood properties found in the NEE low-lag driving, and does not Doubtful ?

were to comple for built in potential very and charge transfer The PMD vinution, while promed for low lights LLLD and plication, aluen a mong soundHipux to the Rymock virtualdenice aspects of the virtual-phase CCD. Biggivent, report phase CCD structure, with the exception of the VCE). The two Deve claims in a 2001 paper (20) and shows a VOO structure reconists were solving different profilence with executedly the that is not femal in the 1973 patent geologiese. Some did sate dries structure and operating principles. set uses to young the RAD structure until well after the So 1975. Blaghware at Some Word a journey application on

> NEC paper was published. However, the "turnow-pair" EXTO with an open a-type vortice orgion for improved QE also dischard in the 1975 application was reported in more detail. In Hagiwage et al. at Some in 1978 (27). A similar expector was used connected by Philips (20).

The PPG: as it is most contentedly used today, hears the attraged startellisms in the Tomacile of all \$27 CCD-Brise. The, there day Toyanta's considered as the primary stress

The surface P+ layer is NOT connected to the LOCOS P+ layer. The surface P+ layer may be floating and this photodiode may have serious image lag.

Hagiwara in 1975 invented PPD with VOD and the virtual charge transfer. Study the Japanese Patents 1975-127646, 1975-127647 and 1975-134985.

#### Difference between Buried Photodiode and Pinned Photodiode

What is the difference between Buried Photodiode and Pinned Photodiode? I understand that the P+/N/P structure where the P+ and P layers have the same potential is the Pinned Photodiode. So what is the buried Photodiode?

This is a commonly misunderstood misused set of terminologies.

First off these are not PIN Photodiodes - which stands for P - Intrinsic- N. These have large depletion regions for higher internal QE (Quantum Efficiency) and faster response. You can't make an array with this design though.

Pinning, refers to fermi-level pinning or pinning to a certain voltage level. Or also the forcing or prevention of the fermi-level/voltage from moving in energy space.

You can get surface state pinning from the dangling Si/SiO2 bonds providing trapping centers. A buried PD (Photodiode) has a shallow implant that forces the charge carriers away from these surface traps. The Si/SiO2 surface contributes to increased leakage (dark current) and noise (particularly 1/f noise from trapping/de-trapping). So confusingly a buried PD avoids pinning of the fermi-level at the surface.

A pinned PD is by necessity a buried PD, but not all buried PD's are pinned. The first Pinned PD was invented by Hagiwara at Sony and is used in ILT CCD PD's, these same PD's and the principles behind this complete transfer of charge are used in most CMOS imagers built today.

A pinned PD is designed to have the collection region deplete out when reset. AS the PD depletes it becomes disconnected from the readout circuit and if designed properly will drain all charge out of the collection region (accomplishing complete charge transfer). An interesting side effect is that the capacitance of the PD drops to effectively zero and therefore the KTC noise  $q_n = sqrt(KTC)$  also goes to zero. When you design the depletion of the PD to deplete at a certain voltage you are pinning that PD to that voltage. That is where the term comes from.

I've edited this Answer to acknowledge Hagiwara-san's contribution. It has long been incorrectly attributed to Teranishi and to Fossum (in CMOS image sensors)

### **Buried Photodiode**

Serious Image Lag Problem

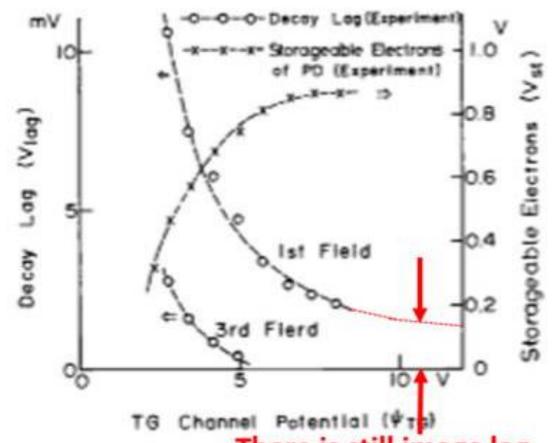

## **NEC IEDM1982 Paper**

Fig. 5. P\*NP- structure photodiode

(a) Unit cell cross sectional view

There is still image lag at the CTD gate voltage more than 10 volt.

Fig.6. Storageable electrons vs. transfer gate channel potential, and decay lag vs. transfer gate channel potential in the P\*NP\* structure photodiode

NEC analyzed in detail the relationship between the electric potential of the N layer of a photodiode in which the P layer was pinned to the substrate potential and the potential of the transfer gate to an external circuit.

NEC JPA 1980-1386026 出願特許は Pinned Photodiodeではない。

NEC analyzed in detail the relationship between the electric

potential of the N layer of a photodiode in which the P layer was pinned to the substrate potential and the potential of the transfer gate to an external circuit.

NEC JPA 1980-1386026 出願特許は Pinned Photodiodeではない。

特許請求の範囲

1. 第1等電型の干等体型板と、この型板である。 に形成され光の入射による信号電荷を蓄積する第 1 導電型と逆導電性の第2 導電型の蓄積領域と、 この蓄積減域に対応して設けられた信号電荷転送 手反こ、前記蓄積減域と前記信号電荷転送手数と の間に設けられ近記蓄積減域から助記信号電荷転送 送手段への信号電荷の転送を制御するトランスフ ァゲートとを有する固体液球装置の単位セルにおいて、前記蓄減額域の表面の全面に前記第1 導電型の表面層が設けられ、かつ前記蓄積領域が完全 に望乏化するのに必要な前記基板と前記蓄積領域 との間の逆バイアス電圧が30ボルト以下である ことを海たすように構成されてなることを特象と する固体域像装蔵。

# (4)Wrong?

In 1977, Toshiba proposed optimizing the impurity concentration and thickness of the charge storage N layer of the PN junction photodiode to completely deplete it in order to reduce image lag and improve light sensitivity [7].

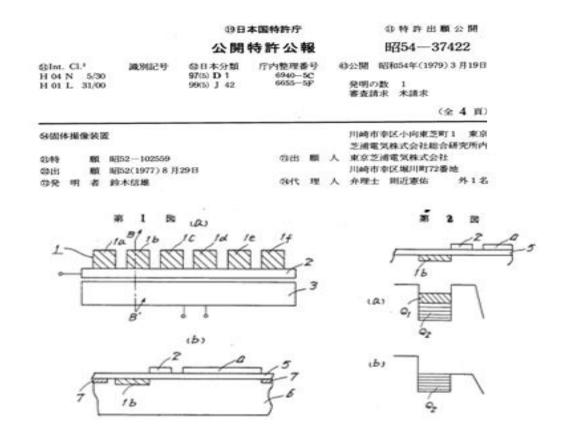

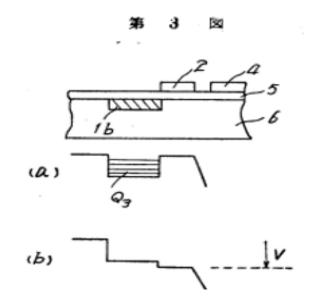

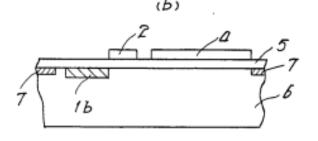

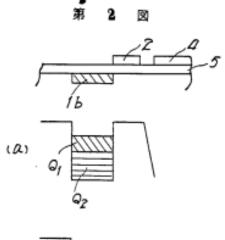

### JPA1977-102559

[7] N. Suzuki, Japanese Patent JP1977-102559

単純な受光面のN+層がFloatingの N+ P接合型の 受光素子の構造である。N+層の濃度を薄くする 事により完全電荷電荷転送できると誤解している。 残像が生じるので、Pinned Photodiodeでもない。

#### 19日本国特許庁

① 特許出願公開

#### 公開特許公報

昭54-37422

50Int. Cl.2 H 04 N 5/30 H 01 L 31/00 識別記号

録日本分類 97(5) **D** 1 99(5) J 42

庁内整理番号 6940-5C 6655-5F

昭和54年(1979)3月19日

発明の数 1 審査請求 未請求

(全 4 頁)

#### 69固体撮像装置

22出

川崎市幸区小向東芝町 1 芝浦電気株式会社総合研究所内

昭52-102559 20特

願 人 東京芝浦電気株式会社

昭52(1977) 8 月29日

川崎市幸区堀川町72番地

鈴木信雄

理 人 弁理士 則近憲佑

#### 外1名

# JPA1977-102559

[7] N. Suzuki, Japanese Patent JP1977-102559

単純な受光面のN+層がFloatingの N+ P接合型の 受光素子の構造である。N+層の濃度を薄くする 事により完全電荷電荷転送できると誤解している。 残像が生じるので、Pinned Photodiodeでもない。

### **Japanese Patent JPA 1977-837**

This patent is applied for the lateral overflow drain (LOD) function. The excess charge is drained to the N+ lateral output drain (LOD).

(D) Signal Output with Input Light showing No Image Lag Feature

Yoshiaki Hagiwara, Motoaki Abe and Chikara Okada, "A 380H x 488V CCD Imager with Narrow Channel Transfer Gates", Proceeding of 10<sup>th</sup> Conference on Solid State Devices, Tokyo 1978, Japanese Journal of Applied Physics, Volume 18 Sup 18-1, pp. 367-369.

Hitachi presented a structure in which the high-concentration surface P<sup>+</sup> layer is connected to a P-type substrate (well) and pinned it to the same potential as the substrate to increase the charge storage capacity and widen the dynamic range of the photodiode [4]. In 1978, Sony announced an FT (Frame Transfer) -CCD image sensor, using the photodiode with the same structure [5]. Sony succeeded for the first time in the world in prototyping a VTR-integrated color movie camera using a 2 / 3-inch 280,000-pixel FT-CCD image sensor that developed this technology, in 1981 [6].

(2) Wrong?

(3) Wrong?

### https://ieeexplore.ieee.org/document/9058907

### Multichip CMOS Image Sensor Structure for Flash Image Acquisition

Published in: 2019 International 3D Systems Integration Conference (3DIC)

### Yoshiaki Hagiwara

AIPS, Artificial Intelligent Partner Laboratory, Atsugi-city, Japan

#### Abstract:

A new 3D Pinned Photodiode (HAD) CMOS image sensor structure applied in the 3-Dimensional multichip high speed digital flash image data acquisition system is explained and the important features are discussed.

CONCLUSION

Hole Accumulation Diode<sup>6</sup> (HAD), with the P+ heavily doped surface hole accumulation layer, invented in 1975, is very important, because first of all it has the excellent short wave length blue light sensitivity feature producing the high picture quality of color reproduction in low level light illumination, which is realized by the photo electron and hole pair generation and separation in the built-in potential barrier<sup>1</sup> and the electric field at the surface heavily doped P+ hole accumulation HAD. No dark current is the second important feature. And no image lag is the third one since CCD was known to have the no image lag feature already. But CCD itself does NOT have the excellent blue light sensitivity and does NOT have the low dark current feature which the Pinned Photodiode<sup>1,2,6,10</sup> invented by Hagiwara has.

HAD is defined as the PNPN junction Photodiode with the VOD function. HAD is also by necessity the P+N-P junction Pinned Photodiode with no dark current feature. HAD is also by necessity the PN-P junction Depletion Photodiode defined as Buried Photodiode with no image lag feature. When Hagiwara invented HAD1,2,6,10 in 1975, Hagiwara also invented (1) Pinned Photodiode<sup>6</sup>, (2) Depletion Photodiode<sup>1</sup>, (3) Buried Photodiode<sup>10</sup>, (4) the inpixel vertical overflow drain<sup>6</sup> (VOD) function and (5) the in-pixel Global Shutter function1, 10. The surface pinned potential<sup>1, 6, 10</sup> also serves as the hole collector terminal separating the holes from photo electrons which drift more than the distance estimated by Debye length until being collected into the Buried10, Depletion1 and Pinned6 Photodiode (HAD), with the back light illumination scheme1 which is the most important feature needed to build the super sensitive 3D CMOS image sensor with the high blue-light quantum efficiency and the excellent color reproduction at low light level for fast action pictures with no image lag.

https://ieeexplore.ieee.org/document/9117803

# Simulation and Device Characterization of the P+PN+P Junction Type Pinned Photodiode and Schottky Barrier Photodiode Yoshiaki Hagiwara

AIPS Artificial Intelligent Partner Laboratory Atsugi-city, Japan

#### Abstract:

Process parameter tolerance of semiconductor device is very important for manufacturability and yield. Pinned Photodiode has by definition the pinned surface potential of the low surface dark current feature and the pinned empty potential well of the no image lag feature with the excellent blue light sensitivity of the ideal quantum efficiency. This paper reports simulation and device characterization of the unique P+PN+P junction type Buried, Depletion and Pinned Photodiode with excellent manufacturability, originally invented in 1975. Related various historical photodiode structures are reviewed, including the metal semiconductor Schottky Barrier photo sensor of Au/  $\beta$  - Ga  $_2$  O  $_3$  type in search for the low leakage and dark current photodiode which led the 1975 invention of the low leakage P+NPNsub junction Pinned Photodiode by Hagiwara.

Published in: 2020 4th IEEE Electron Devices Technology & Manufacturing Conference (EDTM)