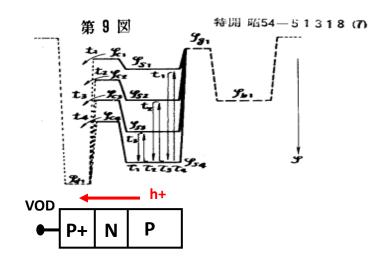

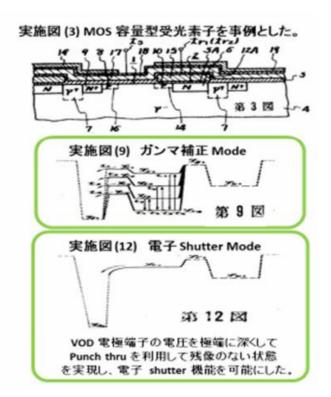

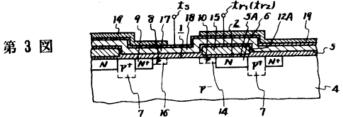

Fig. 3 of JPA1977-126885 on Gamma Function Controls

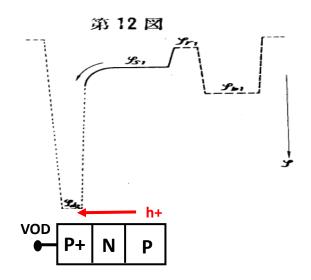

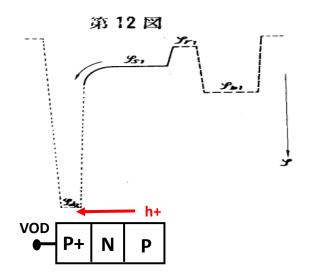

Fig. 12 of JPA1977-126885 on Electric Function Controls

#### Patent Claims of JPA1977-126885

特許的というでは、 を主いて、各のでは、 を主いて、各のでは、 を主いて、のでは、 を主いて、のでは、 を主いて、のでは、 を主いて、のでは、 を主いて、のでは、 を主いて、のでは、 を主いて、のでは、 を主いて、 を主いて、 を主いて、 のでは、 のでは

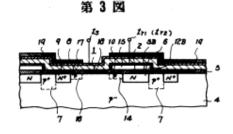

Fig. 3 of JPA1977-126885 on Electric Function Controls

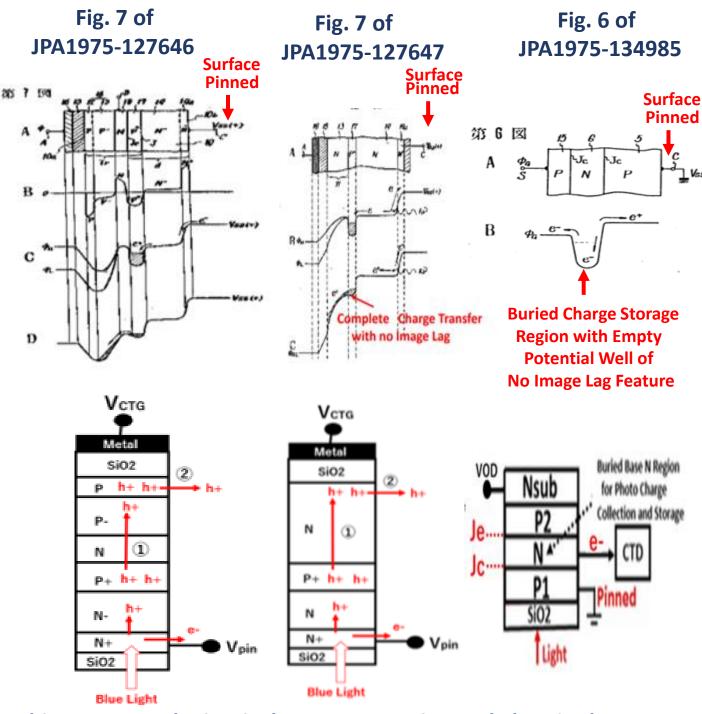

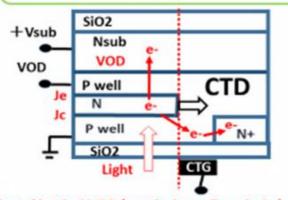

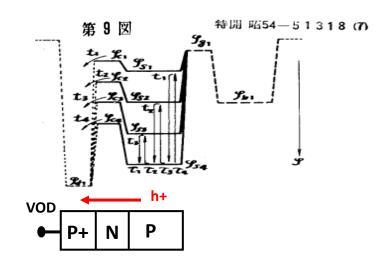

Fig. 3 of JPA1977-126885 shown above is an example of a photodiode with the lateral in-pixel P+ overflow drain (OFD) applied the Electric Function Control Scheme defined in this JPA1977-126885 patent which, however, can also be applicable in the P+NPNsub triple junction type Pinned Buried Photodiode with the vertical Nsub overflow drain (VOD) defined in JPA1975-134985 by Hagiwara in1975.

### **English Translation of Patent Claims of JPA1977-126885**

"In Interline-Transfer Image Sensors with an in-pixel overflow drain (VOD) structure, the same common (VOD) control voltage can be applied over the surface of the photodiode and also over the charge draining channel region by applying clock pulses externally on the overflow drain (OFD) so that the photo-charge storag-capacity can be controlled externally for realizing the Gamma Function and the Electric Function by punch-thru action of the OFD."

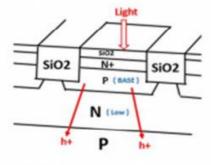

This patent can be applied for all of the image sensors now widely produced in the world including three Pinned Buried Photodiode Structures invented by Yoshiaki Hagiwara at Sony in 1975.

This patent on the in-pixel Gamma Function and Electric Shutter Clocking Schemes using the OFD punch-thru action is applied now in all of the image sensors produced widely all over the world.

Sony Central Research Center Lab Note Sketch by Yoshiaki Hagiwara on March 5, 1975 on the N+PNP triple junction type Pinned-Surface Buried-Storage Photodiode with the in-pixel Vertical OFD function for Gamma Control and Electric Shutter.

1975 年には既に N+PNP 接合型受光素子を考案し、かつこの受光素子には、 縦型 Overflow Drain (VOD) 機能を持つことを理解していた。電子 shutter 機能実現の為の重要は基板に過剰電荷を掃き出す手法を既に萩原は 1975年2月から使用のSONY中研 Lab Noteに記載している。

The N+PNP junction type Dynamic Photo Transistor Structure

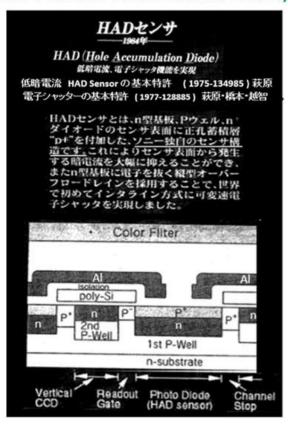

Pinned Photodiode and Sony Hole Accumulation Diode (HAD)

with the vertical overflow drain (VOD) function

invented by Hagiwara at Sony in 1975

Hagiwara's Lab Note at Sony in February 1975

In 1975 at Sony, Yoshiaki Hagiwara filed three Japanese patents JPA1975-127646, JPA1975-127647 and JPA1975-134985 on the Pinned Surface Photodiode with the VOD function which is later called as Sony Hole Accumulation Diode (HAD).

Hagiwara did not file a patent on the SiO2 device isolation but this lab note shows that Hagiwara had an idea of forming the Shallow Trench Isolation by the Local Oxidation Method, which was hinted by the LOCOS isolation in 1970s.

出願特許 1977-126885

| ! | 特許のタ   | 名称                  | 出願人     |              |  |            |            |

|---|--------|---------------------|---------|--------------|--|------------|------------|

|   | 固体撮像装置 |                     | ソニー株式会社 |              |  |            |            |

|   |        | 文献番号                |         | 出願番号         |  | 出願日        | 公知日        |

|   | 8      | <u>特開昭54-051318</u> |         | 特願昭52-126885 |  | 1977/09/29 | 1979/04/23 |

|   |        |                     |         |              |  |            |            |

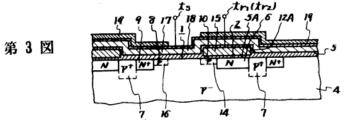

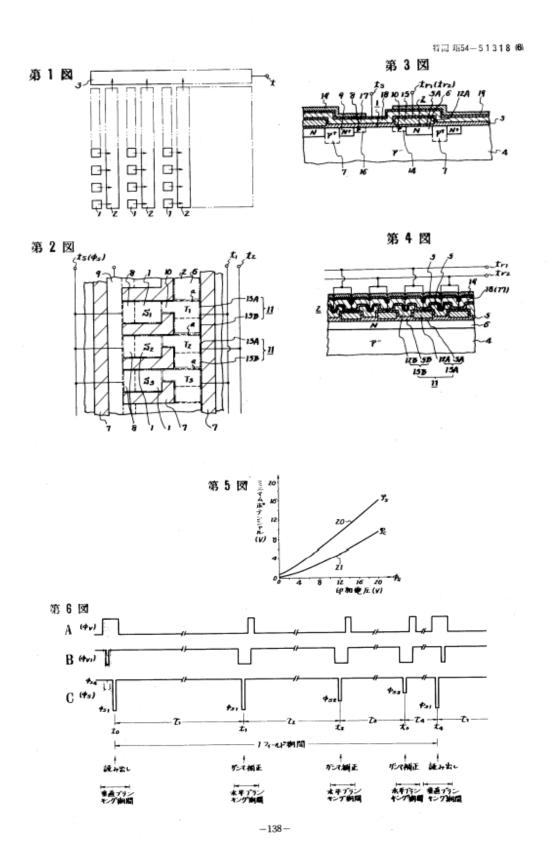

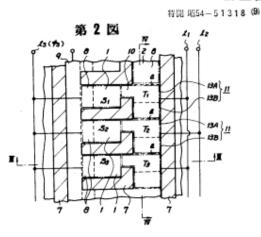

#### 図面の関準な説明

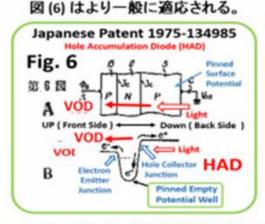

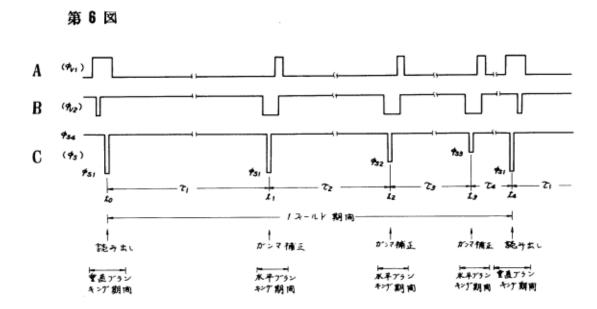

第1図は本発明の説明に供する固体操像装置の 構成図、第2図はその要部の拡大平面図、第3図 はそのA-A線上断面図、第4図は本発明装置の 一例の要部の拡大断面図、第5図は本発明装置の 他の例の要部の拡大断面図、第6図は本発明装置 の動作の説明図である。 電荷転送部 (CTD) が形成される面を主面と呼ぶ。図(6)は 受光面は主面側でも裏面側でも 特許請求範囲に入る。主面が シリコンウェハー上部でも下部 裏面でも特許請求範囲に入る。

図 は け トリー かに 次立 ナヤ

第4図は本発明装置の一例の要認の拡大新面図、 第5図は本発明装置の他の例の要認の拡大新面図、 第6図は本発明装置の動作の説明図である。

Fig. 6 shows that this is also the invention of in pixel VOD (vertical overflow drain).

Visit https://www.j-platpat.inpit.go.jp/ and type Japanese Patent Number 1975-134985

- ●完全に残像のない受光部のVOD機能を使って、電子 shutter 機能を実現するための Overflow Drain の電圧を従来は固定でしたが、それに Clock 電圧を印加することを 提案した、Overflow Drain 端子の Clock 駆動方式に関する特許です。

- ●実施例としては横型 OFD に適応しています。

- ●この特許は残像のない縦型 OFD(VOD)にも適応できる事は容易に類推できます。

- ●VOD付き Pinned Photodiode (Sony HAD)にも適応可能なことは容易に類推します。

- ●1987 年にSONY (浜崎チーム) は電子 Shutter 機能を持つ SONY HAD センサーを採用した ILT CCD Image Sensor の開発と商品化を実現しました。日経マクロデバイス 1987 年 10 月号参照。

- ●この出願特許 1977-126885 で提案された Clock 駆動方式を SONY の Hole Accumulation Diode (HAD) センサー (VOD 機能を持ち、残像のない、超光感度特性をもち、表面暗電流のない、P+NPNsub 接合型の 受光素子)を ILT CCD Image Sensor の採用したものです。

- ●これは「萩原が 1975 年に発明した P+NPNsub 接合型受光素子がVOD機能を持つこと」の証拠です。

#### The Pinned Photodiode (Sony Original HAD sensor) Structure

Electric Shutter Basic Patent Award from Sony President Idei to Yoshiaki Hagiwara for Japanese Patent 1977-128885 by Hagiwara

(from SONY Product Catalog)

(9日本国特許庁(JP)

00特許出願公開

⑩公開特許公報 (A)

昭54—51318

5DInt. Cl.<sup>2</sup>

H 04 N 5/30

H 04 N 5/20

識別記号 ⑫日本分類

97(5) **D** 1 97(5) A 42 庁内整理番号 ⑬公開 昭和54年(1979)4月23日

6940-5 C 6940-5 C

発明の数 1 審査請求 未請求

(全 10 頁)

⑤固体撮像装置

願 昭52-126885

②出 願 □

②特

額 昭52(1977)9月29日

70発 明 者 越智成之

町田市木曽町880-1 境川住

宅37-202

同 橋本武夫

町田市玉川学園 5 - 3 - 38

⑫発 明 者 萩原良昭

横浜市保土ケ谷区狩場町303の1

59 狩場台アパート402

⑪出 願 人 ソニー株式会社

東京都品川区北品川6丁目7番

35号

個代 理 人 弁理士 伊藤貞

男 組 書

発明の名称 固体操像装置

等許請求の範囲

発明の詳細な説明

本発明はCCD(チャージ・カブルド・デバイス)形構成を有する固体機像装置、特にインター

ライントランスファ方式による固体機像装置に係 わる。

通常のインターライントランスファ方式による CCD形固体摄像装置は、共通の半導体基体、例 まばシリコン基体に第1回に示すように、失々飲 **素となる受光部、即ちセンサー部(1)が一方向**(以 下水平方向という)とこれと重変する方向(以下 垂直方向という)に夫々複数盤配列され、各垂直 方向の同一ライン上に配列されたセンサー部(1)の — 倒には C C D 構成の垂直シフトレジスタ(2)が配 置され、各シフトレジスタ(2)の一端には同様に CCD 構成の水平シフトレジスタ(3)が設けられる。 そして、例えばテレビジョン映像においては、垂 直プランキング期間において、センサー部(1)の受 光量に応じて生じた信号電荷を対応する垂直シフ トレジスタ(2)に転送し、各水平プランキング期間 において、顧衣各垂直シフトレジスタ(2)の各水平 ラインの信号電荷を水平シフトレジスタ(3)に転送 し、各水平映像期間において出力端子はより順次 読み出すようになされる。との場合、各センサー

特別 昭54--51318 (4)

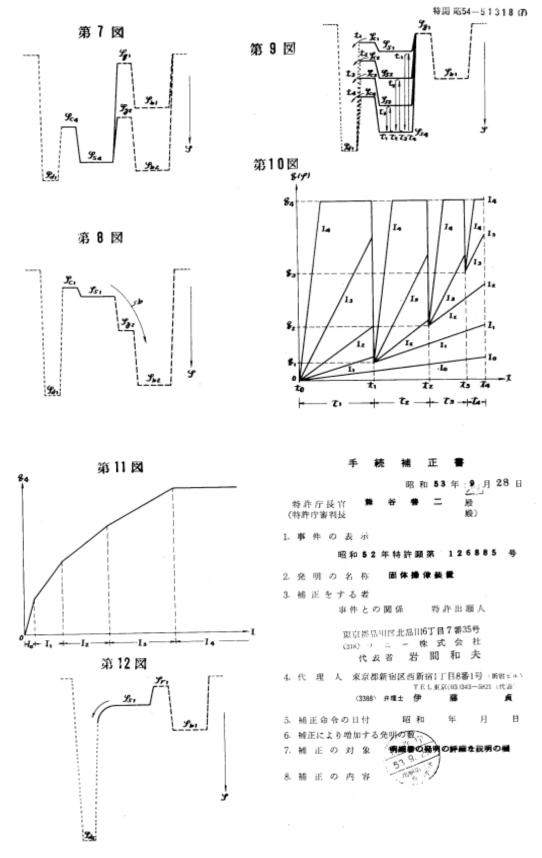

ンサー部(1)の受光量に応じた信号電荷を垂直シフ トレジスタ(2)の対応する転送部(1)に転送(以下競 み出しという。)し、シフトレジスタ(2)の端子 tra 及び tr2 に第6回人及びBに示すように、2相ク ロック øv1 及び øv2 を与えて水平プランキング期 間において、この信号電荷を順次集合り一方向の 転送部へと転送し、第1回に示した水平シフトレ ジスタ(3)へと1水平ライン毎の信号を転送し、水 平映像期間中で水平ライン毎の信号を端子はより 脱み出して行くものである。第7回ないし第9回 は、第3図に示す断面における各部のミニマムボ テンシャル図で、オーバーフロードレイン領域(9)、 オーパーフロー制御部(8)、センサー部(1)の各ミニ マムポテンシャルを pd、pc、ps、pg、pb で表わ し、各印加電圧状態におけるポテンシャルにサフ イックスを付して示したものである。第7回は受 光・蓄積モードを示し、この受光・蓄積状態では 増子 ts に、センサー部(1)に柔いポテンシャルの 井戸を形成する電圧、即ち正の大なる電圧はまを 与える。そして、奇数番目のフィールド期間の顕

初に対応する垂直ブランキング期間の時点は。で、 第 6 個 A 及び B に示すように、シフトレジスタ(2) の増子 tri 及び tr2 への印加電圧 fv1 及び fv2 と して正の所要の電圧を与えた状態で、端子は。に 与える電圧 og を第6回Cに示すように、低めて 第8回にそのミニマムポテンシャル図を示すよう に、センサー部(1)のポテンシャルの井戸を十分茂 くするポテンシャル pg1 とし、このセンサー部(I) に対応する転送部(1)のストレージ部におけるポテ ンシャルの井戸を十分探めるポテンシャルのh。に する。このようにすると、各センサー部 S1、S2、 83 ・・・・ に受光量に応じて発生蓄積されていた信 号電荷(キャリア)は、各転送部T<sub>1</sub>、T<sub>2</sub>、T<sub>3</sub>・・ ・・・・のストレージ部へと第8個に矢印りで示すよ りに転送、即ち読み出される。次に、との垂直ブ ランキング期間内において、第6図A及びBに示 すよりに、例えば囃子 tgの電圧 évgを上配正の 所要の電圧に保持した状態で、端子 t<sub>1</sub>の電圧 ≠<sub>v1</sub> を例えば0Vに低める。とのよりにすると、1つ 置きの転送部 T<sub>1</sub>、T<sub>3</sub>、T<sub>5</sub>・・・・・ の各電荷が、 他

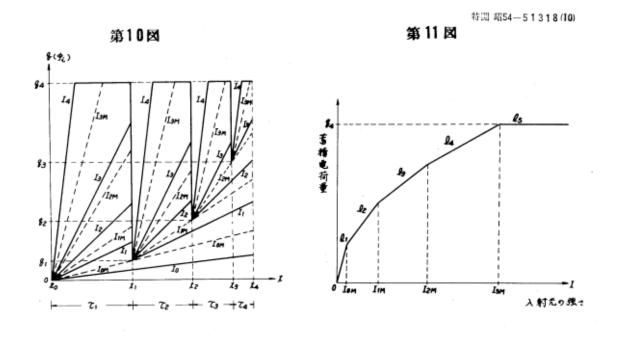

の1つ置きの転送部T2、T4、T6 ・・・・ へと転送さ れて2つの転送部の電荷が加えられる。即ち、セ ンサー部 S<sub>1</sub>、S<sub>3</sub>、S<sub>5</sub>・・・・ の各信号電荷が夫々襲 合うセンサー部 S2、S4、S6 ···· と重量される。 との電荷は垂直シフトレジスタへと垂直及び水平 ブランキング期間に知いて通常のように転送させ るが、特に本発明においては、適当な水平プラン キング期間において、ガンマ補正の操作を行う。 即ち、水平ブランキング期間の囃子 tri 及び tre への印加電圧が、共に例えば低い電圧のOVの状 類で、各転送部 T<sub>1</sub>、T<sub>2</sub>、T<sub>3</sub>・・・・と各センサー部 S1、S2、S3 ···· 間のゲート部のポテンシャルバ リア  $\varphi_g$  が第 9 図に  $\varphi_{g_1}$  として示すように比較的 高い状態で、水平プランキング期間内の各時点ti、 t2、t3・・・・で、端子tsに第6図Cで示すよう に帯次高い電圧 ∮<sub>81</sub> 、∮<sub>82</sub> 、∮<sub>83</sub> ···· を与え、第 9 図に示すように、センサー部 S1、S2、S3・・・・ のポテンシャル φ<sub>81</sub>、φ<sub>82</sub>、φ<sub>83</sub> ・・・・ を残くする と共に、オーパーフロー制御部(8)のポテンシャル を 9c1、9c2、9c3 とする。この場合、第5 図で説

明したように、印加電圧を高めるにつれ、センサー部とオーバーフロー制御部とのポテンシャルの整即ちポテンシャルバリアは低められるので、オーバーフローの量が増大する。したがつて今、光の態度 I が、 $I_0 < I_1 < I_2 < I_3 < I_4$  の関係を有する光を受光した場合の、時点  $t_0 \sim t_4$  におけるセンサー部(I) に書積される電荷量 q をみると、第10 図に示すように各時点  $t_1$ 、 $t_2$ 、 $t_3$ 、 $t_4$  での失々の $q_3$  一 $q_4$  はオーバーフローされて除去されるので、光の微度 I に対する電荷量は、第11 図に示すように指数関数曲線、即ちガンマ補正がなされる。

そして、次の偶数番目のフィールドにおいても、 同様の操作をすることによつてガンマ補正を行う ことができるが、この偶数番目のフィールドにお いては、第6図に示すように、その類初に対応す る垂直ブランキング期間における各センサー部 $S_1$ 、 $S_2$ 、 $S_3$  ···· からシフトレジスタ(2) の転送器 $T_1$ 、 $T_2$ 、 $T_3$  ···· への読み出し接前述の奇数番目のフィールドの場合とは逆に、端子 $t_1$  の電圧を正の

のミニマムポテンシャルが、常にゲート部において小さくなるように各部間側の不純物濃度或いは 絶縁層の厚さ等を選定するものとする。そして、 1 つ 置きの転送部間を共通に接続され、端子 t<sub>r1</sub> 及び t<sub>r2</sub> が導出される。

また、オーバーフロー制御部(8)は、例えば、基体(4)と同導電型を有するもこれに比し高い不純物 機度を有する領域値が主面(4a)に離んで形成され、これの上に絶縁層(5)を介して制奏電極師が被 着されて成る。

センサー部(I)は、光透過性の絶縁層(5)を介して これの上にセンサー電極時が被着されて構成され る。このセンサー電極時と、これに対応するオー パーフロー制御部(8)の制御電極切は、連続した共 通の透明電極によつて構成するか、電気的に接続 して共通の電圧を与える端子 t。が導出される。

尚、各額域(6)、(7)、(9)、04、66は、夫々周知の 技術、例えば選択的拡散法、イオン注入法等によ つて形成し得る。又、電板(5)(12A)及び(12B)は 夫々不純物がドープされて低抵抗ときれた多結晶 シリコン層を順次化学的気相成長法によつてデポ ジットすることによつて形成し得、これらの表面 を酸化することによつて絶級層を形成してこれら 電極(12A)及び(12B)上を含んで、全面的にセン サー電優階及びオーパーフロー制御電極(27を構成 する透明電極を全面的に被着して形成し得る。

特別 高54-51318 (3)

そして、センサー部(1)以外の部分上に、産光層 倒を被着する。この遅光層(1)は、例えばアルミニ ウム層によつて構成し得、このように進光層(1)を 導電体によつて構成する場合は、各電極を覆つて 絶録層(5)を形成し置き、これの上に進光層(9)を被 増せる

上述したように本発明装置においては、各センサー部(1)のセンサー電転幅と、之に対応するオーバーフロー制御部(8)の制御電極師とを電気的に共通の電圧が与えられた状態で、センサー部(1)とオーバーフロー制御部(8)とのミニマムボテンシャル(図示の例ではミニマムボテンシャルが表面に生ずるようにした場合で、との場合ミニマグボテンシャ

ルは表面ポテンシャルに相当する)に差が生する ようになすと共に、印加電圧によつてこのポテン シャルの差が変化するようになす。上述の例では センサー部(1)の表面機度を基体(4)の機度に選定し、 オーバーフロー制御部(8)の表面機度をセンサー部 (1)のそれより大にした場合で、この場合において、 センサー部(1)とオーバーフロー制御部(8)の各絶録 順(5)の厚さを 3000 Å とし、センサー部(1)の表面機 度を5×10<sup>14</sup> cm<sup>-3</sup> とし、制御部(8)のそれを5×10<sup>15</sup> cm<sup>-3</sup> としたときの、センサー電板GS及び制御電板 切への共通の印加電圧、即ち婚子 taへの印加電 圧 が、に対するセンサー部(1)と制御部(8)における 夫々の表面ポテンシャルφ。及びφc は夫々第5 図 中曲線御及び創に示すように、印加電圧が、が大 になるにつれ両者の差は大となる。尚、上述した 例では、センサー部(1)と制御部(8)の表面ポテンシ ヤルに差が生するように両者の表面表度を選定し た場合であるが、或る場合はセンサー部(1)と制御 部(8)との表面濃度は一定にして、或いはこれらを 異ならしめると共に、各部(1)及び(8)の電機(1)及び

断下の絶縁層の厚さを互に異ならしめ、センサー部における絶縁層の厚さを制御部(8)におけるそれより小に選定するようになすこともできる。このような構成としたことによつて、後に詳述するように、端子  $t_s$  への印加電圧  $t_s$  の大小によつて制御部(8)とセンサー部(1)の表面ポテンシャルの差( $t_s$  ー $t_s$  ののの水テンシャルの差( $t_s$  ー $t_s$  のの印加電圧  $t_s$  の大小によつて制御部(8)によるセンサー部(1)とオーバーフロードレイン領域( $t_s$  の との間のバリアの高さを変化させてセンサー部(1)よりのキャリアのオーバーフロー量を制御する。

尚、後の説明の便宜上、第2図に示すように名水平ライン上のセンサー部(1)を順次  $S_1$ 、 $S_2$ 、 $S_3$ ・・・・と、夫々に対応するシフトレジスタ(2)の転送部 00)を  $T_1$ 、 $T_2$ 、 $T_3$ ・・・・とし、1 つ世きの転送部  $T_1$ 、 $T_3$ 、 $T_5$ ・・・・の電極が端子  $t_1$ に、他の 1 つ産きの転送部  $T_2$ 、 $T_4$ 、 $T_6$ ・・・・・の電極が端子  $t_2$ に接続されるものとする。

次に、本発明装置の動作を説明するに、との場合においても循直プランキング期間において、セ

ンサー部(1)の受光量に応じた信号電荷を垂直シフ トレジスタ(2)の対応する転送部(1)に転送(以下競 み出しという。)し、シフトレジスタ(2)の端子 tn 及び tr2 に第6回 A 及び B に示すように、2相ク ロック øv1 及び øv2 を与えて水平ブランキング期 間において、との信号電荷を順次集合う一方向の 転送都へと転送し、第1回に示した水平シットレ ジスタ(3)へと1水平ライン毎の信号を転送し、水 平映像期間中で水平ライン毎の信号を端子はより 読み出して行くものである。第7回ないし第9回 は、第3図に示す断面における各部のミニマムポ テンシャル図で、オーバーフロードレイン領域(9)、 オーバーフロー制御部(8)、センサー部(1)の各ミニ マムポテンシャルを pd、pc、ps、pg、pb で扱わ し、各印加電圧状態におけるポテンシャルにサフ イックスを付して示したものである。第7回は受 光・蓄積モードを示し、この受光・蓄積状態では 端子 ts に、センサー部(1)に柔いポテンシャルの 井戸を形成する電圧、即ち正の大なる電圧は。を 与える。そして、奇数番目のフィールド期間の顕

初に対応する垂直ブランキング期間の時点toで、 第 6 因 A 及び B に示すように、シフトレジスタ(2) の端子 t<sub>r1</sub> 及び t<sub>r2</sub> への印加電圧 ≠<sub>v1</sub> 及び ≠<sub>v2</sub> と して正の所要の電圧を与えた状態で、端子t。に 与える電圧 ≠g を第 6 図 C に示すように、低めて 第8図にそのミニマムポテンシャル図を示すより に、センサー部(1)のポテンシャルの井戸を十分後 くするポテンシャル pg1 とし、このセンサー都(1) に対応する転送部(1)のストレージ部におけるポテ ンシャルの井戸を十分探めるポテンシャル Pho に する。とのようにすると、各センサー部81、82、 83 ・・・・ に受光量に応じて発生蓄積されていた信 号電荷( キャリア ) は、各転送部 T<sub>1</sub> 、T<sub>2</sub> 、T<sub>3</sub>・・ ・・・のストレージ部へと餌8個に矢印りで示すよ りに転送、即ち読み出される。次に、との垂直ブ ランキング期間内において、第6図A及びBに示 すよりに、例えば囃子 tgの電圧 évgを上配正の 所要の電圧に保持した状態で、端子 t<sub>t</sub>の電圧 ∮<sub>vt</sub> を例えば0Vに低める。とのようにすると、1つ 置きの転送部 T<sub>1</sub>、T<sub>3</sub>、T<sub>5</sub>・・・・・ の各電荷が、 他

特別 昭54-51318 (4)

の1つ量きの転送部 $T_2$ 、 $T_4$ 、 $T_6$ ・・・・ へと転送さ れて2つの転送部の電荷が加えられる。即ち、セ ンサー部 S<sub>1</sub>、S<sub>3</sub>、S<sub>5</sub>・・・・ の各信号電荷が夫 \* 隣 合うセンサー部 S2、S4、S6 ···· と重量される。 との電荷は垂直シフトレジスまへと垂直及び水平 プランキング期間において通常のよりに転送させ るが、毎に本発明においては、適当な水平プラン キング期間において、ガンマ補正の操作を行う。 即ち、水平ブランキング期間の増子 tri 及び tre への印加電圧が、共に例えば低い電圧のOVの状 繋で、各転送部 T₁、T₂、T₃・・・・ と各センサー部 S<sub>1</sub>、S<sub>2</sub>、S<sub>3</sub> ···· 関のゲート部のポテンシャルバ リアタ。が第9図にタ。日として示すように比較的 高い状態で、水平プランキング期間内の各時点 t<sub>1</sub>、 t2、t3····で、端子ts 化第6図Cで示すよう に漸次高い電圧 ∮<sub>51</sub> 、∮<sub>52</sub> 、∮<sub>53</sub> ···· を与え、第 9 図に示すように、センサー部 S1、S2、S3・・・・ のポテンシャル φ<sub>81</sub>、φ<sub>82</sub>、φ<sub>83</sub> ・・・・ を残くする と共に、オーバーフロー制御部(8)のポテンシャル を 9c1、9c2、9c3 とする。この場合、第5図で説

明したように、印加電圧を高めるにつれ、センサー部とオーバーフロー制御部とのポテンシャルの登か増大する。したがつて今、光の強度 I が、 $I_0$  <  $I_1$  <  $I_2$  <  $I_3$  <  $I_4$  の関係を有する光を受光した場合の、時点  $t_0$   $\sim$   $t_4$  におけるセンサー部(1)に蓄積される電荷量 q をみると、第 1 0 図に示すように各時点  $t_1$  、 $t_2$  、 $t_3$  、 $t_4$  での夫々の $q_3$  一 $q_4$  はオーバーフローされて除去されるので、光の策度 I に対する電荷量は、第 1 1 図に示すように指数関数曲線、即ちガンマ補正がなされる。

そして、次の偶数番目のフィールドにおいても、 同様の操作をすることによつてガンマ補正を行う ことができるが、この偶数番目のフィールドにお いては、第6回に示すように、その顕初に対応す る垂直プランキング期間における各センサー部 $S_1$ 、 $S_2$ 、 $S_3$  · · · · からシフトレジスタ(2)の転送部 $T_1$ 、  $T_2$ 、 $T_3$  · · · · への競み出し接前述の奇数番目のフィールドの場合とは遊に、端子 $t_1$  の電圧を正の

ロー制製部に電気的に独立の電極を設けることな くガンマ補正が行りことができるので電極構造が 複雑化することによる製造の煩雑さ、信頼性の低

特別 昭54-51318(5)

複雑化することによる製造の煩郁さ、信頼性の体 下、歩留りの低下等の招来を回避でき、実用に供 してその利益は大である。

としてセンサー部  $S_2$ 、 $S_3$ 、 $S_4$  ···· の電荷を、失々奇数フィールドにおける組合せとは異る他の関合うセンサー部  $S_1$ 、 $S_2$ 、 $S_3$  ···· と加え合せられるようにする。即ち、奇数フィールドにおいては $S_1$  と  $S_2$ 、 $S_3$  と  $S_4$ 、 $S_5$  と  $S_6$  ···· の組合せによつて失々1 つの数素信号を構成し、偶数フィールドにおいては他の組合せの  $S_2$  と  $S_3$ 、 $S_4$  と  $S_5$ 、 $S_6$  と  $S_7$  ···· の組合せによつて大々1 つの数素信号を形成する。

所定電圧に保持した状態で、端子 t<sub>2</sub>を例えば 0 V

また、上述の構成によるときは、各フィールドの類切において、全センサー部  $S_1$ 、 $S_2$ 、 $S_3$  ・・・・よりの電荷を読み出すので、残像の問題を解うつきる。即ち、従来のように各フィールドで1つ世をのセンサー部の電荷を読み出す場合は、各サーがなるというでは、また、変化のでは、では、ないなったがなったがなったがなったがなった。残像の問題が生ずるが、上述の本発明装置によれば、この問題が解析されま

このようにして2フィールドで1面面(1フレーム)を形成し、飛越し走査と同様の効果を得る。 尚、上述の構成において、感度調整を行うには、 オーパーフロー制御部(8)の幅を十分小となし置き、 第12図に示すようにオーパーフロードレイン 領 域(9)のパイアスを架めこれのポテンシャルが制御 部(8)に影響し、このパリアを低めてセンサー部(1) のキャリアを領域(9)へと透がしめるようにすると とによつて行い得る。

尚、上述の例においては、センサー電極を共通 として各フィールドで各センサー部の信号電荷を読 み出すようにした場合であるが、或る場合はセン サー電極を1つ置きの水平ライン上のセンサー部

上述したように、本発明によれば、オーバーフ

$S_1$ 、 $S_3$ 、 $S_5$  ···· 、  $S_2$ 、 $S_4$ 、 $S_6$  ···· を組として分割し、各フィールドで1つ置きのセンサー部に関して脱み出しを行うようにすることもできる。 図面の簡単な観明 パー領域、(8)はオーバーフロー制御部、(9)はオーパーフロードレイン領域、(0)はゲート部、(1)、 $T_1$ 、 $T_2$ 、 $T_3$  ···・はシフトレジスタ(2)の転送部、(13A)及び (13B) は転送電板、(9)はゲート電極、(7)はオーバーフロー制御電極、(8)はセンサー電極である。

代選人伊藤 貞

(1)、S<sub>1</sub>、S<sub>2</sub>、S<sub>3</sub>・・・・はセンサー部、(2)は垂直 シフトレジスタ、(3)は水平シフトレジスタ、(4)は 半導体基体、(5)は絶縁層、(7)はチャンネルストッ

特周 昭54-51318 (8)

- (1) 明細書中、第6頁3~4行「ストレージゲート部 (13A) とトランスファーゲート部」を「トランスファゲート部 (13A) とストレージゲート器」と訂正する。

- (2) 同、同頁6~7行「接続される。」の後に次の文を加入する。

「第4図の例では垂直シフトレジターのトランスフアゲート部とストレージゲート部にポテンシャルの深さを異らしめるため電極 (12A)(12B)下の絶縁層 (5A)(5B)の摩さを異らしめたものであるが、酸化腰厚差を用いずに半導体基体の不絶物渡度を用いてポテンシャルの深さを異らしめることもできる。この場合ストレージ電極(12B) およびトランスフア電極(12A)下の絶縁値(12A)の下にP型導電型の機い側線が形成される。このP型領域はたとえば選択的にイオン注入を行りことによつて形成できる。

(3) 同、同頁1 2 行「(5A)」を「(5B)」と訂正す

- (4) 同、第7頁2行「小さく」を「幾く」と訂正 する。

- (5) 同、第11頁13行「センサー部(1)の」を 「センサー部(1)、ゲート部00、ストレージゲート部(13B)の」と訂正する。

- (7) 同、同頁7行「進当な」の後に「回数の選ば れた」を加入する。

- (8) 同、同頁16行「を与え、」の前に「すなわ ち、 #s1 < #s2 < #s3 ・・・・・」を加入する。

- (9) 何、第14頁3行「低められる」を「高められる」と訂正する。

- (0) 同、同頁4行「増大する。したがつて今」を 次のように訂正する。

「減少する。この動作をたとえば I4 の 強 さ の 光が入射する場合について、 第 9 図、 第 1 0 図 を参照しながら詳細に説明する。すなわち I4 の強さの光が入射した場合、まず端子 t<sub>5</sub>に 4<sub>84</sub> が与えられた時のセンサー部のポテンシャル

**∮84 およびオーバーフロー制御部のポテンシヤ** ル Pc4 の差で挟められる電荷量 q4 以上の電 荷 はオーパーフロードレインへと枯てられ、セン サー部に蓄積される電荷量はq。で飽和する。 次に定められたある水平プランキング期間中の 一時点tiにおいて、端子tiには比較的低い電 位∮81 が与えられることによりセンサー窓のポ テンシャル +s1 とオーバーフロー制御部のポテ ンシャル éci で失まる蓄積量 q1 以上の電荷は オーバーフロードレインへと排除される。次い で端子tsに与えられる電位は再びチsaになされ るため入射光の強さIaにもとずいて再び電荷は センサー部のポテンシャル 🕬 とオーバーフロ - 制御部のポテンシャル差で決められたセンサ 一部に書積され、電荷量q。以上の余剰電荷は オーバーフロードレインに捨てられる。次に定 められた別の水平ブランキング期間中の一時点 toにおいて端子 ts に先きの fsi よりも高い電 位 482 が与えられることによりセンサー部のポ テンシャル 🗚 とオーパーフロー制御部のポテ

ンシャル・c2 とによって決められる書機量 q2 以上の電荷がオーパーフロードレインへと排除される。その後再び端子 ts には電位 fs4 が与えられて電荷は書積され第3の選ばれた水平プランキング期間中の一時点 t3 にて fs2 よりも高い電位 fs4 が与えられることにより蓄積量 q3 以上の電荷は排除される。その後再び端子 tsには電位 fs4 が与えられるため入射光に応じて電荷は蓄積された後、垂直プランキング期間中の一時点 t4 において統み出される。

したがつて今、」

- (1) 同、同頁9~10行「電荷q<sub>1</sub>~q<sub>4</sub>は」を 「電荷q<sub>1</sub>~q<sub>4</sub>以上の電荷は」と訂正する。

- 02 同、同頁12行「指数関数曲線、」を「べき 乗関数曲線、」と訂正する。

- (3) 同、同頁同行「なされる。」の後に次の文を 加入する。

「すなわち第10図および第11図において強さ IoM以下の光 Io が入射した時、センサーに 客様される電荷量は直線 81 で示され、 IoM と

補正図

Fig. 3 of JPA1977-126885 on Gamma Function Controls

Fig. 12 of JPA1977-126885 on Electric Function Controls

#### Patent Claims of JPA1977-126885

Fig. 3 of JPA1977-126885 on Electric Function Controls

Fig. 3 of JPA1977-126885 shown above is an example of a photodiode with the lateral in-pixel P+ overflow drain (OFD) applied the Electric Function Control Scheme defined in this JPA1977-126885 patent which, however, can also be applicable in the P+NPNsub triple junction type Pinned Buried Photodiode with the vertical Nsub overflow drain (VOD) defined in JPA1975-134985 by Hagiwara in1975.

### **English Translation of Patent Claims of JPA1977-126885**

"In Interline-Transfer Image Sensors with an in-pixel overflow drain (VOD) structure, the same common (VOD) control voltage can be applied over the surface of the photodiode and also over the charge draining channel region by applying clock pulses externally on the overflow drain (OFD) so that the photo-charge storag-capacity can be controlled externally for realizing the Gamma Function and the Electric Function by punch-thru action of the OFD."