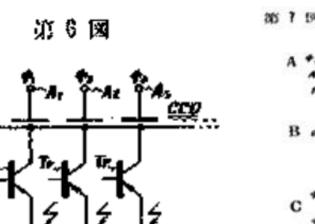

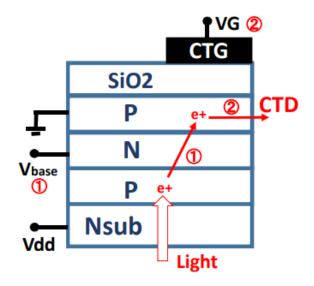

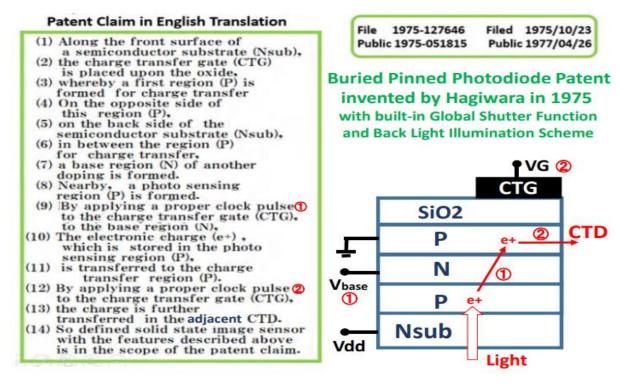

Fig. 6 of JPA1975-127646

Patent Claims of JPA1975-127646

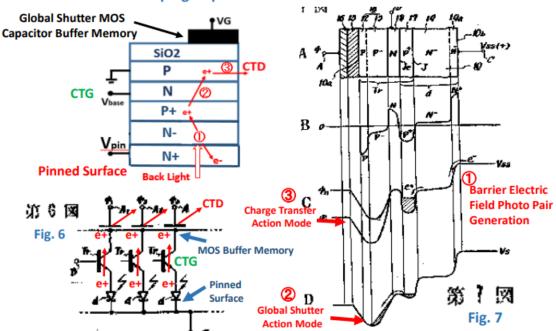

**Pinned Surface**

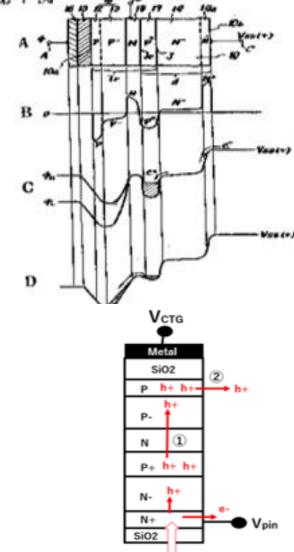

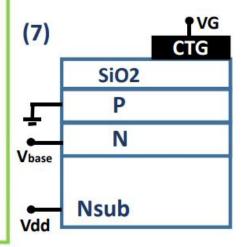

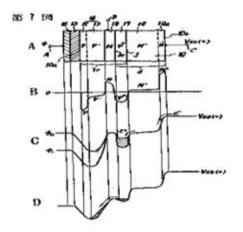

Fig. 7 of JPA1975-127646

Blue Light

# **English Translation of Patent Claims of JPA1975-127646**

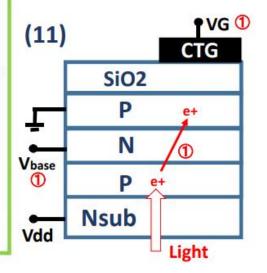

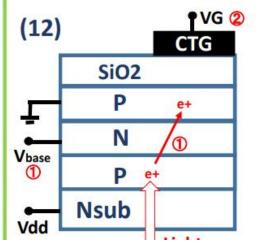

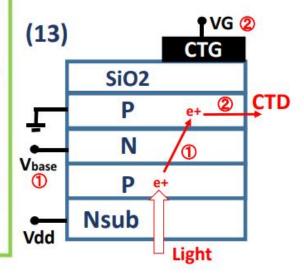

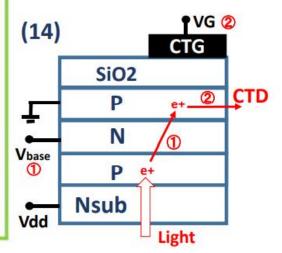

"An array of charge transfer gates is formed on the oxide layer of a semiconductor substrate (Nsub). The first charge transfer region (P1) is formed under the oxide layer. There is a base gating region (N) between the first region (P1) and the second photo charge collecting region (P2) which is formed in the substrate (Nsub). By proper gating clocks (1), the photo charge is drained to the surface region (P1) from the second region (P2) and subsequently transferred along the semiconductor surface by another proper clocks (2)."

# https://www.j-platpat.inpit.go.jp/

# Japanese Patent 1975-127646

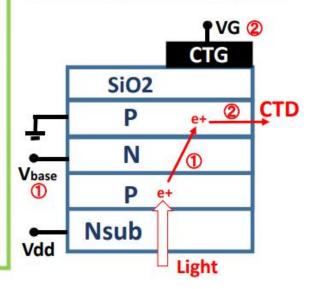

N+NP+NP junction Dynamic Photo Thyristor type Buried Pinned Photodiode with Built-in MOS Capacitor Buffer Memory Global Shutter Function and the surface N+N doping slope Barrier Electric Field Photo Pair Generation

## Japanese Patent 1975-127646

N+NP+NP junction type Buried Pinned Photodiode with Built-in MOS Capacitor Buffer Memory Global Shutter Function and the surface N+N doping slope Barrier Electric Field Photo Pair Generation

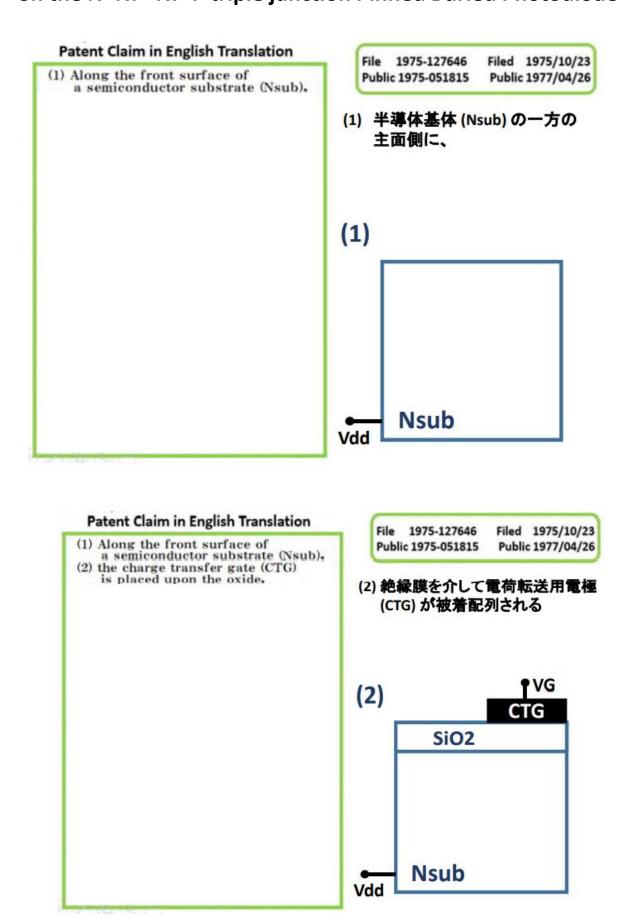

### Patent Claim in English Translation

(1) Along the front surface of a semiconductor substrate (Nsub).

(2) the charge transfer gate (CTG) is placed upon the oxide,

(3) whereby a first region (P) is formed for charge transfer

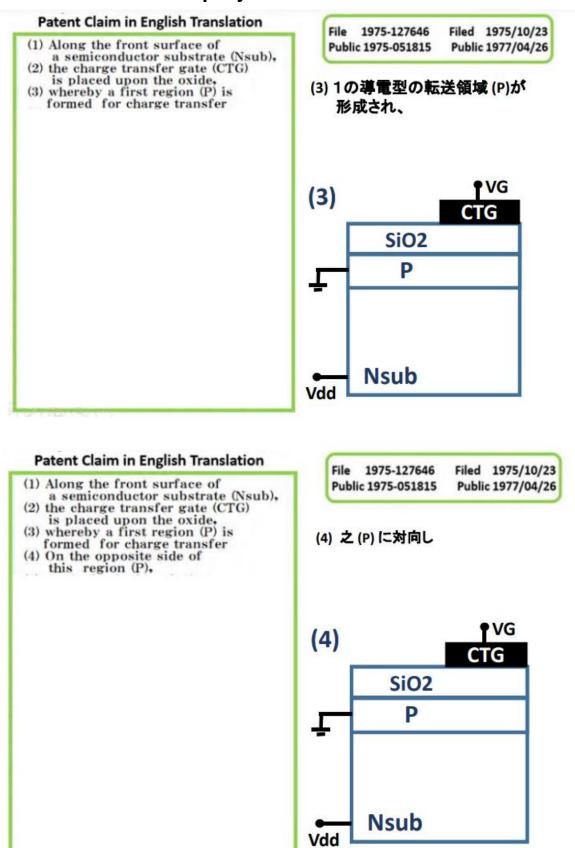

(4) On the opposite side of this region (P),

(5) on the back side of the semiconductor substrate (Nsub).

(6) in between the region (P) for charge transfer,

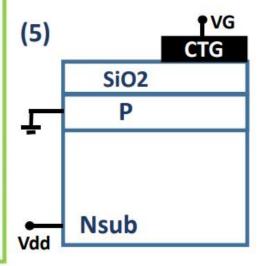

(7) a base region (N) of another doping is formed.

(8) Nearby, a photo sensing region (P) is formed.

(9) By applying a proper clock pulse to the charge transfer gate (CTG). to the base region (N),

(10) The electronic charge (e+), which is stored in the photo sensing region (P),

(11) is transferred to the charge

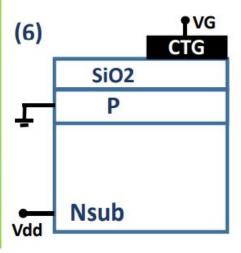

transfer region (P). (12) By applying a proper clock pulse 2 to the charge transfer gate (CTG),

(13) the charge is further transferred in the adjacent CTD.

(14) So defined solid state image sensor with the features described above is in the scope of the patent claim.

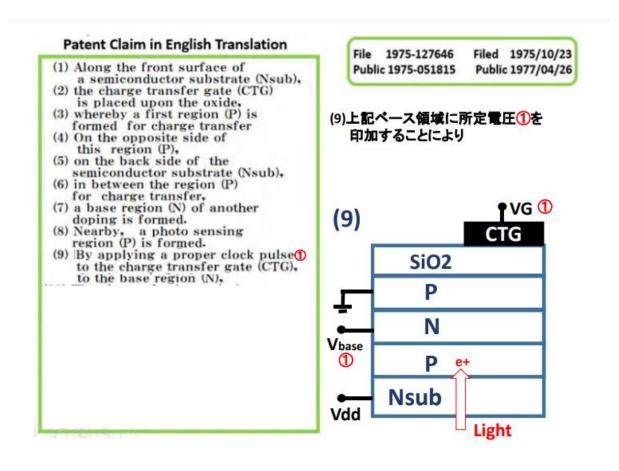

File 1975-127646 Filed 1975/10/23 Public 1975-051815 Public 1977/04/26

Buried Pinned Photodiode Patent invented by Hagiwara in 1975 with built-in Global Shutter Function and Back Light Illumination Scheme

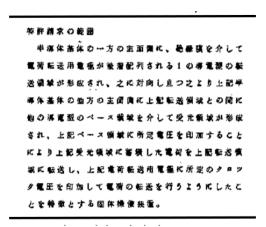

## 昭50-127646 特許の特許請求範囲の原文

- (1) 半導体基体 (Nsub) の一方の主面側に、

- (2) 絶縁膜を介して電荷転送用電極 (CTG) が被着配列される

- (3) 1の導電型の転送領域 (P) が形成され、

- (4) 之(P) に対向し

- (5) 且つ之より上記半導体基体 (Nsub) の 他方の主面側に

- (6) 上記転送領域 (P) との間に

- (7) 他の導電型のベース領域 (N) を介して

- (8) 受光領域 (P) が形成され、

- (9) 上記ベース領域に所定電圧①を 印加することにより

- (10) 上記受光領域に蓄積した電荷 (e+) を

- (11) 上記転送領域 (P) に転送し、

- (12) 上記電荷転送用電極(CTG) に指定の クロック電圧②を印加して

- (13) 電荷の転送を行うようにしたことを

- (14) 特徴とする固体撮像装置

File 1975-127646 Public 1975-051815 Filed 1975/10/23 Public 1977/04/26

Buried Pinned Photodiode Patent invented by Hagiwara in 1975 with built-in Global Shutter Function and Back Light Illumination Scheme

特 許 額(5)

图 和 6 0年 1.0月 2.3日

2 244070VD

1. 発明の名称 国体操像装備

> 要家部福川区北部川6丁目7 普35号 (215) ソニー株式会社 代表哲盛田昭夫

4.代 理 人 ● 160

性 時 東京都新存区高新宿1丁目8番1号 (明前ビル) 「 TRL開度 (53) 345~582( (代表)

表 43、(3389) 井瀬士 伊伊 英語

8、旅付参類の目跡

(1) 9 th 6 (2) R 5

(3) 類葉明末

1 通 1 选 1 通

50 127646 L

### ⑩ 日本国特許庁

# 公開特許公報

①特開昭 52-51815

❸公開日 昭52 (1977) 4.26

②特願昭 50-127646

②出願日 昭/ん(197√7/ん、23)

審査請求 朱雋求

(金6 頁)

庁内整理番号 69%の 59 6655 52

**図日本分類**

97001

**(1)** Int.C1: H04*N 5/30* H01L 31/00 織別記号

91 #41 =

発明の名称 四体操像装置

#### 整許請求の範囲

発明の詳細な説明:

本発明は、電荷転送素子CCDを用いた固体機 像装置に係わる。

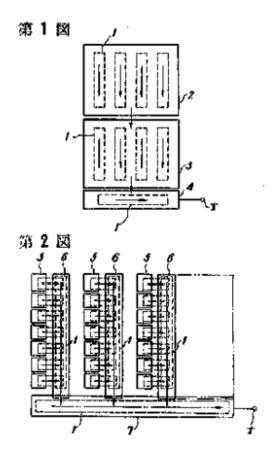

CCDを用いた個体操像装置としてはフレームトランスファ万式によるもの、取いなインメーライントランスファ方式によるものが喪楽されている。

フレームトランスフア方式による個体操像装置 表 1 倒に示す如く 馬像部(2)と、 書稿部(3)と、 水平シフトレシスカ(4)とから敗る。帰像部(2)は失 ▲ 転送電視を有する 転送部が倒えば垂鎖方向に配 羽され、1つ鱧を又は2つ間きの転送電極を組と して2相又は3相の転送クロック電圧が印加され て、各電極間又は各電優を通じて受光した光量だ 応じて各部に生じた電荷を倒えば垂直方向に混合 り転送部へとシフトして行くようにしたCCD(() が複数外配列されて成る。又、警務部[3]は、受先 はなされないようにするが機像筋(2)を構成する CCD(1)に対応するCCD(1)が設けられて成る。 をして、操像部間の各部に生じた操像光学像に伝 じた電荷パターンを、例えばテレビジョン映像に 於いては、その帰籍消去期間で、順及垂直方向に シフトさせて蓄積銀(3)へと仮送させ。この蓄積銀 (3)に一見意断パメーンを蓄積し、その後シフトレ シスク(4)に警機部(3)の各行の電視を順次転送助ち シフトし、シフトレジスタ(4の出力程子しよりこ の電荷による操像信号をとり出するのである。

一方、インターライントランスファ方式による操作機関は、第2個に示す如く失々数果となる複数の高秋受先部(5)が行及び列方向に配列され、各受先部(6)に第9合ので、共通の列上の受先部(6)に関し失々共通のCCD(1)より取る要覆シフトレジスタ(6)が配され、これらシフトレジスタ(6)の一端には共通の関係にCCD(1)より成る水平シフトレ

ジスタ(別が設けられ機像せんとする光学像に応じたバターンの電荷を受光部(別に得、この電荷を開合シフトレジスタ(例に帰継的安期間に於いて転送し、その後シフトレジスタ(例の多転送部に転送された電荷をシフトレジスタ(例に転送し、この電荷に応じた機像信号を出力端子1より解次得るものである。

$\frac{\partial \mathcal{G}}{\partial x}$

とのような表次による場合、帰業前去期間れ各受光部(同に対応して難合つて設けられたシフトシスタ(6)にその電新を転送するのみで何えば垂直方向へのシフトを必要としないので剪萃したフレームトランスファ方式による場合のように高いる版数のクロックを用いる必要がないという利息を有するが、この場合に近ても各受光部(6)とが進量配列されていることによって全体の面積が比較的大となるという欠点はある。

本発明は、このような欠点を解消した別体機像 装置を機供せんとするものである。

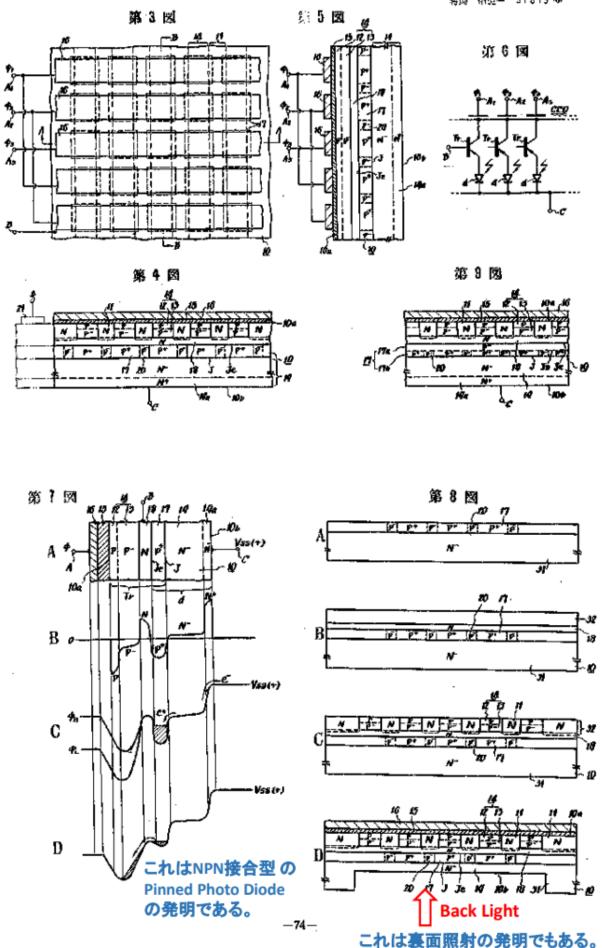

即ち、本発明に扱いては、 学導体整体の一主面 側に組込みテヤンネル形の C C D 構成を有する転

遊領線を形成し、他方の生態個はで先領域を形成し、絵葉となる貴光領域とこれに対応する転送領域との間に失 キトランジスタを介容させた構成となして之等のトラン ジスタのペースに所定の転送電圧を削加することによつ て受光領域に生じた機像せんとする光学像による電荷を 転送領域に移す。この受光領域から転送領域への電荷の 転送は直接的に行われるものであつて、前述したフレー ムトランスフリ方式による場合のような高い関放数の転 送タロックを必要とするものではない。

# 3 図ないし# 6 図を参照して、本発明による P ナヤンネル形の埋込みチヤンネル形のC C D 機 成を有する固体操像装置の一例を評論に説明する に、半導体兼体、例えばシリコン差体科を設ける。 この半導体基体(I)はその一定面(104) 角に切込み C C D が形成され、之に対向して之より他方の主 面(10b) 負に受光復減が形成される。

組込み C C D は、 整体(0 の 出面 (10 a) 例に面して形成された N 形のチャンネルストッパ 領域(6)によって区分されて夫々主面 (10 a) に沿つて一方向、例えば残方向(製造方向)に延長する荷なの P 形

の比較的高い不純物像度、例えば 2×i 0<sup>16</sup>/cx<sup>3</sup> の 単導体領域的と、2の下にこの領域的下の全域に 豆つて同様にP形を有するも領域に比しない不 総物機度、例えば 10<sup>15</sup>/cx<sup>3</sup> を有する P形の半導 体領域的とが形成され所要の関係を保持して形成 された複数の転送後域的が平行起列されて成る。 悪体傾の転送後域はが平行起列されて成る。 悪体傾の拡接され、この起数線的を介して各版 送機域は上に之等を送域はなる方向即ち行 方向(水平方向)に延長する転送電値が複数不 所要の関係を保持して形成される。

一方、受光領域は、各転送領域(個下に、部ち、 各転送領域(個上) 基体値の作方の主面 (10b) 別に、 芸い後えれば、基体値の厚さ方向側に、各転送領域(個との交叉部に対向して失き最 状がPをの電荷装徴(は個がN形のペース領域と なる半導体循環を介して形成され、更に各領域(間 と新して基体値の主面 (10b) 関にN形の共通の半 は解値の半導体循環を介して形成され、更に各領域(間 と新して基体値の主面 (10b) 関にN形の共通の半 は解値の半導体循環を介して形成され、 を新して基体値の主面 (10b) 関にN形の共通の半 は解値の非常成されるとうになす。電荷書系領 報信は例えば10<sup>35</sup>/cm<sup>3</sup> オーダーの高い不純物競優に悪定される。又、N影の半導体署(9位、その報味所と様する部分は比較的吸い不純物競及例えば10<sup>15</sup>/cm<sup>3</sup> オーダーの半導体署より構成するも、必要に応じて主通(10b) 側の製液にN形の高度度例えば10<sup>16</sup>/cm<sup>3</sup> オーダーの高級関層(19a)を形成し得る。又、各電荷署機関域傾間関与各転送領域し得る。又、各電荷署機関域傾間関与各転送領域制能に対向する部分とに将手状に署積領域領と同消電形を有するも、領域的に比し十分扱い不納物設度、例えば10<sup>15</sup>/cm<sup>5</sup> のオーダーのP形の電荷の潜機を回避する領域側を形成する。

チャンネルストッパー個数印とペース領域となる半導体を移往互に連載するようになす。又、ペース領域関より之に所定の電圧を用加するための 囃子Bを導出する。これがため例えば第4個に示す如くテャンネルストッパー仮域側上に電極側を オーミックに被害し、漢子Bを導出する。

又、 総合う 2 つ 置きの 報送 電機 暗を 相互に 接続 して之等 3 組の 電気値の共通の 弾子 A1、A2、A3 に 3 相のクロックが1、が2、が4 を印加するようになす。 そして、参体的の裏面(10b) ほより受光するようになす。

このような構成による関体操像装置は、基体側の一方の質(16a)関に失る伝送領域側に関し、共通の振送電影の振送電影の振送電影の振送電影の振送を介して見れる。そして、各CCDに関し握る図にその観送される。そして、各CCDの、その転送者を収録を介して、各の非過なを開発を表現して、大人の関係を表現して、大人の関係を表して、大人の関係をより成るフォトディオードすが、大人の関係をより、大人を関係は、大人を関係をより、大人を関係に対して、大人の大力を表して、大人の大力を表して、大人の大力を表して、大人の大力を表して、大人の大力を表して、大人の大力を表して、大人の大力を表して、大人の大力を表して、大人の大力を表して、大人の大力を表現された。

このような構成による本発明装置に換て、フォトダイオード d の共通のカソード即ち半導体滑削の降子 C には、正の固定電位 Vas 例えば接地電位 を年えてフォトダイオード d に 遊 パイアスを与え

٥.

便に、本発明無常の動作を影り図を整照して観明すると、終り図Aに示す楽る図中AーA様の断断に対応する不概能機関の分布は集了図Bに示す如くなる。今、この断面に於ての受光状態則ち

次にこの状態から様子Bに食の色位を与えて操 分J c に独立イアスを与える。この時、電機Mで はクロック電位に比し十分低い電位レベル、即ち 負の十分大なる電圧を与える。かくすると、傾望 師に蓄積されていた電荷、即ちホールは、乗7回 D に示す知くC C D の転送情報がへと転送される。 そして、この状態から再び終7回じの状態とさ れての状態で受光がなされると共に、象子図Dで 説明した転送領域に転送された電荷は電極船に与 えられるクロックによる胃圧<sub>列車</sub>〜列」によって説 子図に於いて紙面と変交する方向に通常の<mark>埋込み</mark> チャンネル形のCCDに於けると同様に転送され ていく。

との場合、転送領域時に於て之に信号電視が到来しても常に之が恋乏化されているように、文元の運動が基体表面(10a)に確することがないように無数傾の表面には高速度低級的が配され、且つ、ベース領域傾の不納物機関はその多数やキリア量が無破がを構成する両面域的及び時に持つ多数やキリアの量に対応するように比較的高く過せれる。

上述したように本ி明芸世によれば、参外間の 裏面 (10b) 関から受光をなし、表面 (10s) 跳の C C D で駆送するようになすもので、受光部と転 送部とは著体調の無み方向に云わば立体的に構成 されるので、全体の面積の筋少化をはかることが でき、ひいては受光部の面積の増大化がはかれる

電荷書機保護師を行及び列方向に所義の間隔を保持して配列すると非に、各領域師問の会域に、始わ各領域師と接し、且つ之等をとり語むように格子状に、強城師と同連電形を有するもこの領域師に比し十分銀い不統物経度例えば10<sup>15/cm<sup>5</sup></sup>の銀城師をイオン注入法、並いは拡散法によつて選択的に領域師と同程度の確さに形成する。

次に、更に本発明装置の理解を移場にするため に、第8回を参照して上述した本発明装置を得る 製法の一例をその工機順に説明しよう。

先ず、第8 器Aに示す如く例えばほさが 150 ~ 300 Am の、不動物機関が向 18 35 / cm 3 の N 形のシリコンサプストレイト側を根象し、その一方の 面に約 2 Am の保さを以つて P 形の不純物を夫々イ オン注入、吸いは拡散法によつて 選択的に ドープ して不純物機関が 10 26 / cm 3 程度の複数の 島状の

体層観をそのエピタキシヤル競長に楽してN形の不動物をドープして形成することもできる。次いで、この 簡優上に十分低い不適物の半導体例えば シリコン層間を 2 ~ 4 pm の厚さにエピタキシヤル 競技して着体態を構改する。

サブストレイト師をその裏面よりその周辺部を残して中央部の動作領域部分をエッテンクしてその 理みを10~15 Am とし、この様い部分のサブストレイト側によつて前述したダイオードもの共通 のカソード領域のち各電前等被領域間との間に PN 整合 J を形成するN 形の半導体層的を形成する。このように現辺部の学みは大にし、動作部の みの即さを小とするときは、全体の機械的強度を 保持しつン受光効率を高めることができる。

親の節は本発明装置の他の例を示すもので、この図に於いて据る図ないし集の図と対応する部分には同一符号を付して直接説明を省略するが、この例ではトランジスタTcのエミンタ振波初にし、円接合Jsを影成すべくそのベース機製機の名は環境域(17b)を形成し、之とは反対機に高級皮領域(17b)を形成した場合Js即ちエミンタ領域値に於ける少数キャリアに対するボテンシャルパリアを形成するときは、ベース領域値がたエミンタ領域値に発力をおたキャリアがこのボテン

シャルバリアによって押し戻されることによって との商級師に於ける少数キャリアの拡散電流を小 とするととができ、このトランジスタTr の電流 増市率の向上をはかることができることになる。

尚、上述した本勢明整度の各例に於て、そのサ ブストンイト側面を半導体基体傾の半導体層側の 表面に高不規制度度(19 m)を設けるときは、表面 再級合の防止を行うことができる利益がある。文、 原示しないが基体傾の面(10b)側に 8iO2 番のようにその配析率が基体値と空気との中間の値を有 する要を被着することによってこの表面の反射的 止を行って受光効率の向上をはかることができる。

又、よぶした各例に於て端子でに我の電値を与えることによつて領域値の等機関所を適当最清敵 させ先量調整を行うようにすることもできる。

間、上述した各例はP形の想込みテヤンネル形CCD構成とした場合であるが、N形の組込みテヤンネル形CCDに本発明を適用して同様の効果を得ることができることは明らかであり、この場合に於ては各陸に於ける各部の準電形と電圧の極

性とを反転させれば良い。

#### 図面の領単な説明

男1 図及び写2 図は従来の樹年掃像装置の構成図、第3 即は本発明表徴の一例の要部の拡大上面図、第4 図及び第5 樹はそのA ーA 梯上及びB ーB 線上の拡大断面図、現6 図はその等価監路の、現7 図はその観光図、現9 図は本発明集置の製法の一例の工程図、乗9 図は本発明表覚の他の例の要罪の新面図である。

10 位半導体基体、(10x)及び(10b) はその両支面、別は転送額状、12はその高不純物美度領域、(1)はその数不純物無度領域、(1)はその数不純物無度領域、(1)はペース領域となる半導体等、前はエミック領域となる電荷等機領域、同は半導体等、優は転送電気、明は絶象鍵である。

春許部顧人 ソニー株式会社 代 理 人 伊 毎 (典)

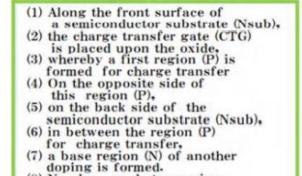

### Patent Claim in English Translation

- (1) Along the front surface of a semiconductor substrate (Nsub),

- (2) the charge transfer gate (CTG) is placed upon the oxide,

- (3) whereby a first region (P) is formed for charge transfer

- (4) On the opposite side of this region (P),

- (5) on the back side of the semiconductor substrate (Nsub).

Filed 1975/10/23 1975-127646 Public 1975-051815 Public 1977/04/26

(5) 且つ之より上記半導体基体 (Nsub) の 他方の主面側に

#### Patent Claim in English Translation

- (1) Along the front surface of a semiconductor substrate (Nsub), (2) the charge transfer gate (CTG)

- is placed upon the oxide.

- (3) whereby a first region (P) is formed for charge transfer

- (4) On the opposite side of this region (P),

- (5) on the back side of the semiconductor substrate (Nsub),

- (6) in between the region (P) for charge transfer,

File 1975-127646 Filed 1975/10/23 Public 1975-051815 Public 1977/04/26

(6) 上記転送領域 (P) との間に

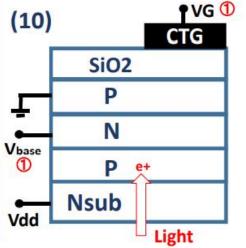

## Patent Claim in English Translation

- (1) Along the front surface of a semiconductor substrate (Nsub),

- (2) the charge transfer gate (CTG) is placed upon the oxide,

- (3) whereby a first region (P) is formed for charge transfer

- (4) On the opposite side of this region (P),

- (5) on the back side of the semiconductor substrate (Nsub),

- (6) in between the region (P) for charge transfer, (7) a base region (N) of another

- doping is formed.

File 1975-127646 Filed 1975/10/23 Public 1975-051815 Public 1977/04/26

(7) 他の導電型のペース領域 (N) を介して

#### Patent Claim in English Translation

- (1) Along the front surface of a semiconductor substrate (Nsub).

- (2) the charge transfer gate (CTG) is placed upon the oxide,

- (3) whereby a first region (P) is formed for charge transfer

- (4) On the opposite side of this region (P),

- (5) on the back side of the semiconductor substrate (Nsub).

- (6) in between the region (P)

- for charge transfer, (7) a base region (N) of another doping is formed.

- a photo sensing (8) Nearby, region (P) is formed.

File 1975-127646 Filed 1975/10/23 Public 1977/04/26 Public 1975-051815

(8) 受光領域 (P) が形成され、

Patent Claim in English Translation

(8) Nearby, a photo sensing region (P) is formed.

(9) By applying a proper clock pulse to the charge transfer gate (CTG), to the base region (N),

(10) The electronic charge (e+), which is stored in the photo sensing region (P), File 1975-127646 Filed 1975/10/23 Public 1975-051815 Public 1977/04/26

(10) 上記受光領域に蓄積した電荷 (e+)を

### **Patent Claim in English Translation**

- (1) Along the front surface of a semiconductor substrate (Nsub). (2) the charge transfer gate (CTG)

- is placed upon the oxide.

(3) whereby a first region (P) is formed for charge transfer

- (4) On the opposite side of this region (P),

- (5) on the back side of the semiconductor substrate (Nsub),

- (6) in between the region (P) for charge transfer,

- (7) a base region (N) of another doping is formed.

- (8) Nearby, a photo sensing region (P) is formed.

- (9) By applying a proper clock pulse to the charge transfer gate (CTG), to the base region (N),

- (10) The electronic charge (e+), which is stored in the photo sensing region (P),

- (11) is transferred to the charge transfer region (P).

1975-127646 Filed 1975/10/23 Public 1975-051815 Public 1977/04/26

(11) 上記転送領域 (P) に転送し、

#### Patent Claim in English Translation

- (1) Along the front surface of a semiconductor substrate (Nsub).

- (2) the charge transfer gate (CTG)

- is placed upon the oxide.

(3) whereby a first region (P) is formed for charge transfer

- (4) On the opposite side of this region (P),

- (5) on the back side of the semiconductor substrate (Nsub),

- (6) in between the region (P)

- for charge transfer, (7) a base region (N) of another doping is formed.

- (8) Nearby, a photo sensing region (P) is formed.

- (9) By applying a proper clock pulse(1) to the charge transfer gate (CTG),

- to the base region (N). (10) The electronic charge (e+) . which is stored in the photo

- sensing region (P), (11) is transferred to the charge transfer region (P).

- (12) By applying a proper clock pulse 2 to the charge transfer gate (CTG),

File 1975-127646 Filed 1975/10/23 Public 1975-051815 Public 1977/04/26

(12) 上記電荷転送用電極(CTG) に指定の クロック電圧 ②を印加して

#### Patent Claim in English Translation

- (1) Along the front surface of a semiconductor substrate (Nsub),

- (2) the charge transfer gate (CTG)

- is placed upon the oxide.

(3) whereby a first region (P) is formed for charge transfer

- (4) On the opposite side of this region (P),

- (5) on the back side of the semiconductor substrate (Nsub),

- (6) in between the region (P)

- for charge transfer, (7) a base region (N) of another doping is formed.

- (8) Nearby, a photo ser region (P) is formed. a photo sensing

- (9) By applying a proper clock pulse 1 to the charge transfer gate (CTG). to the base region (N)

- (10) The electronic charge (e+) , which is stored in the photo sensing region (P),

- (11) is transferred to the charge transfer region (P).

- (12) By applying a proper clock pulse 2 to the charge transfer gate (CTG),

- (13) the charge is further transferred in the adjacent CTD.

1975-127646 Filed 1975/10/23 Public 1975-051815 Public 1977/04/26

## (13) 電荷の転送を行うようにしたことを

#### Patent Claim in English Translation

- (1) Along the front surface of a semiconductor substrate (Nsub),

- (2) the charge transfer gate (CTG) is placed upon the oxide.

- (3) whereby a first region (P) is formed for charge transfer

- (4) On the opposite side of this region (P),

- (5) on the back side of the semiconductor substrate (Nsub),

- (6) in between the region (P)

- for charge transfer, (7) a base region (N) of another

- doping is formed. (8) Nearby, a photo sensing region (P) is formed.

- (9) By applying a proper clock pulse(1) to the charge transfer gate (CTG). to the base region (N),

- (10) The electronic charge (e+) which is stored in the photo sensing region (P),

- (11) is transferred to the charge transfer region (P).

- (12) By applying a proper clock pulse 2 to the charge transfer gate (CTG),

- (13) the charge is further

- transferred in the adjacent CTD. (14) So defined solid state image sensor with the features described above is in the scope of the patent claim.

1975-127646 Filed 1975/10/23 Public 1975-051815 Public 1977/04/26

## (14) 特徴とする固体撮像装置。

## Patent Claims of JPA1975-127646

Fig. 7 of JPA1975-127646

## **English Translation of Patent Claims of JPA1975-127646**

"An array of charge transfer gates is formed on the oxide layer of a semiconductor substrate (Nsub). The first charge transfer region (P1) is formed under the oxide layer. There is a base gating region (N) between the first region (P1) and the second photo charge collecting region (P2) which is formed in the substrate (Nsub). By proper gating clocks (1), the photo charge is drained to the surface region (P1) from the second region (P2) and subsequently transferred along the semiconductor surface by another proper clocks (2)."