## **Image Sensor Story**

Yoshiaki Hagiwara AIPS

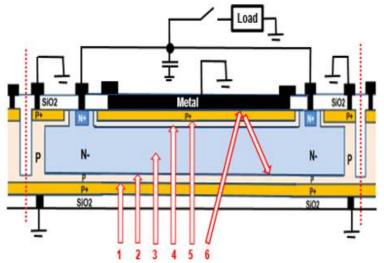

**Back-illuminated CIS**

**Back-illuminated CIS**

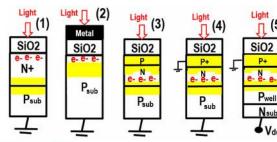

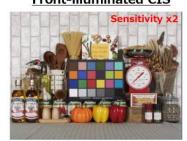

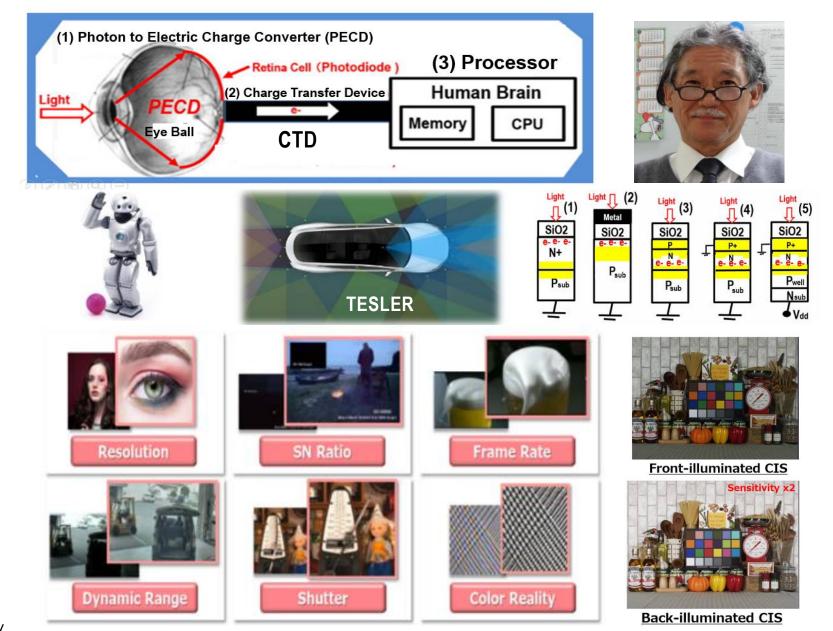

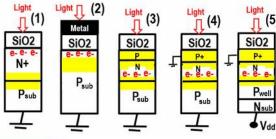

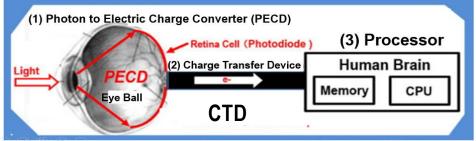

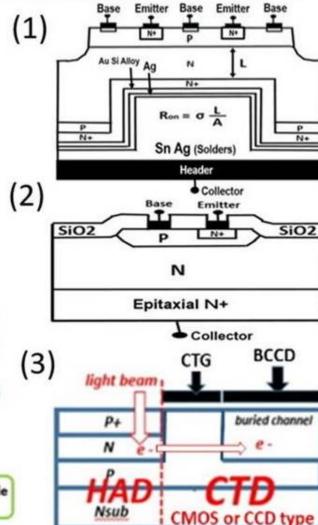

(1) Photon to Electric Charge Converter (PECD)

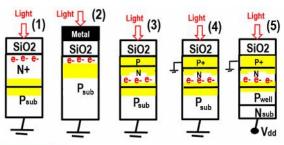

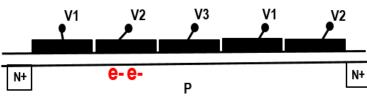

N+P single junction P+NP double junction P+NPN triple junction

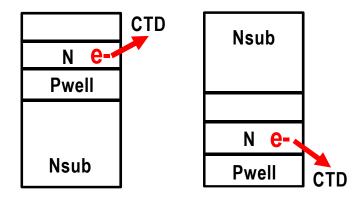

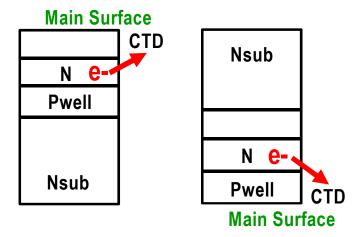

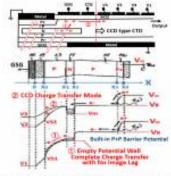

(2) Charge Transfer Device (CTD)

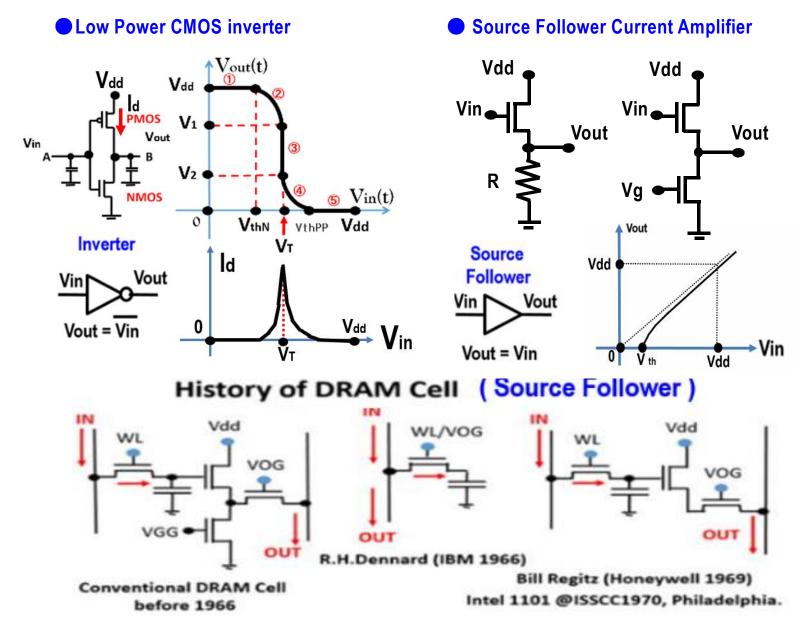

●MOS type ●CCD type ●Active Pixel (In Pixel Current Amp + CDS + ADC ) CMOS

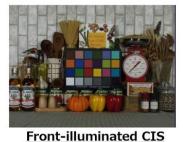

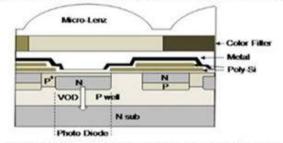

Front-illuminated CIS

**Back-illuminated CIS**

d

Analog TV  $800H \times 500 V = 400,000 pixels$

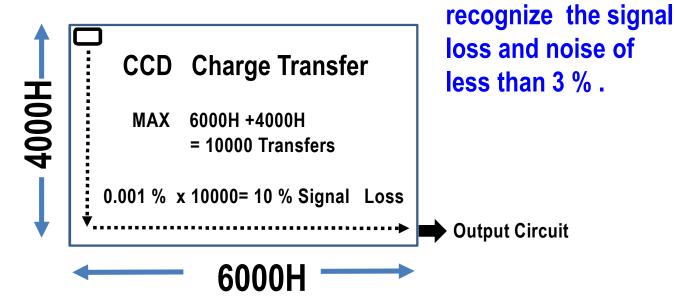

**CCD** Charge Transfer Efficiency < 99.999%

recognize the signal **CCD** Charge Transfer 500H MAX 800H +500H = 1300 Transfers 0.001 % x 1300= 1.3% Signal Loss **Output Circuit** 800H

loss and noise of less than 3 %.

**Human Eyes cannot**

**Digital TV**6000H x 4000 V = 24,000,000 pixels

**Human Eyes cannot**

**CCD** Charge Transfer Efficiency < 99.999%

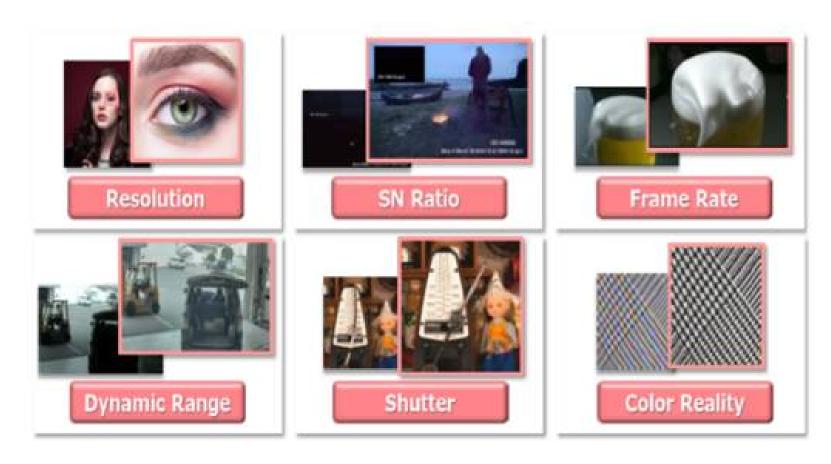

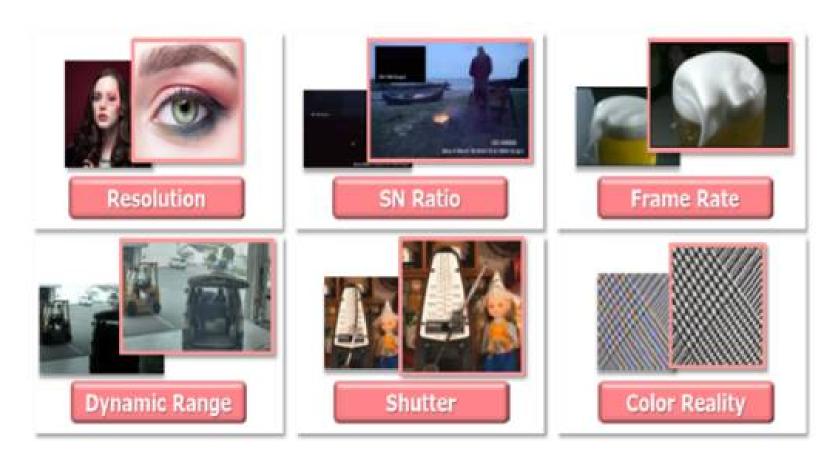

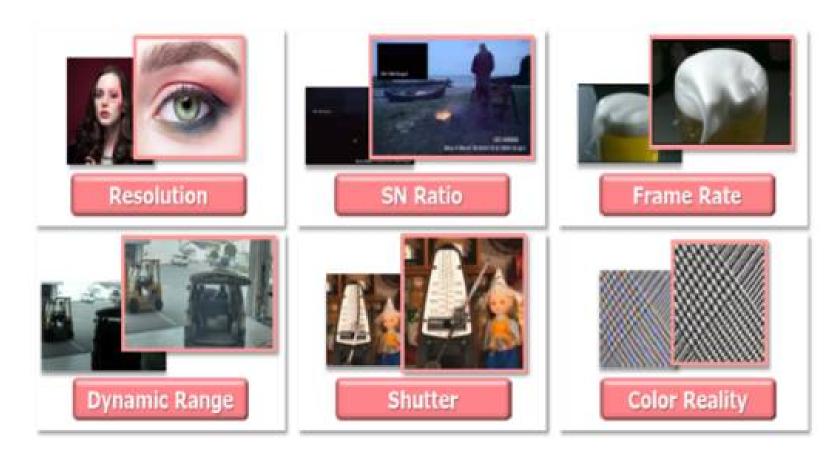

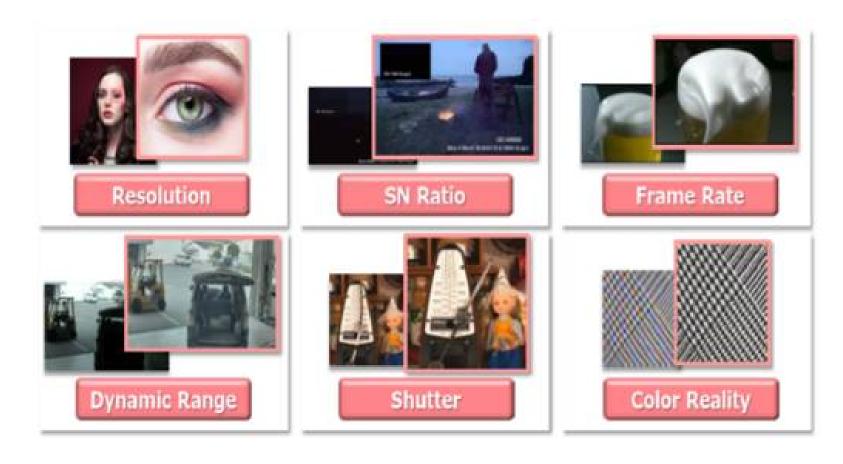

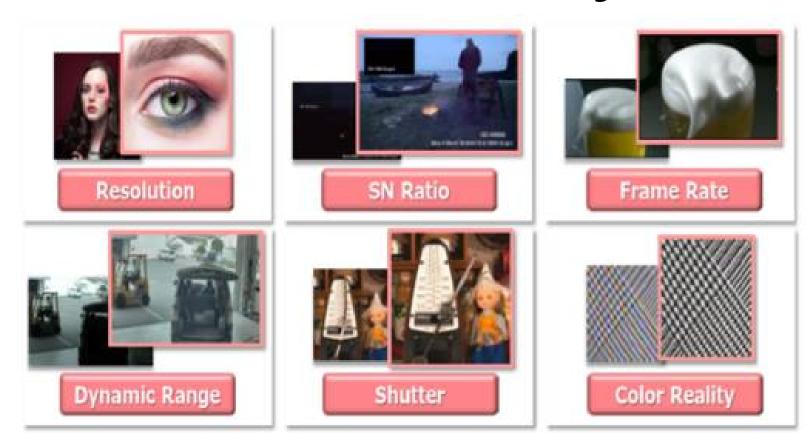

## S/N Ratio

## **Frame Rate**

## **Dynamic Range**

## Shutter

## **Color Reality**

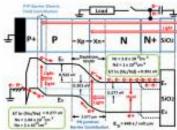

## (1) N+P junction Photodiode in 1960s

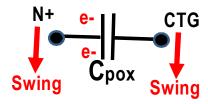

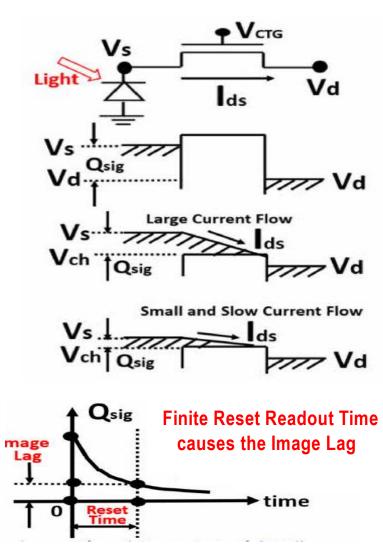

#### Parasitic Oxide Capacitor Cpox

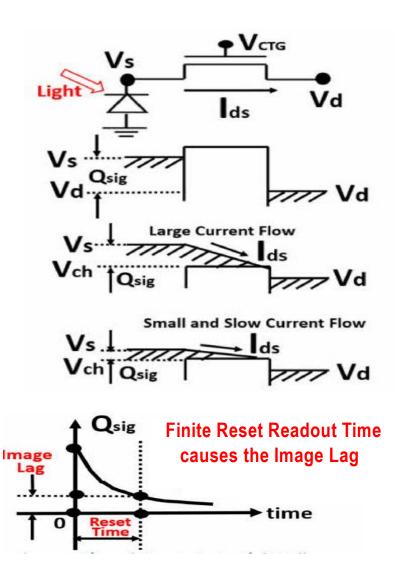

$$lds = K (Vs - Vch)^2$$

As

$$(Vs - Vch) \rightarrow 0$$

$Ids \rightarrow 0$

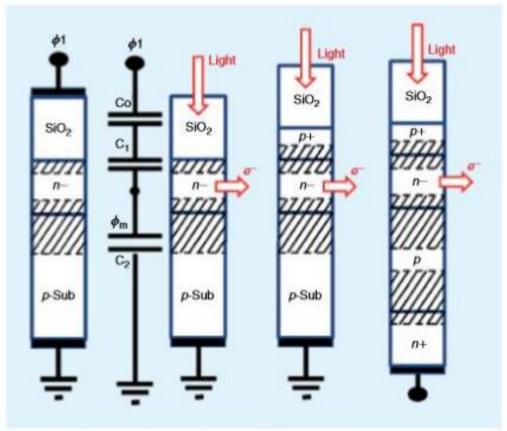

## (1) N+P junction Photodiode in 1960s

More Problem

Poor Blue Light Sensitivity Problem

Single Junction N+P type Solar Cell also has a very poor short wave blue light sensitivity.

16

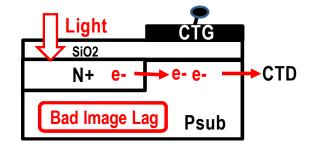

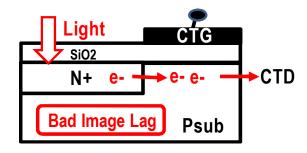

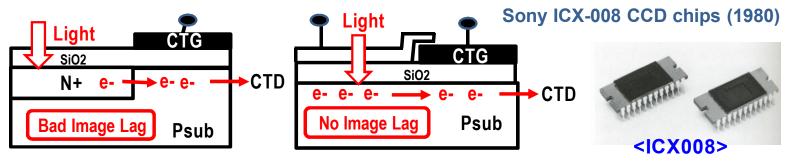

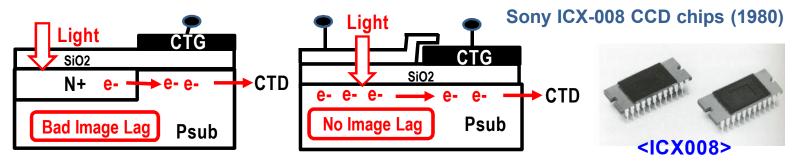

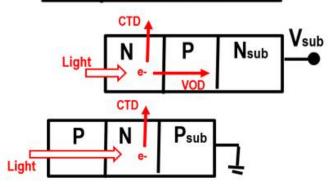

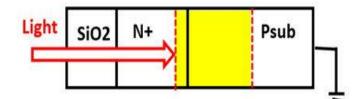

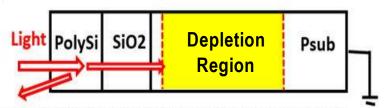

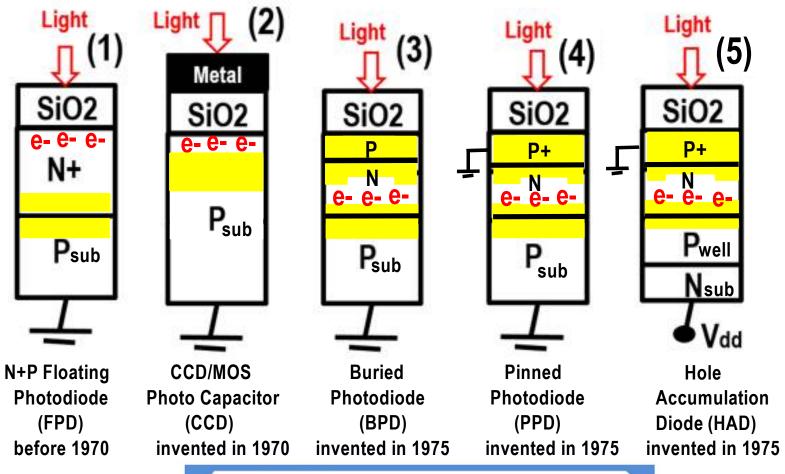

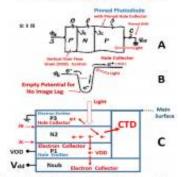

# (1) N+P junction Photodiode in 1960s (2) Transparent Electrode CCD/MOS Photo Capacitor (1980) Light SiO2 N+ e- e- e- CTD Bad Image Lag Psub

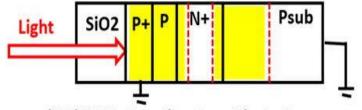

#### (2) Transparent Electrode CCD/MOS Photo Capacitor (1980)

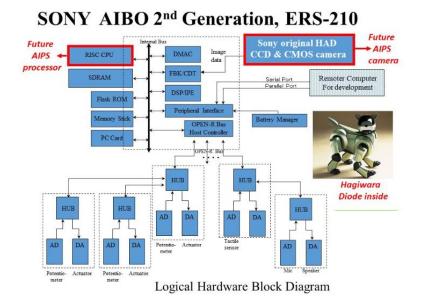

CCD/MOS Dynamic Photo Capacitor with no image lag for action pictures with Electric Shutter Function XC-1 1980 Two-Chip Color Video Camera on ANA 747 Jumbo Jet

all solid state = robustness

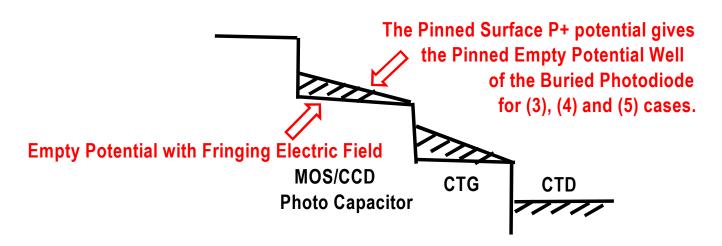

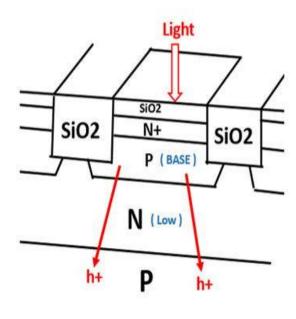

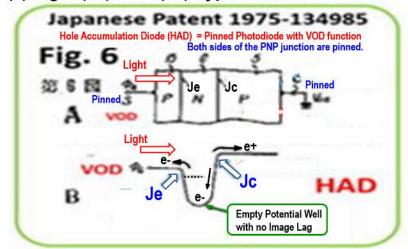

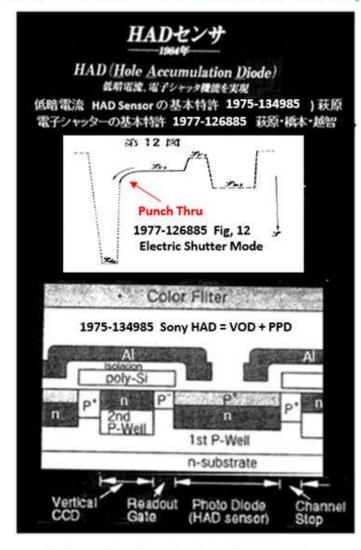

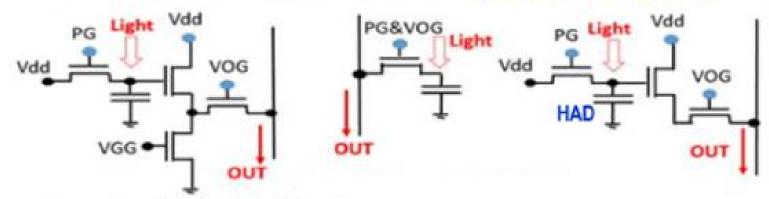

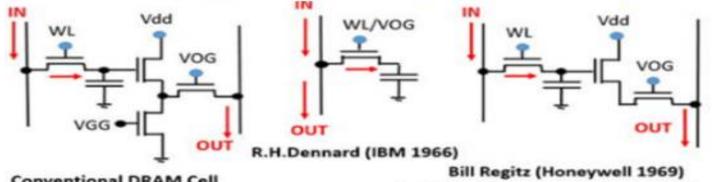

(3) P+NPNsub 接合型 Photodiode **Hole Accumulation Diode (HAD)**

(4) P+PNP 接合型 Photodiode

(5) P+PNPN接合型 Photodiode Global Shutter Buffer MOS Memory Global Shutter Buffer MOS Memory

19

#### (2) Transparent Electrode CCD/MOS Photo Capacitor (1980)

(3) P+NPNsub 接合型 Photodiode **Hole Accumulation Diode (HAD)**

(4) P+PNP 接合型 Photodiode

(5) P+PNPN接合型 Photodiode Global Shutter Buffer MOS Memory Global Shutter Buffer MOS Memory

20

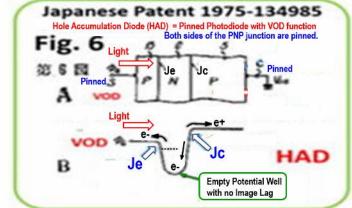

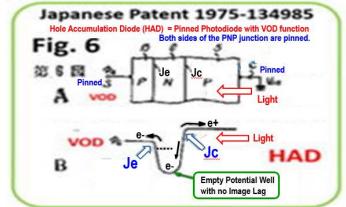

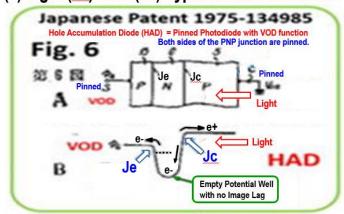

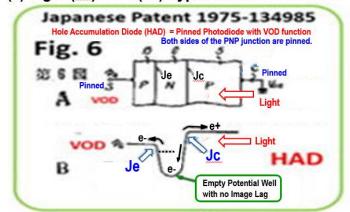

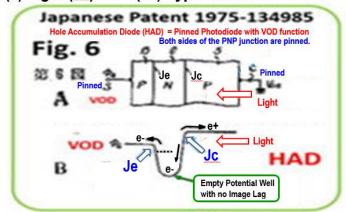

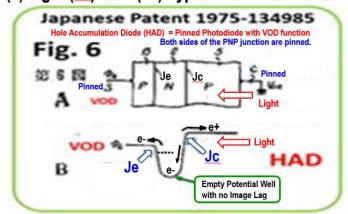

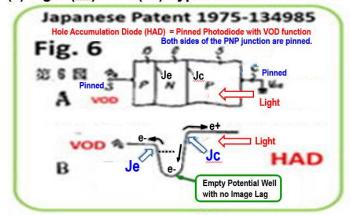

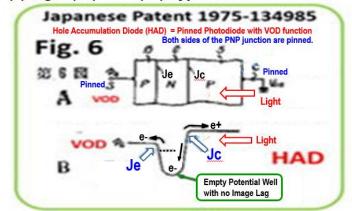

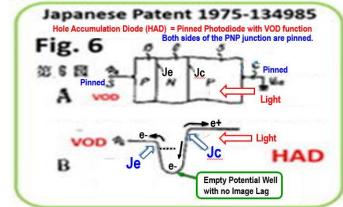

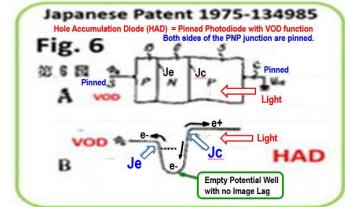

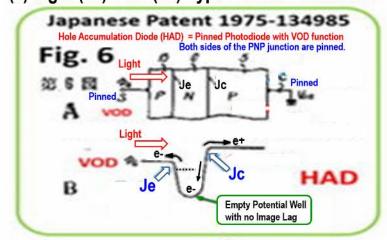

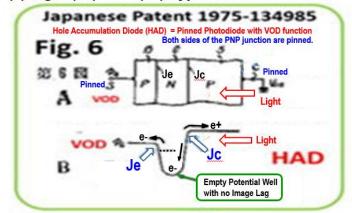

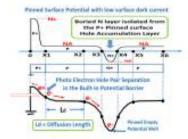

● P+NPNsub Pinned Photodiode (JAP 1975-134985)

with VOD function and No Image Lag by Hagiwara (1975)

● NPNsub with VOD function (JAP 1978-1971)

by Yamada at Toshiba (1978)

● PNPsub Buried Photodiode (JAP 1980-138026)

by Teranish at Toshiba (1978)

P+ 表面はピン留めされている。

21

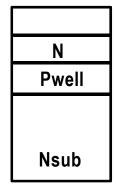

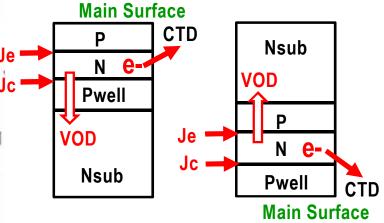

Pwell

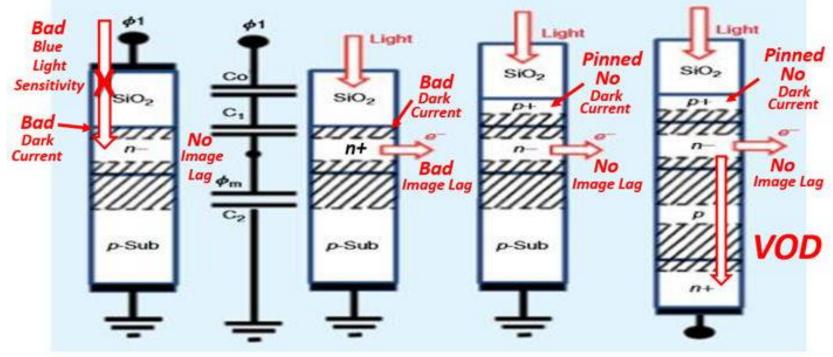

#### **Comparison of Various Light Detecting Photo Sensor Structures**

| type feature           | Classical<br>N+Psub<br>Photodiode | Surface<br>Channel<br>CCD | Buried<br>Channel<br>CCD | Yamada<br>1978<br>NPNsub | Teranishi<br>1980<br>PNPsub | Hagiwara<br>1975<br>PNPNsub |

|------------------------|-----------------------------------|---------------------------|--------------------------|--------------------------|-----------------------------|-----------------------------|

| Blue Light Sensitivity | Δ                                 | х                         | х                        | 0                        | 0                           | 0                           |

| Low Image Lag          | х                                 | 0                         | 0                        | х                        | 0                           | 0                           |

| Surface Dark Current   | 0                                 | х                         | х                        | х                        | 0                           | 0                           |

| Surface Trap Noise     | 0                                 | х                         | 0                        | х                        | 0                           | 0                           |

| Vertical OFD (VOD)     | х                                 | х                         | х                        | 0                        | х                           | 0                           |

| Electrical Shutter     | х                                 | х                         | х                        | х                        | х                           | 0                           |

The actual 1978 Sony HAD sensor has the P+PN+Psub Junction type Pinned Photodiode (PPD) sensor structure for the excellent short wave blue light sensitivity.

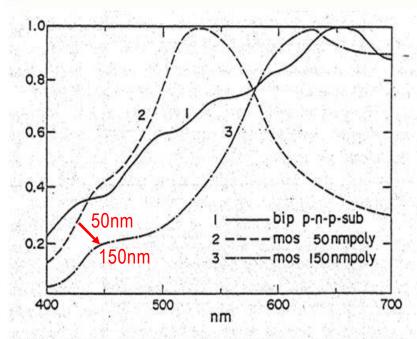

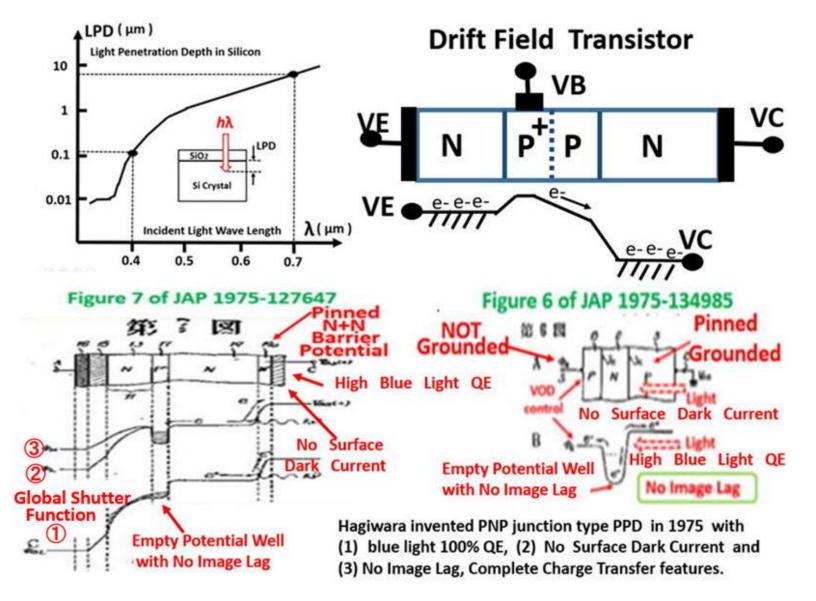

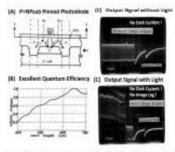

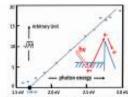

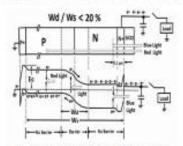

Fig. 7. Relative spectrum response. The relative response of the bipolar-type SiO<sub>2</sub>-P2-N1-P1-SUB structure is compared with poly-SiO<sub>2</sub>-N2-P(SUB) structures of the polysilicon thickness of 50 and 150 nm.

(0) Original N+P junction type Photo Sensor with very poor short wave blue light sensitivity

(1) Bip PNPsub junction type Photo Sensor with excellent short wave blue light sensitivity

(2,3) MOS Capacitor type Photo Sensor with fairly good short wave blue light sensitivity

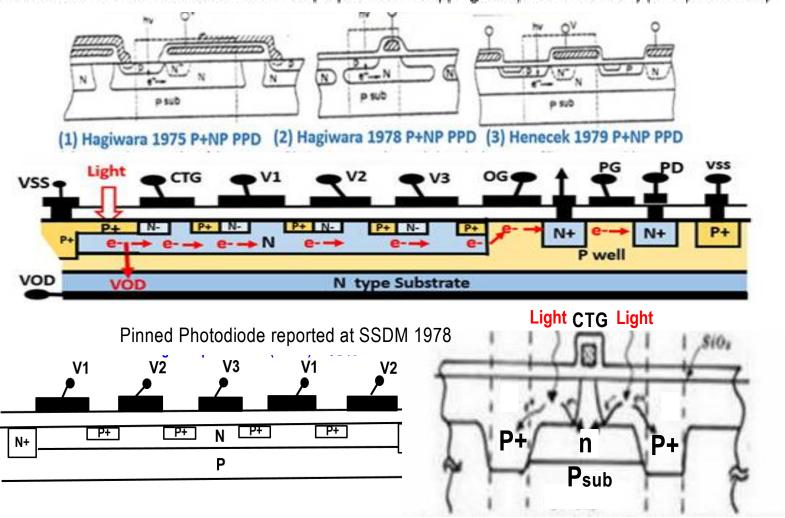

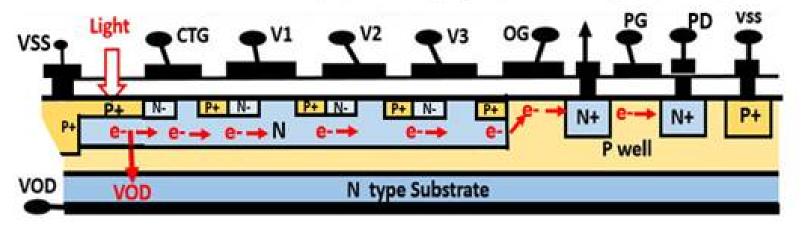

Yoshiaki Hagiwara,"High Density and High Quality Frame Transfer CCD Imager with Very Low Smear, Low Dark Current and Very High Blue Sensitivity", IEEE Transaction on Electron Devices, Vol 43, no. 12, December 1996 http://www.aiplab.com/P1996\_Pinned\_Photodidoe\_used\_in\_Sony\_1980\_FT\_CCD\_Image\_Sensor.pdf

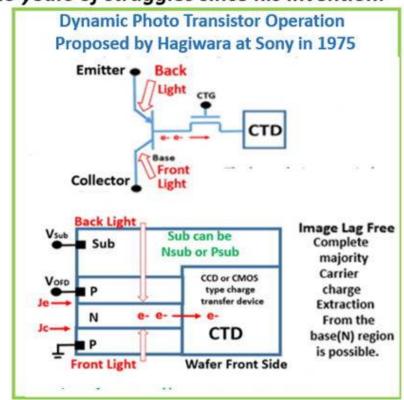

## The N+PNP junction type Dynamic Photo Transistor Structure Pinned Photodiode and Sony Hole Accumulation Diode (HAD) with the vertical overflow drain (VOD) function invented by Hagiwara at Sony in 1975

23

Hagiwara's Lab Note at Sony in February 1975

In 1975 at Sony, Yoshiaki Hagiwara filed three Japanese patents JPA1975-127646, JPA1975-127647 and JPA1975-134985 on the Pinned Surface Photodiode with the VOD function which is later called as Sony Hole Accumulation Diode (HAD). Hagiwara did not file a patent on the SiO2 device isolation but this lab note shows that Hagiwara had an idea of forming the Shallow Trench Isolation by the Local Oxidation Method, which was hinted by the LOCOS isolation in 1970s.

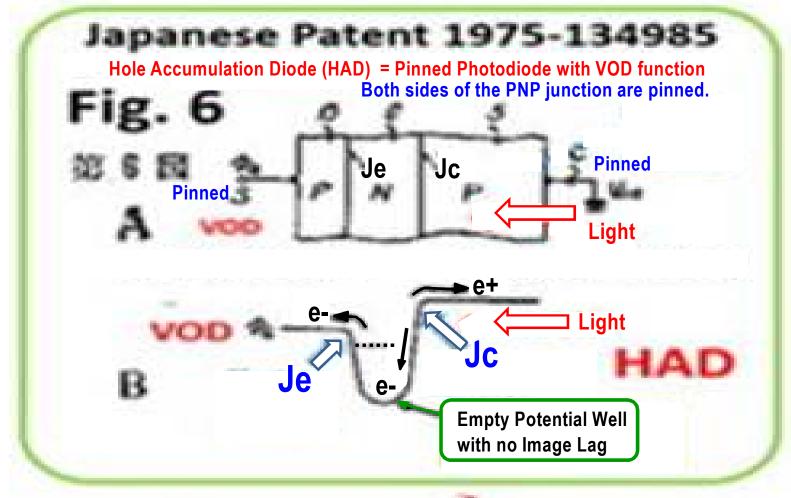

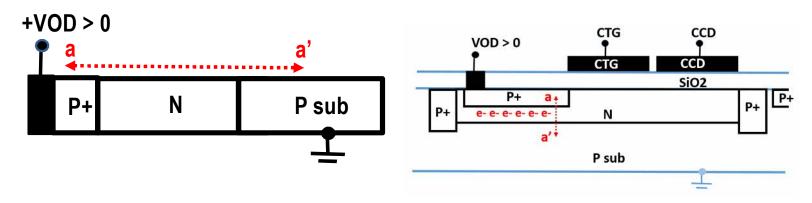

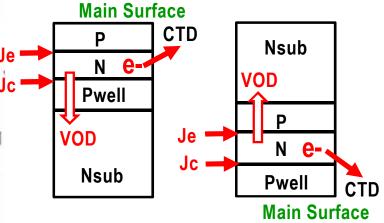

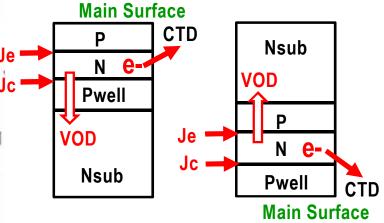

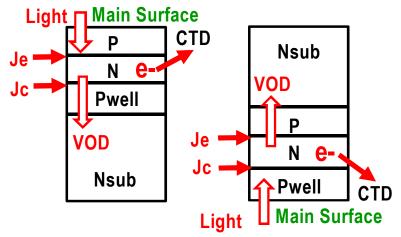

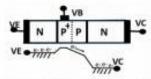

## (1) Light (Jc) VOD (Je) type Pinned Photodiode

Hagiwara invented in 1975 the in-pixel vertical overflow drain (VOD) in PNP Pinned Photodiode.

Image Sensor Story

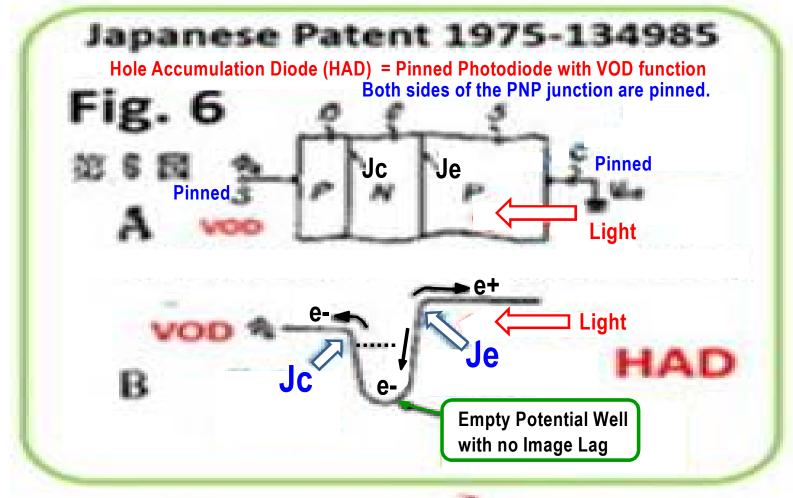

## (2) Light (Je) VOD (Jc) type Pinned Photodiode

Hagiwara invented in 1975 the in-pixel vertical overflow drain (VOD) in PNP Pinned Photodiode.

Image Sensor Story

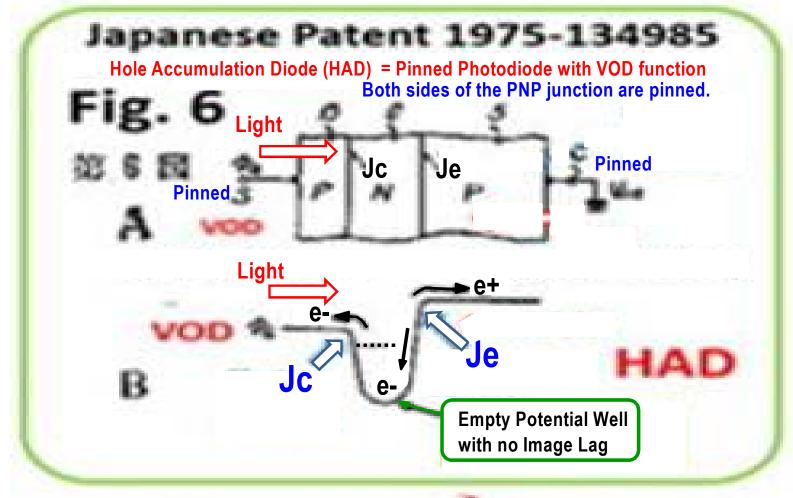

## (3) Light (Jc) VOD (Jc) type Pinned Photodiode

Hagiwara invented in 1975 the in-pixel vertical overflow drain (VOD) in PNP Pinned Photodiode.

Image Sensor Story

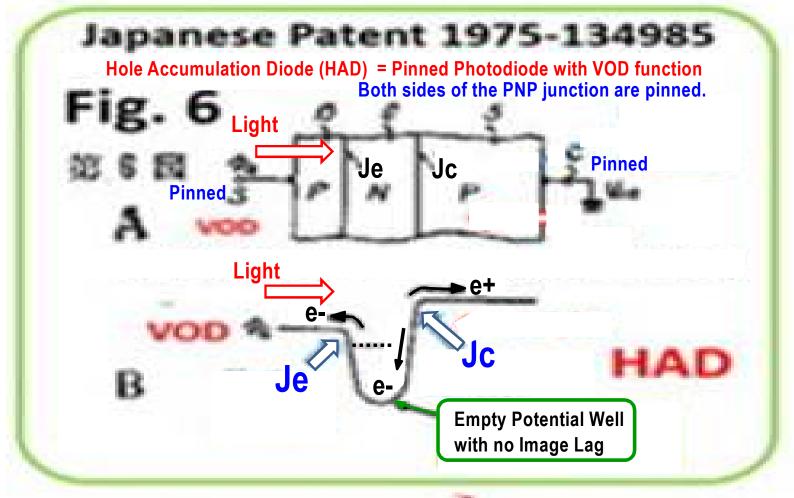

## (4) Light (Je) VOD (Je) type Pinned Photodiode

Hagiwara invented in 1975 the in-pixel vertical overflow drain (VOD) in PNP Pinned Photodiode.

Image Sensor Story

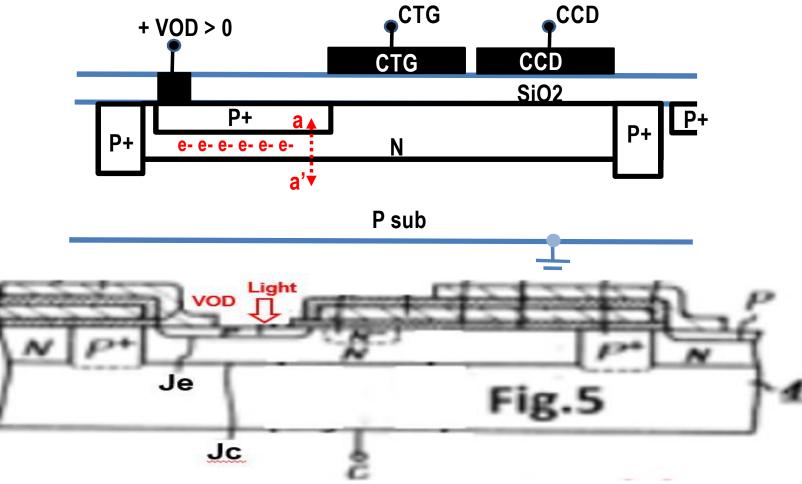

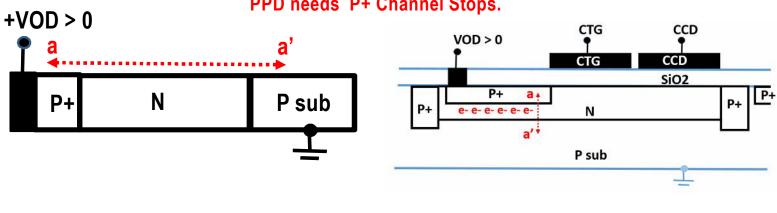

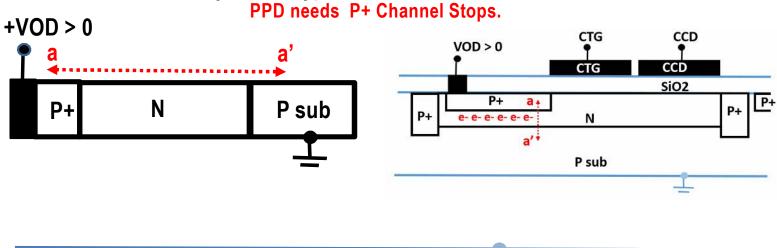

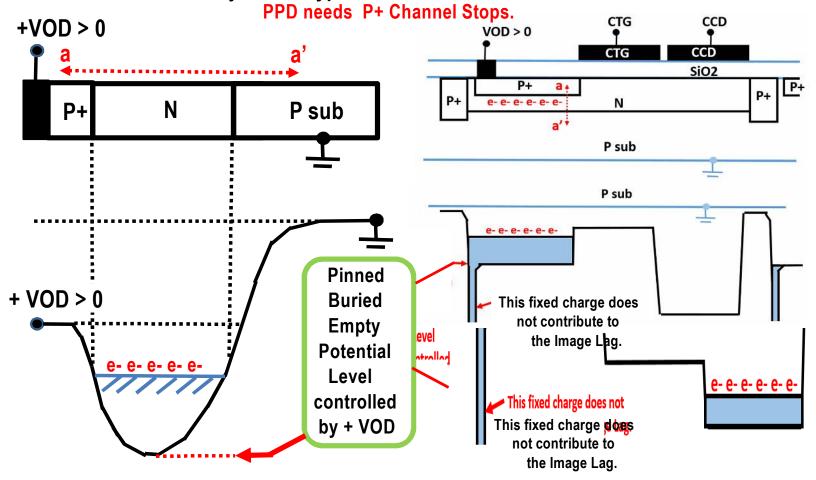

#### (4) Light (Je) VOD (Je) type Pinned Photodiode

Light(Je) type Pinned Photodiode

Je side is used for light illumination

VOD(Je) type Pinned Photodiode

Je side is used for VOD action

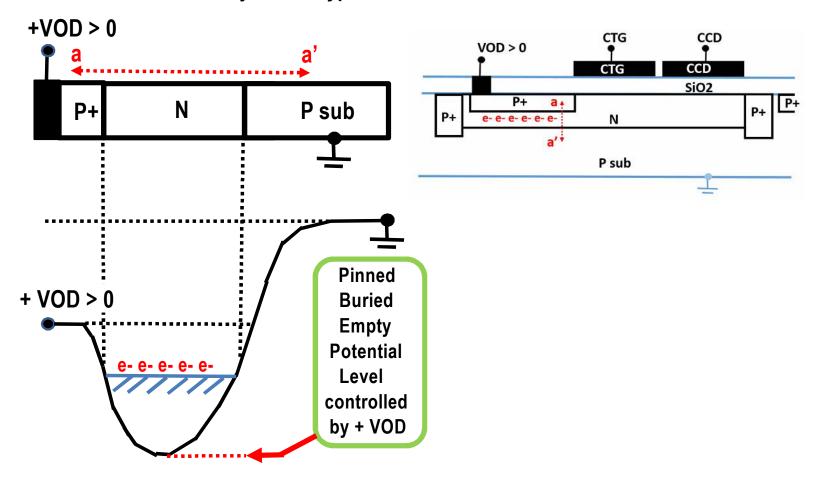

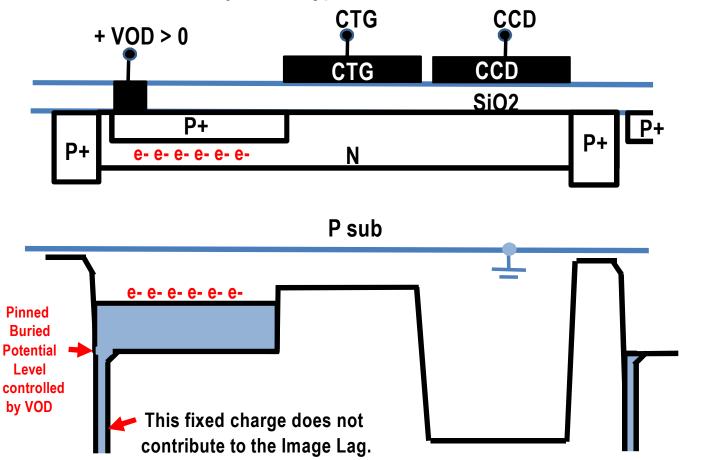

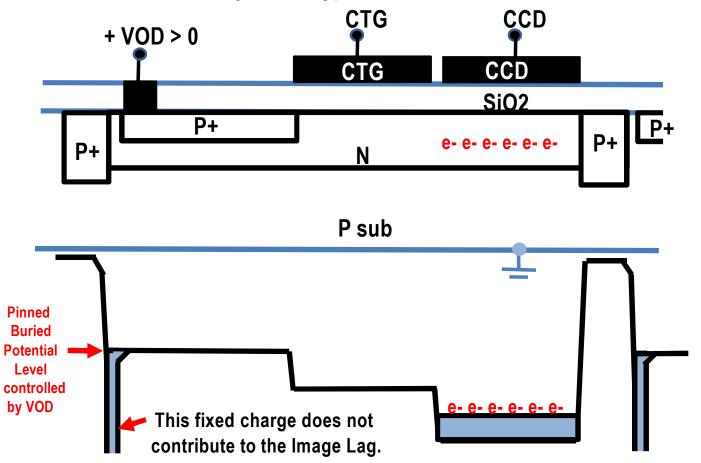

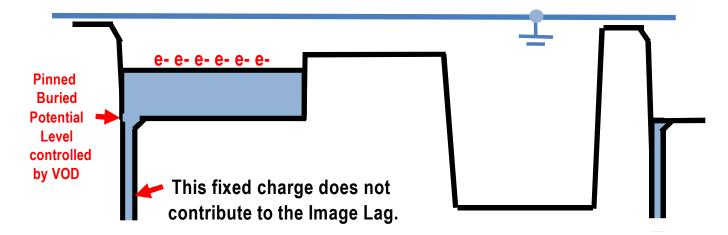

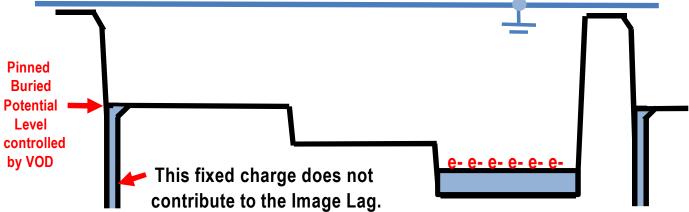

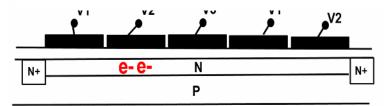

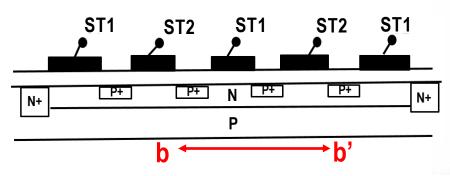

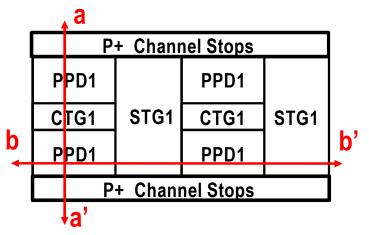

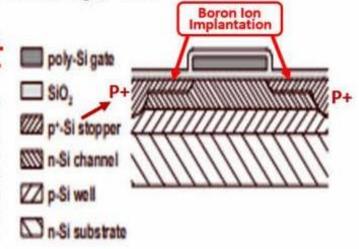

### PPD needs P+ Channel Stops.

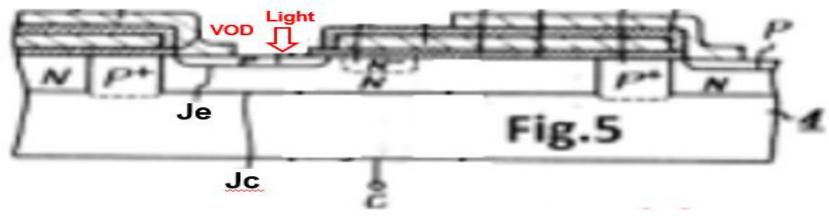

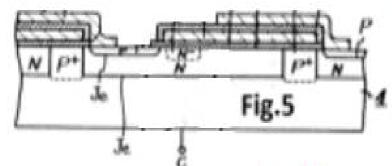

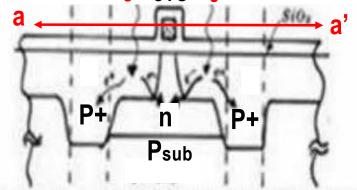

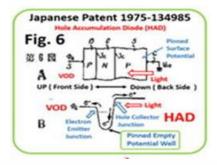

Fig. 5 of the Japanese Patent Application JPA 1975-134985 shows the P+NP double junction type Pinned Photodiode with the VOD function

Fig. 5 of the Japanese Patent Application JPA 1975-134985 shows the P+NP double junction type Pinned Photodiode with the VOD function

Fig. 5 of the Japanese Patent Application JPA 1975-134985 shows the P+NP double junction type Pinned Photodiode with the VOD function

Fig. 5 of the Japanese Patent Application JPA 1975-134985 shows the P+NP double junction type Pinned Photodiode with the VOD function

Fig. 5 of the Japanese Patent Application JPA 1975-134985 shows the P+NP double junction type Pinned Photodiode with the VOD function

Fig. 5 of the Japanese Patent Application JPA 1975-134985 shows the P+NP double junction type Pinned Photodiode with the VOD function PPD needs P+ Channel Stops.

Fig. 5 of the Japanese Patent Application JPA 1975-134985 shows the P+NP double junction type Pinned Photodiode with the VOD function

Fig. 5 of the Japanese Patent Application JPA 1975-134985 shows the P+NP double junction type Pinned Photodiode with the VOD function

SONY HAD ( Pinned Photodiode ) Publications at the International Solid State Device Conference in 1978 and the Tokyo & New York SONY Press Conference in 1980

The original Pinned Photodiode (PPD) structure was invented by Hagiwara at Sony in 1975.

The first one-chip color video camera with a FT CCD image sensor with P+NP junction type

Pinned Photodiode (PPD) was reported by Sony in 1980 at Tokyo Press Conference by Iwama

Kazuo of Sony president, and at New York Press conference by Morita Akio of Sony chairman.

Sony original 570H x 498 V one-chip FT CCD Image Sensor with Pinned Photodiode, July 1980

On July 1980, Iwama Kazuo at Sony Tokyo Press Conference and Morita Akio at New York Press Conference announced the one chip CCD video camera with the 8 mm VTR in one box.

#### See the Original 1978 Publication of the Pinned Photodiode Sensor

Y. Daimon-Hagiwara, M. Abe, and C. Okada, "A 380Hx488V CCD imager with narrow channel transfer gates," Proceedings of the 10th Conference on Solid State Devices, Tokyo, 1978; Japanese Journal of Appllied Physics, vol. 18, supplement 18–1, pp. 335–340, 1979

High quality picture of SONY CMOS Imager is also based on SONY HAD ( Pinned Photodiode).

37

Image Sensor Story

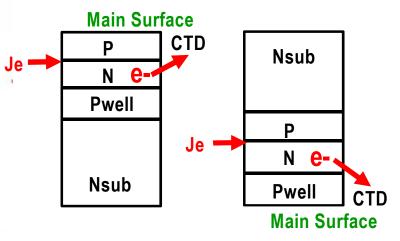

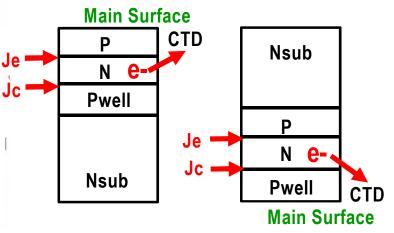

invented by Hagiwara at Sony in Japanese Patent 1975-134985.

Filed 1975/11/10 File 1975-134985 Public 1977/05/13 Public 1975-058414 Grant 1983/10/19

Patent Claim in English Translation

(1) In the semiconductor substrate (Nsub), the first region( Pwell ) of the first impurity type is formed, (2) on which, the second region (N) of the second impurity type is formed. (3) The charge (e-) from the light collecting part (N/Pwe Junction ) is transferred to the adjacent charge transfer device (CTD). (4) Both are placed along the main surface of the semiconductor substrate. (4) Light(Je)VOD(Jc) (5) In the solid stare image sensor so defined, a rectifying Emitter junction ( Je ) is formed on the second region (N) of the light collecting part (N/Pwell), (6) forming a PNP Junction type transistor structure with the N/Pwell junction as Collector junction ( Jc ). (7) The charge, stored in the Base region (N) according to the illuminated light intensity, is transferred to the adjacent CTD. The solid state image sensor so defined is in the scope of this patent claim.

(4) Light (Je) VOD (Je) type Pinned Photodiode

(1) Light(Jc) VOD(Je)

Visit https://www.j-platpat.inpit.go.jp/ and type Japanese Patent Number 1975-134985

invented by Hagiwara at Sony in Japanese Patent 1975-134985.

Filed 1975/11/10 File 1975-134985 Public 1977/05/13 Public 1975-058414 Grant 1983/10/19

Patent Claim in English Translation

(1) In the semiconductor substrate (Nsub), the first region( Pwell ) of the first impurity type is formed, (2) on which, the second region (N) of the second impurity type is formed. (3) The charge (e-) from the light collecting part (N/Pwe Junction ) is transferred to the adjacent charge transfer device (CTD). (4) Both are placed along the main surface of the semiconductor substrate. (4) Light(Je)VOD(Jc) (5) In the solid stare image sensor so defined, a rectifying Emitter junction ( Je ) is formed on the second region (N) of the light collecting part (N/Pwell), (6) forming a PNP Junction type transistor structure with the N/Pwell junction as Collector junction ( Jc ). (7) The charge, stored in the Base region (N) according to the illuminated light intensity, is transferred to the adjacent CTD. The solid state image sensor so defined is in the scope of this patent claim.

(1) Light (Jc) VOD (Je) type Pinned Photodiode

invented by Hagiwara at Sony in Japanese Patent 1975-134985.

File 1975-134985 Filed 1975/11/10 Public 1975-058414 Public 1977/05/13 Grant 1983/10/19

Patent Claim in English Translation

In the semiconductor substrate (Nsub),

(1) Light (Jc) VOD (Je) type Pinned Photodiode

(4) Light(Je)VOD(Jc)

(1) Light(Jc) VOD(Je)

Nsub

Nsub

Visit https://www.j-platpat.inpit.go.jp/ and type Japanese Patent Number 1975-134985

invented by Hagiwara at Sony in Japanese Patent 1975-134985.

File 1975-134985 Filed 1975/11/10 Public 1975-058414 Public 1977/05/13 Grant 1983/10/19

Patent Claim in English Translation

In the semiconductor substrate (Nsub), the first region( Pwell ) of the first impurity type is formed, (1) Light (Jc) VOD (Je) type Pinned Photodiode

(4) Light(Je)VOD(Jc)

(1) Light(Jc) VOD(Je)

Pwell Nsub Nsub

Pwell

invented by Hagiwara at Sony in Japanese Patent 1975-134985.

File 1975-134985 Filed 1975/11/10 Public 1975-058414 Public 1977/05/13 Grant 1983/10/19

Patent Claim in English Translation

(1) In the semiconductor substrate (Nsub), the first region (Pwell) of the first impurity type is formed, (2) on which, the second region (N) of the second impurity type is formed. (1) Light (Jc) VOD (Je) type Pinned Photodiode

(4) Light(Je)VOD(Jc)

invented by Hagiwara at Sony in Japanese Patent 1975-134985.

File 1975-134985 Filed 1975/11/10 Public 1975-058414 Public 1977/05/13 Grant 1983/10/19

Patent Claim in English Translation

(1) In the semiconductor substrate (Nsub), the first region( Pwell ) of the first impurity type is formed, (2) on which, the second region ( N ) of the second impurity type is formed. (3) The charge (e-) from the light collecting part (N/Pwell Junction ) is transferred to the adjacent charge transfer device (CTD). (1) Light (Jc) VOD (Je) type Pinned Photodiode

(4) Light(Je)VOD(Jc)

invented by Hagiwara at Sony in Japanese Patent 1975-134985.

Filed 1975/11/10 File 1975-134985 Public 1977/05/13 1975-058414 Public Grant 1983/10/19

Patent Claim in English Translation

(1) In the semiconductor substrate (Nsub), the first region( Pwell ) of the first impurity type is formed, (2) on which, the second region (N) of the second impurity type is formed. (3) The charge (e-) from the light collecting part (N/Pwe Junction ) is transferred to the adjacent charge transfer device (CTD). (4) Both are placed along the main surface of the semiconductor substrate. (4) Light(Je)VOD(Jc)

(1) Light (Jc) VOD (Je) type Pinned Photodiode

invented by Hagiwara at Sony in Japanese Patent 1975-134985.

Filed 1975/11/10 File 1975-134985 Public 1977/05/13 1975-058414 Public Grant 1983/10/19

Patent Claim in English Translation

(1) In the semiconductor substrate (Nsub), the first region( Pwell ) of the first impurity type is formed, (2) on which, the second region (N) of the second impurity type is formed. (3) The charge (e-) from the light collecting part (N/Pwe Junction ) is transferred to the adjacent charge transfer device (CTD). (4) Both are placed along the main surface of the semiconductor substrate. (4) Light(Je)VOD(Jc) (5) In the solid stare image sensor so defined, a rectifying Emitter junction ( Je ) is formed on the second region (N) of the light collecting part (N/Pwell),

(1) Light (Jc) VOD (Je) type Pinned Photodiode

invented by Hagiwara at Sony in Japanese Patent 1975-134985.

Filed 1975/11/10 File 1975-134985 Public 1977/05/13 1975-058414 Public Grant 1983/10/19

Patent Claim in English Translation

(1) In the semiconductor substrate (Nsub), the first region( Pwell ) of the first impurity type is formed, (2) on which, the second region (N) of the second impurity type is formed. (3) The charge (e-) from the light collecting part (N/Pwe Junction ) is transferred to the adjacent charge transfer device (CTD). (4) Both are placed along the main surface of the semiconductor substrate. (4) Light(Je)VOD(Jc) (5) In the solid stare image sensor so defined, a rectifying Emitter junction ( Je ) is formed on the second region (N) of the light collecting part (N/Pwell), (6) forming a PNP Junction type transistor structure with the N/Pwell junction as Collector junction ( Jc ).

(1) Light (Jc) VOD (Je) type Pinned Photodiode

invented by Hagiwara at Sony in Japanese Patent 1975-134985.

Filed 1975/11/10 File 1975-134985 Public 1977/05/13 Public 1975-058414 Grant 1983/10/19

Patent Claim in English Translation

(1) In the semiconductor substrate (Nsub), the first region( Pwell ) of the first impurity type is formed, (2) on which, the second region (N) of the second impurity type is formed. (3) The charge (e-) from the light collecting part (N/Pwe Junction ) is transferred to the adjacent charge transfer device (CTD). (4) Both are placed along the main surface of the semiconductor substrate. (4) Light(Je)VOD(Jc) (5) In the solid stare image sensor so defined, a rectifying Emitter junction ( Je ) is formed on the second region (N) of the light collecting part (N/Pwell), (6) forming a PNP Junction type transistor structure with the N/Pwell junction as Collector junction ( Jc ). (7) The charge, stored in the Base region (N) according to the illuminated light intensity, is transferred to the adjacent CTD. The solid state image sensor so defined is in the scope of this patent claim.

(1) Light (Jc) VOD (Je) type Pinned Photodiode

invented by Hagiwara at Sony in Japanese Patent 1975-134985.

(4) Light (Je) / VOD (Je) type

Light(Je) Je side is used for light illumination VOD(Jc) Jc side is used for VOD action

(4) Light (Je) VOD (Je) type Pinned Photodiode

(1) Light (Jc) VOD (Je) type Pinned Photodiode

(4) Light(Je)VOD(Jc)

(1) Light(Jc) VOD(Je)

Visit https://www.j-platpat.inpit.go.jp/ and type Japanese Patent Number 1975-134985

Finally the Sony-Fairchild Patent Wat(1991-2000) ended over the Sony HAD Sensor which is identical to the P+NPNsub junction type Pinned Photodiode with Vertical Overflow Drain, originally invented by Hagiwara at Sony in 1975.

SONY 2000年度 \$8許第1215101号 因体摄像装置 曹保明は卓越した創造性および先見性により 会社に対し顕著な貢献がありましたので 発明考案規定に基づき ここに本質を贈りこれを賞します 2001年4月26日 ソニー株式会社

And finally Hagiwara received for his 1975-134985 Japanese Patent officially, the First Patent Award from Mr. Ando, Sony president in April, 2001 after more 26 years of struggles since his invention.

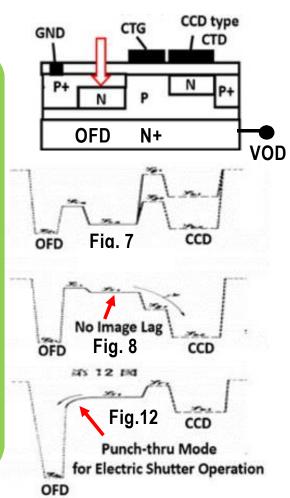

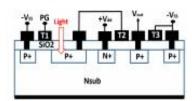

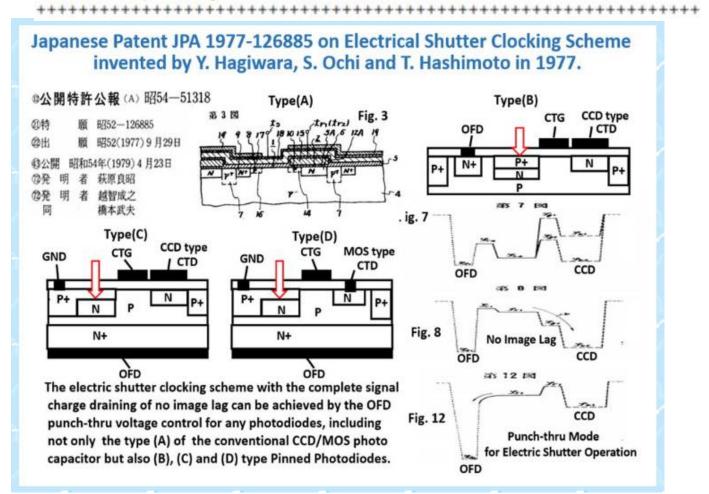

# Japanese Patent JPA 1977-126885 on Electrical Shutter Clocking Scheme invented by Y. Hagiwara, S. Ochi and T. Hashimoto in 1977.

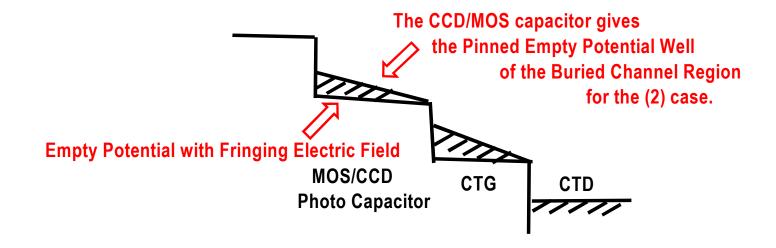

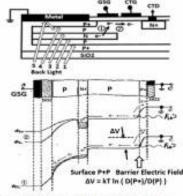

Fig. 3 CCD/MOS Photo Capacitor

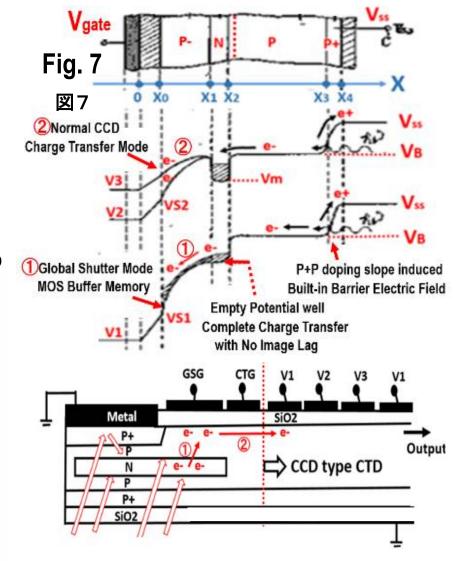

# CTG CCD OFD: CCD OFD Fig. 8 Gamma Control Mode CTG: Punch-thru CCD Fig. 12 Electric Shutter Mode 新 12 图 **Complete Charge Transfer OFD** and no image lag

#### Pinned Photodiode with VOD function

The electric shutter clocking scheme with the complete draining of signal charge with the no image lag feature can be achieved by controlling the overflow drain (OFD) punch-thru voltage.

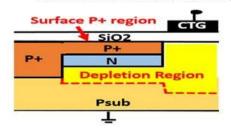

## The Pinned Photodiode (Sony Original HAD sensor) Structure

(from SONY Product Catalog)

Electric Shutter Basic Patent Award from Sony President Idei to Yoshiaki Hagiwara for Japanese Patent 1977-126885 by Hagiwara

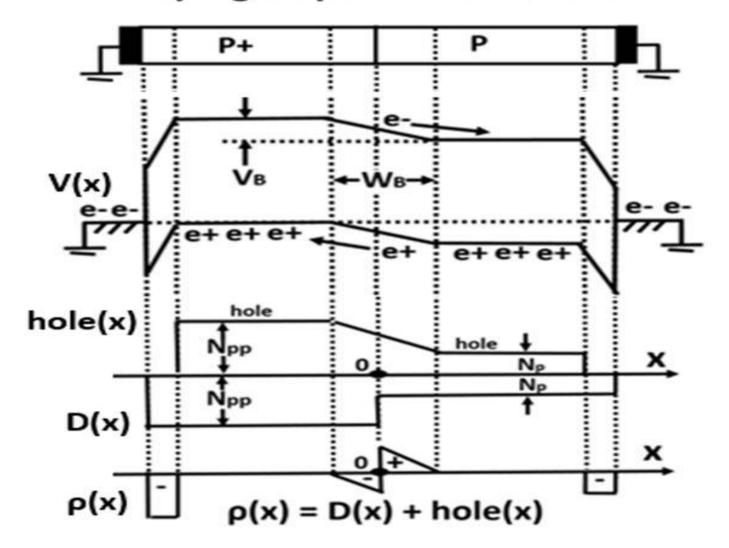

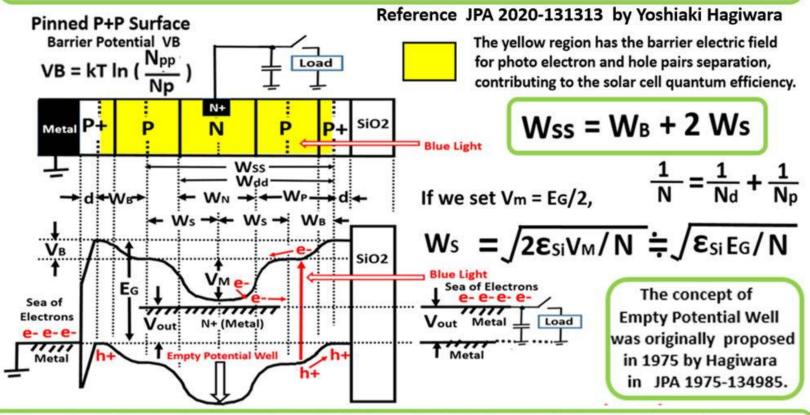

## P+P Doping Slope Barrier Potential VB

Image Sensor Story

Image Sensor Story

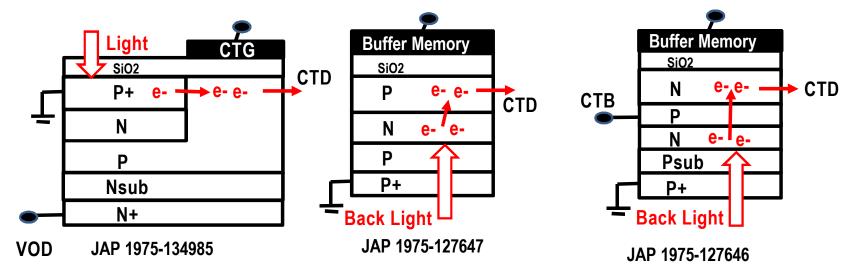

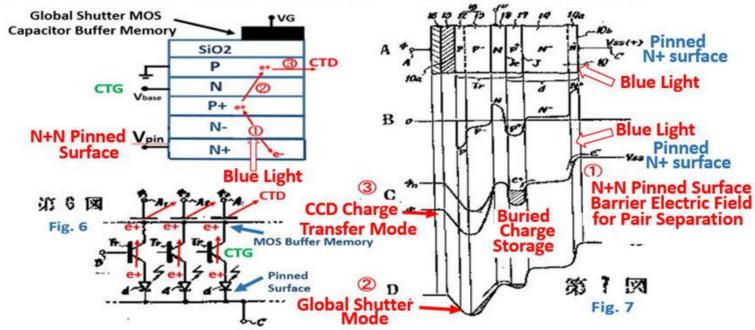

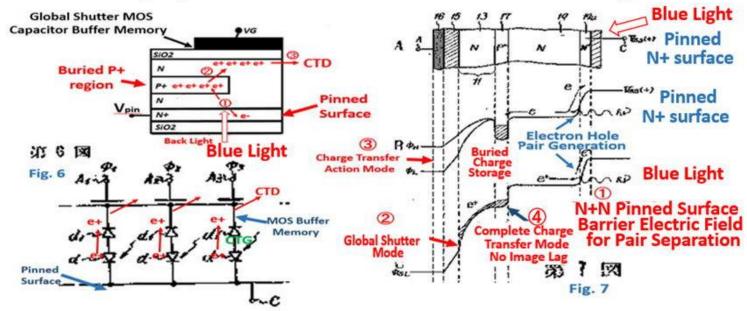

#### Japanese Patent 1975-127646

N+NP+NP junction type Buried Pinned Photodiode with Built-in MOS Capacitor Buffer Memory Global Shutter Function and the surface N+N doping slope Barrier Electric Field Photo Pair Generation

The First Japanese PPD Patent Application JPA 1975-127646 was applied for the back light illumination type Pinned Photodiode (PPD) image sensors with the CCD/MOS capacitor type buffer memory for Global Shutter Function which is a very important function needed for Modern CMOS Image Sensors.

Double Junction Dynamic Photo Transistor (PPD) invented in 1975 by Hagiwara at Sony.

Triple Junction Dynamic Photo Thyristor (HAD) invented in 1975 by Hagiwara at Sony.

See Japanese Patent Application JPA 1975-127646, 1975-127647 and 1975-134985

# Global Shutter Japanese Patent 1975-127647

Complete Charge Transfer Mode No Image Lag

N+NP+N junction type Buried Pinned Photodiode No Image Lag

with Built-in MOS Capacitor Buffer Memory Global Shutter Function

and the surface N+N doping slope Barrier Electric Field Photo Pair Generation

This Japanese PPD Patent Application JPA 1975-127647 was also applied for the back light illumination type Pinned Photodiode (PPD) image sensors with the CCD/MOS capacitor type buffer memory for Global Shutter Function which is a very important function needed for Modern CMOS Image Sensors.

Double Junction Dynamic Photo Transistor (PPD) invented in 1975 by Hagiwara at Sony.

Triple Junction Dynamic Photo Thyristor (HAD) invented in 1975 by Hagiwara at Sony.

See Japanese Patent Application JPA 1975-127646, 1975-127647 and 1975-134985

### Japanese Patent 1975-134985

### Pinned Photodiode and Sony Hole Accumulation Diode (HAD)

Pinned Surface Double Junction P+NP Dynamic Photo Transistor in the silicon substrate (Nsub) Pinned Photodiode with the vertical overflow drain (VOD) function in the silicon substrate (Nsub)

#### PNPN junction Transistor type Pinned Photodiode

Visit https://www.j-platpat.inpit.go.jp/ and put the patent number 1975-134985

1975-134985 Japanese Patent 1975-134985 1977/05/13 1975-058414 1983/10/19 Fig. 6 Patent Claim in English Translation (1) In the semiconductor substrate (Nsub), the first region(P1) of the first impurity type is formed, (2) on which, the second region (N) of the second impurity type is formed. (3) The charge (e-) from the light collecting part (N) is is transferred to the adjacent charge transfer device (CTD). (4) Both are placed along the main Potential Well surface of the semiconductor substrate. (5) In the solid stare image sensor so defined, a rectifying SiO2 Vsub Emitter junction (Je) is formed on the second Nsub region (N) of the light collecting part (N). And (6) Collector junction ( Jc ) is formed by the VOD Pwell P2 second region (N) and the first region (P1), forming a transistor structure ( P2NP1 ) (7) Photo charge is stored in the Base region (N) according to the P1

Most CCD Image sensors and CMOS Image sensors today are applied with the combination of the vertical overflow drain (VOD) and Pinned Photodiode.

In 1975 Yoshiaki Hagiwara at Sony proposed using a PNP transistor as the photodetector which is the combination of the VOD and Pinned Photodiode.

By providing a P + layer (emitter) for the light incident section, the sensor electrode that covers the entire light receiving surface of the photodiode can be eliminated, greatly improving the light sensitivity. This P + layer was also a proposal to reduce the dark current and image lag which became the basis of the pinned photodiode

Yoshiaki Hagiwara, Japanese Patent JP 1975-134985

illuminated light intensity, and transferred to

defined is in the scope of this patent claim.

the adjacent CTD. The solid state image sensor so

Double Junction Dynamic Photo Transistor (PPD) invented in 1975 by Hagiwara at Sony.

https://www.shmj.or.jp/english/pdf/dis/exhibi1005E.pdf

Triple Junction Dynamic Photo Thyristor (HAD) invented in 1975 by Hagiwara at Sony.

See Japanese Patent Application JPA 1975-127646, 1975-127647 and 1975-134985

CTG

SiO2

VOD may be grounded.

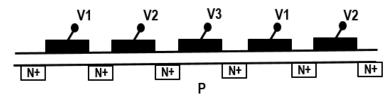

(1) Bucket Brigate Device (BBD)

(2) Surface Channel CCD

(3) Buried Channel CCD

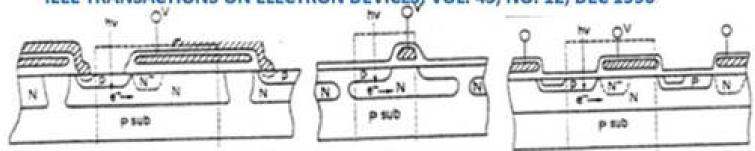

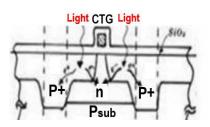

(3) Pinned Photodiode reported at SSDM 1978

Narrow Charge Transfer Gate (CTG) and Pinned Photodiode (PPD) with the adjacent P+ channel stops

The first Pinned Photodiode(PPD) developed in 1978 by Hagiwara and reported at SSDM1978 in Tokyo.

Light CTG Light

The most important idea of the P+NP Double Junction Buried Pinned Photodiode proposed by Hagiwara in the 1975-134985 Japanese Patent Application is the virtual complete charge transfer operation with no image lag which does not need the conventional double polysilicon overlapping CCD process with very poor productivity.

Image Sensor Story

#### See the Japanese Patent 1975-134985 for the original invention of the Pinned Photodiode

High-Density and High-Quality Frame Transfer CCD Imager with Vey Low Smear, Low Dark Current, and Very High Blue Sensitivity

Yoshiaki Hagiwara

IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 43, NO. 12, DEC 1996

#### (1) Hagiwara 1975 P+NP PPD (2) Hagiwara 1978 P+NP PPD (3) Henecek 1979 P+NP PPD

The most important idea of the P+NP Double Junction Buried Pinned Photodiode proposed by Hagiwara in the 1975-134985 Japanese Patent Application is the virtual complete charge transfer operation with no image lag which does not need the conventional double polysilicon overlapping CCD process with very poor productivity.

Hagiwara in 1975 proposed the PPD Charge Transfer which is later called as Virtual Phase Charge Transfer. Hagiwara in 1975 proposed also the NEC Buried Photodiode, the KODAK PPD and the Sony HAD. Study Japanese Patent 1975-127646, 1975-127647 and 1975-134985 for the details.

Image Sensor Story 60

Hagiwara in 1975 proposed the PPD Charge Transfer which is later called as Virtual Phase Charge Transfer. Hagiwara in 1975 proposed also the NEC Buried Photodiode, the KODAK PPD and the Sony HAD. Study Japanese Patent 1975-127646, 1975-127647 and 1975-134985 for the details.

Image Sensor Story

Hagiwara in 1975 proposed the PPD Charge Transfer which is later called as Virtual Phase Charge Transfer. Hagiwara in 1975 proposed also the NEC Buried Photodiode, the KODAK PPD and the Sony HAD. Study Japanese Patent 1975-127646, 1975-127647 and 1975-134985 for the details.

Image Sensor Story 62

Hagiwara in 1975 proposed the PPD Charge Transfer which is later called as Virtual Phase Charge Transfer. Hagiwara in 1975 proposed also the NEC Buried Photodiode, the KODAK PPD and the Sony HAD. Study Japanese Patent 1975-127646, 1975-127647 and 1975-134985 for the details.

Image Sensor Story

Hagiwara in 1975 proposed the PPD Charge Transfer which is later called as Virtual Phase Charge Transfer. Hagiwara in 1975 proposed also the NEC Buried Photodiode, the KODAK PPD and the Sony HAD. Study Japanese Patent 1975-127646, 1975-127647 and 1975-134985 for the details.

Image Sensor Story

Hagiwara in 1975 proposed the PPD Charge Transfer which is later called as Virtual Phase Charge Transfer. Hagiwara in 1975 proposed also the NEC Buried Photodiode, the KODAK PPD and the Sony HAD. Study Japanese Patent 1975-127646, 1975-127647 and 1975-134985 for the details.

Image Sensor Story

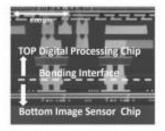

# Back Light Illumination Sony CMOS Image Sensor (2020)

Multi-chips three dimensional LSI chip

P+PNPP+ Junction Buried Pinned Photodiode for Back Light (JAP 1975-127647)

Image Sensor Story

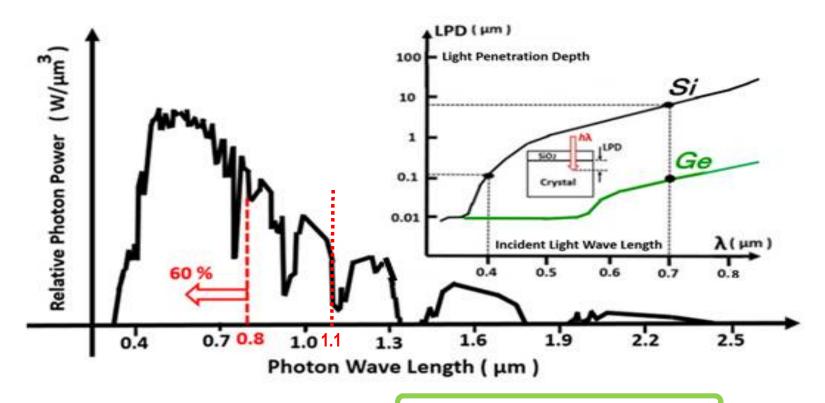

# **Sun Light Spectrum**

$$E = \hbar \omega = h f = h c / \lambda$$

$E (eV) = 1.24 / \lambda (μm)$

For Silicon, Eg = 1.10 eV and  $\lambda$  = 1.12  $\mu m$

The light energy of the wave length more than  $\lambda = 1.12 \mu m$  can not be converted to electrical energy in the silicon crystal.

Image Sensor Story

#### **Conventional N+P Single junction Type Solar Cell**

#### **Poor Blue Light Sensitivity Problem**

Single Junction N+P type Solar Cell also has a very poor short wave blue light sensitivity.

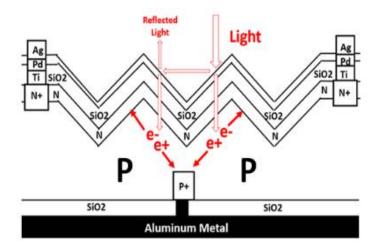

# PNP Double Junction Type Solar Cell proposed by Hagiwara in 2020

Completely depleted Buried N region

In the PNP Double Junction Type Solar Cell

proposed by Hagiwara in 2020

# The P+PNPP+ Junction Type Pinned Photodiode Solar Cell with Very High Blue Light Sensitivity

The surface P+P Pinned Surface Solar Cell with the surface P+P Gaussian doping slope is very important to create the surface barrier electric field for separating the photo electron and hole pairs generated by the short wave length blue light which cannot penetrate into the silicon crystal more than 0.2 µm in depth.

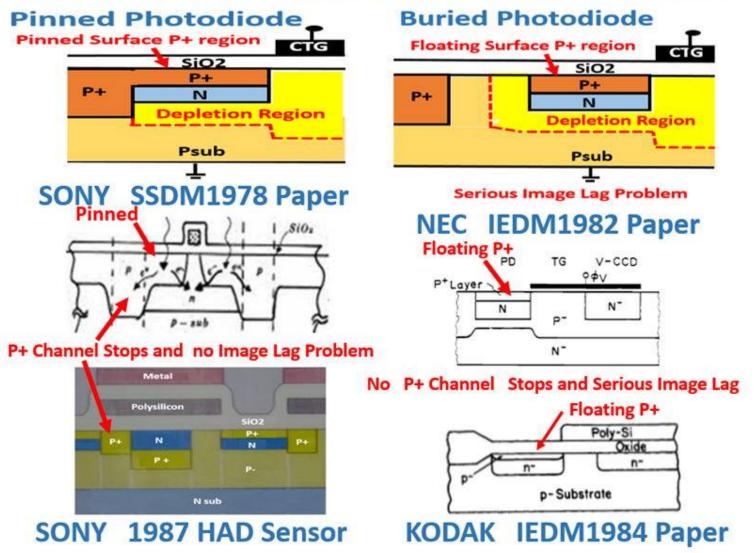

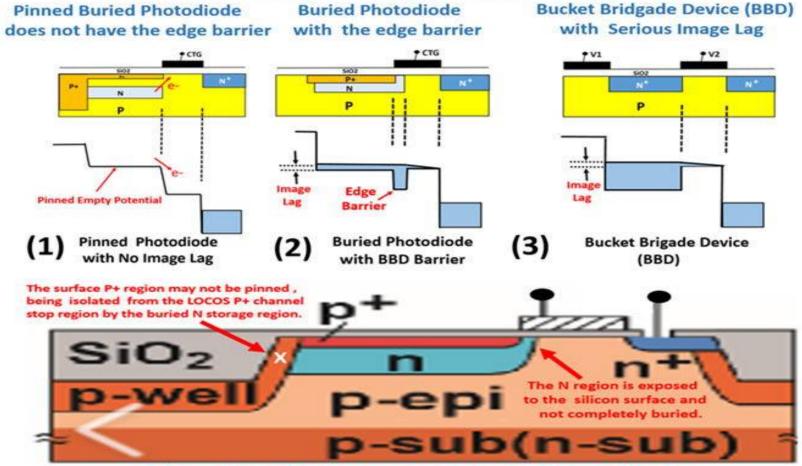

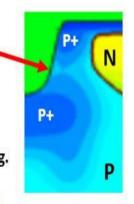

#### Difference of Buried Photodiode and Pinned Photodiode

Figure 5 does not have the P+ channel stop nearby.

#### **Buried Photodiode** Floating Surface P+ region CTG SiO2 (Vlag) N **Depletion Region** Lag Psub Decay Serious Image Lag Problem NEC IEDM1982 Paper Floating PD V-CCD PPV P+Layer N-N

N-

P\*NP\* structure photodiode

No P+ Channel Stops

P- Substrate

Fig. 5.

There is still image lag

at the CTD gate voltage more than 10 volt.

Fig.6. Storageable electrons vs. transfer gate channel potential, and decay lag vs. transfer gate channel potential in the P\*NP\* structure

TG Channel Potential (#15)

Storageable Electrons of PD (Experiment)

1st Field

Storageable

70

NEC IEDM1982 Paper reported Image Lag

Figure 6 shows that there is still image lag at the CTG gate voltage of > 10 volt.

photodiode

#### Difference of Buried Photodiode and Pinned Photodiode

Image Sensor Story

#### Difference of Pinned Photodiode and Buried Photodiode

Pinned Photodiode must have the P+ heavy doped channel stops nearby.

Pinned Photodiode must be a buried photodiode.

Pinned Photodiode must not have the edge barrier to the Charge Transfer Gate

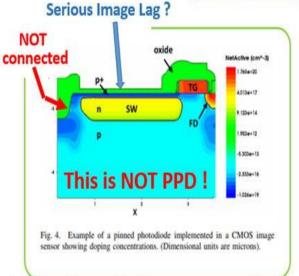

This photodiode is not Pinned Photodiode since the N storage region is not completely buried. Albert J.P. Theuwissen, Jan T.J. Bosiers, Edwin Roks, "The Hole Role", an invited paper at IEDM2005, Washington DC, Techn. Dig., 2005.

But in the case that parts of the depleted n-type CCD channels are not covered by gate material, their surface potential is undefined! Such a structure will suffer from charge transport issues during operation, because charge can be trapped in local potential pockets. The effect can be solved by defining the potential in the open areas through an extension of the p\* channel stopper. A simple self-aligned implant of 2x10<sup>13</sup> /cm² boron ions is sufficient to extend the channel stop areas to the gate edge and consequently fix the potential in the open areas [2]. The result after this self-aligned implant is shown in Figure 3. The presence of enough holes plays a crucial role in fixing the potential for the regions "beyond control" of the gates. (Is this structure the mother of the pinned-photodiode or buried diode or hole-accumulation device?)

Figure 3. Cross section of a buried-channel CCD on n-Si substrate including light windows and pinned interface potential in the non-covered CCD channels (the cross section is made perpendicular to the CCD channel).

73

[2] Y. Daimon-Hagiwara et.al., Proc. 10th Conf. on Solid-State Devices, Tokyo, 1978, pp.335-340.

## Fossum insulted in his 2014 paper Sony and Hagiwara 1975 PPD invention.

Indeed, Hagiwara invented PPD with VOD and the virtual charge transfer in 1975!!

IEEE JOURNAL OF THE ELECTRON DEVICES SOCIETY, VOL. 2, NO. 3, MAY 2014

## Sony HAD (PPD+VOD) does not use LOCOS !!!

A Review of the Pinned Photodiode for CCD and CMOS Image Sensors

Eric R. Fossum, Fellow, IEEE, and Donald B. Hondongwa, Student Member, IEEE

### Many people now said this is a fake paper!

C. Other Contributions to the PPD Invention

The PPD structure, while invented for low lag ILT CCD application, shares a strong resemblance to the Hynecek virtualphase CCD structure, with the exception of the VOD. The two inventions were solving different problems with essentially the same device structure and operating principles.

In 1975, Hagiwara at Sony filed a patent application on bipolar structures for CCDs in which a pnp vertical structure was disclosed, among several structures [24]. The top p layer was connected by metal to a bias used to control full-well capacity and the n-type base layer was proposed for carrier storage. In an unusual paper, Hagiwara, in 1996, revisited the 1975 invention and claimed it was essentially the invention of both the virtual phase CCD and the NEC low-lag structures, as well as the basis of the Sony so-called "Hole Accumulation Diode," or HAD structure [25]. However, the 1975 application

False

properties found in the NEC low-lag device, and does not seem to contain the built-in potential step and charge transfer device aspects of the virtual-phase CCD. Hagiwara repeats these claims in a 2001 paper [26] and shows a VOD structure that is not found in the 1975 patent application. Sony did not seem to pursue the HAD structure until well after the

NEC paper was published. However, the "narrow-gate" CCD with an open p-type surface region for improved QE also disclosed in the 1975 application was reported in more detail by Hagiwara et al. at Sony in 1978 [27]. A similar structure was used extensively by Philips [28].

The PPD, as it is most commonly used today, bears the strongest resemblance to the Teranishi et al. ILT CCD device. Thus, these days Teranishi is considered as the primary inventor of the modern PPD [29].

The surface P+ layer is NOT connected to the LOCOS P+ layer.

The surface P+ layer may be floating and this photodiode may have serious image lag.

74

Hagiwara in 1975 invented PPD with VOD and the virtual charge transfer. Study the Japanese Patents 1975-127646, 1975-127647 and 1975-134985.

### Difference between Buried Photodiode and Pinned Photodiode

What is the difference between Buried Photodiode and Pinned Photodiode? I understand that the P+/N/P structure where the P+ and P layers have the same potential is the Pinned Photodiode. So what is the buried Photodiode?

https://electronics.stackexchange.com/questions/83018/difference-between-buried-photodiode-and-pinned-photodiode

This is a commonly misunderstood misused set of terminologies.

First off these are not PIN Photodiodes - which stands for P - Intrinsic- N. These have large depletion regions for higher internal QE (Quantum Efficiency) and faster response. You can't make an array with this design though.

Pinning, refers to fermi-level pinning or pinning to a certain voltage level. Or also the forcing or prevention of the fermi-level/voltage from moving in energy space.

You can get surface state pinning from the dangling Si/SiO2 bonds providing trapping centers. A buried PD (Photodiode) has a shallow implant that forces the charge carriers away from these surface traps. The Si/SiO2 surface contributes to increased leakage (dark current) and noise (particularly 1/f noise from trapping/de-trapping). So confusingly a buried PD avoids pinning of the fermi-level at the surface.

A pinned PD is by necessity a buried PD, but not all buried PD's are pinned. The first Pinned PD was invented by Hagiwara at Sony and is used in ILT CCD PD's, these same PD's and the principles behind this complete transfer of charge are used in most CMOS imagers built today.

A pinned PD is designed to have the collection region deplete out when reset. AS the PD depletes it becomes disconnected from the readout circuit and if designed properly will drain all charge out of the collection region (accomplishing complete charge transfer). An interesting side effect is that the capacitance of the PD drops to effectively zero and therefore the KTC noise  $q_n = sqrt(KTC)$  also goes to zero. When you design the depletion of the PD to deplete at a certain voltage you are pinning that PD to that voltage. That is where the term comes from.

I've edited this Answer to acknowledge Hagiwara-san's contribution. It has long been incorrectly attributed to Teranishi and to Fossum (in CMOS image sensors)

In 1975 the first PPD was invented by Hagiwara at Sony and used in ILT CCD PDs by Hamazaki at Sony in 1987.

PPD must have the P+ channel stops nearby to pin the surface P+ layer.

### Semiconductor History Museum of Japan

### https://www.shmj.or.jp/english/pdf/dis/exhibi1005E.pdf

In 1975, Sony proposed using a PNP transistor as the photodetector [3]. By providing a P + layer (emitter) for the light incident section, the sensor electrode that covers the entire light receiving surface of the photodiode can be eliminated, greatly improving the light sensitivity. This P + layer was also a proposal to reduce the dark current and image lag which became the basis of the pinned photodiode.

In 1978, Sony presented a 93,000-pixel FT (Frame Transfer) -CCD image sensor compliant with the Analog TV Broadcasting Standard (SDTV) for the first time in the world [5], using the photodiode with the same structure as above. Sony succeeded in 1981 in trial production of a VTR-integrated color movie camera using a 2 / 3-inch 280,000-pixel FT-CCD image sensor by further improvement of this technology [6].

The Pinned Photodiode is a photodiode in which the entire N layer is covered with a P layer. The part of the P layer on the light incident surface is heavily doped P+ (Fig-1). Kodak named this structure Pinned Photodiode in 1984 because the P + surface of the light incident surface was pinned to the substrate potential. This device has features such as high light sensitivity, wide dynamic range, image lag free, much smaller dark current due to reduced influence of GR center on the light receiving surface, and no white scars.

Pinned Photodiode reported at SSDM 1978

#### References:

- [1] M. Hamasaki, T. Suzuki, Y. Kagawa, K. Ishikawa, K. Miyata and H. Kambe, "An IT-CCD imager with electronically variable shutter speed", Technical Report of The Institute of Image Information and Television Engineers. vol. 12, no. 12, pp. 31-36, (1988)

- [3] Y. Hagiwara, Japanese Patent JP1975-134985

- [5] Y. Hagiwara, M. Abe, and C. Okada, "A 380H x 488V CCD imager with narrow channel transfer gates", Proc. The 10th Conference on Solid State Devices, Tokyo, (1978): Japanese Journal of Applied Physics, vol. 18, Supplements 18-1, pp. 335-340, (1979)

- [6] I. Kajino, M. Shimada, Y. Nakada, Y. Hirata and Y. Hagiwara, "Single Chip Color Camera Using Narrow channel CCD Imager with Over Flow Drain", Technical Report of The Institute of Image Information and Television Engineers, vol. 5, no. 29, pp.

77

Japanese | English

### Sony's Representative Inventions Supporting Stacked Multi-Functional CMOS Image Sensors

Sony Corporation Sony Semiconductor Solutions Corporation

## https://www.sony.net/SonyInfo/News/notice/20200626/

### Pinned Photodiode Adopted for Back-Illuminated CMOS Image Sensors

The history of Sony's inventions of image sensors goes back to the CCD era. Above all, Pinned Photodiode is a technology that contributes to improving the performance of back-illuminated CMOS image sensors, and the history of inventions and product development are as below.

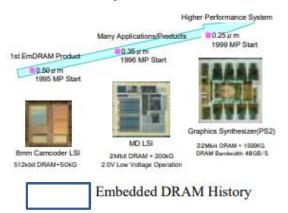

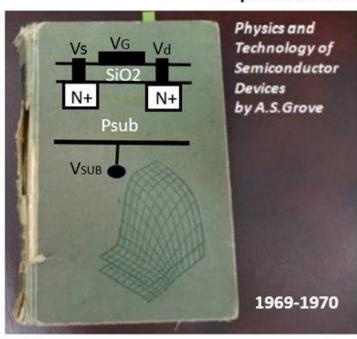

In 1975, Sony invented a CCD image sensor that adopted a back-illuminated N+NP+N junction type and an N+NP+NP junction type Pinned Photodiode (PPD) (Japanese patent application number 1975-127646, 1975-127647 Yoshiaki Haqiwara). In the same year, inspired by such structure, Sony invented a PNP junction type PPD with VOD (vertical overflow drain) function (Japanese Patent No. 1215101 Yoshiaki Haqiwara). After that, Sony succeeded in making a principle prototype of a frame transfer CCD image sensor that adopted the PNP junction type PPD technology, having a high-impurity-concentration P+ channel stop region formed near a light receiving section by ion implantation technology for the first time in the world, and its technical paper was presented at the academic conference, SSDM 1978 (Y. Hagiwara, M. Abe, and C. Okada, "A 380H x 488V CCD imager with narrow channel transfer gates", Proc. The 10th Conference on Solid State Devices, Tokyo, (1978)). In 1980, Sony succeeded in making a camera integrated VTR which incorporated a one-chip frame transfer CCD image sensor that adopted the PNP junction type PPD. President Iwama in Tokyo, Chairperson Morita in New York, at the time held a press conference respectively on the same day, which surprised the world. In 1987, Sony succeeded in developing a 8 mm video camcorder that adopted, for the first time in the world, the interline transfer CCD image sensor, which incorporated "PPD having a high-impurity-concentration P+ channel stop region formed near the light receiving section by ion implantation technology" with VOD function, and became the pioneer of the video camera market. The PPD technology that has been nurtured through such a long history is still used in back-illuminated CMOS image sensors.

#### References

- [1] M. Hamasaki, T. Suzuki, Y. Kagawa, K. Ishikawa, K. Miyata and H. Kambe, "An IT-CCD imager with electronically variable shutter speed", Technical Report of The Institute of Image Information and Television Engineers. vol. 12, no. 12, pp. 31-36, (1988)

- [3] Y. Hagiwara, Japanese Patent JP1975—134985

- [5] Y. Hagiwara, M. Abe, and C. Okada, "A 380H x 488V CCD imager with narrow channel transfer gates", Proc. The 10th Conference on Solid State Devices, Tokyo, (1978): Japanese Journal of Applied Physics, vol. 18, Supplements 18-1, pp. 335-340, (1979)

- [6] I. Kajino, M. Shimada, Y. Nakada, Y. Hirata and Y. Hagiwara, "Single Chip Color Camera Using Narrow channel CCD Imager with Over Flow Drain", Technical Report of The Institute of Image Information and Television Engineers, vol. 5, no. 29, pp.

International Solid State Circuits Conference 1954-2013

Image Sensor Story

78

79

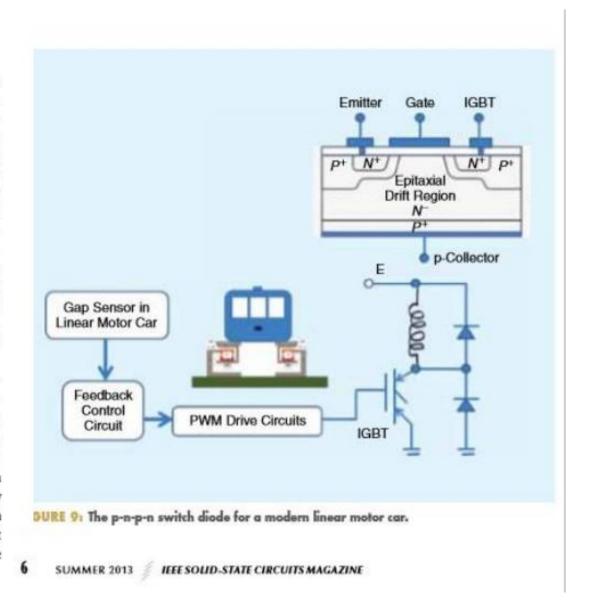

### Yoshiaki Higihara: The p-n-p-n Diode in Future Linear Motor Cars and in Modern Imagers

John Louis Moll (1921-2011) was studying a p-n-p-n diode switch in his Ph.D. dissertation work when the first ISSCC was held in 1954. In a normal operation mode, this device works as a thyristor, which can drive a large current and is the key device structure of an IGBT applied for a linear motor car of the future (see Figure 9). In a dynamic operation mode, this device may work as a simple p-n-p-n dynamic capacitance that can detect and store one single electron, which is a key device structure of the modern image sensor (see Figure 10).

I recall, when I was taking his physics course at Caltech, that Feynman once said that an electron is always free, moving around rapidly in free space, even in solid, and it never stops. It is very hard to catch an electron because we do not know exactly where it is. Our civilization today is based on a technology that controls electrons, down to a single one.

80

Imagine a photon incident to a bipolar transistor base region. The photon energy creates an electronhole pair. And the photo-electron can be stored in the base region as one single majority carrier. That is, a bipolar transistor can also function as a photon detector and/or a storage container. I thought that a room in a hotel must be empty and clean before the first hotel guest arrives. So must be this transistor base region empty and clean with no guest electrons at the beginning. This transistor in a dynamic p-n-p capacitor mode is useful since it can capture, confine, and control one single electron. But as a student, I did not know yet how to student, I did not know yet how to move that single photoelectron sitting in the base region to the outside world so that we can make use of it as a signal. I had no way yet to know whether the hotel guest has arrived and is resting in the hotel room or not. We had no way yet to ask the hotel guest to come up to the hotel lobby to meet me. I had to wait a few more years (until 1970

FIGURE 10: From CCD to the dynamic p-n-p-n diode capacitors.

in my senior year in college) to find the answer. We all know now it is the CCD structure that can store and transfer one single electron. With a precharge reset set gate and

With a precharge reset set gate and a source-follower circuit, a scheme invented by Walter Kosonocky. We could finally meet our hotel guest at the hotel lobby.

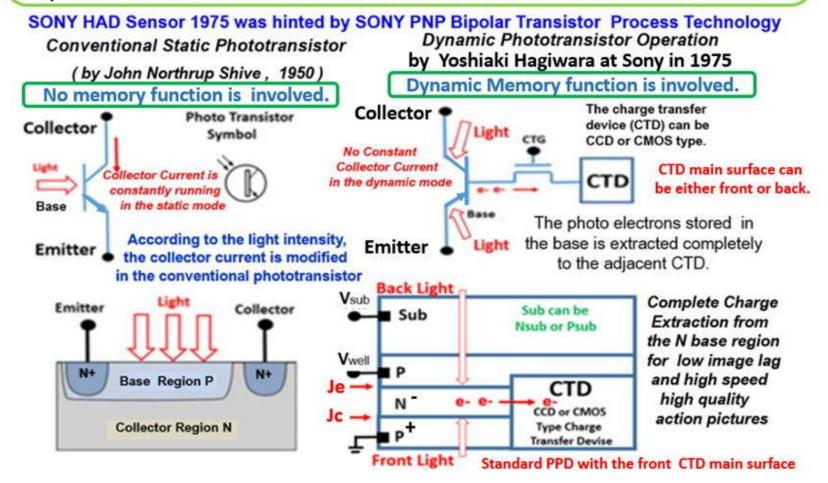

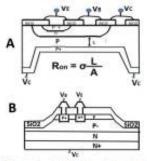

## History of dynamic Solid State image sensing structure from BCCD type MOS capacitor to the P+NPN junction Pinned Photodiode capacitor

(1) CCD type invented by Bell Lab in 1968 (2) N+P type

The classical photodiode with serious image lag

(3) P+NP type (4) P+NPN type

(3) and (4) are the P+NP junction type Pinned Photodiode invented by Yoshiaki Hagiwara, 1975

In Japanese patent 1975-134985, Hagiwara at Sony invented the Pinned photodiode with very low dark current, which is also the completely depleted Buried Photodiode with image lag free picture quality, and also with the built-in vertical overflow drain ( VOD ) function.

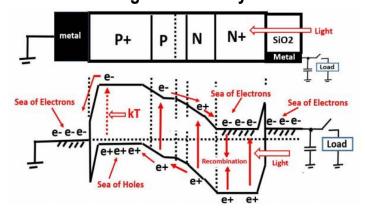

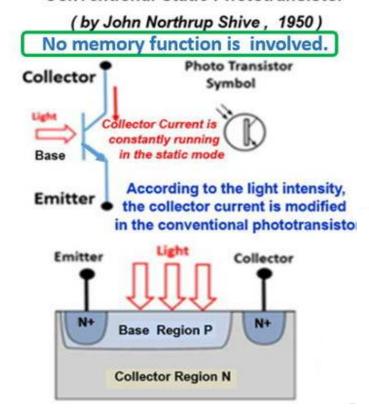

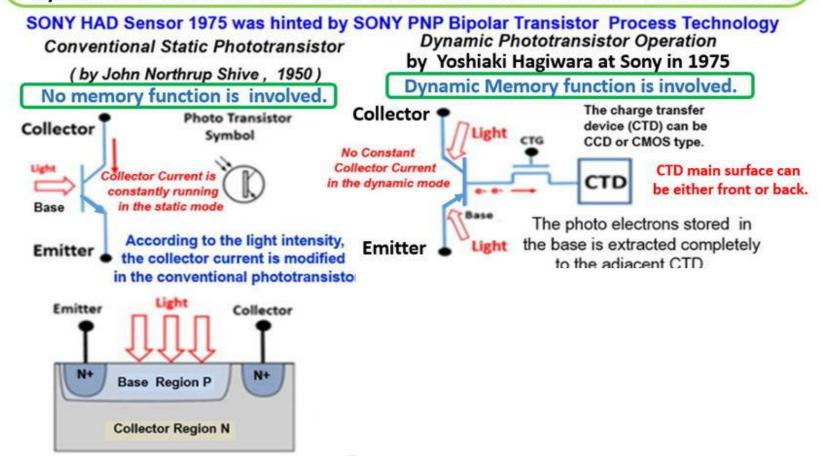

Sony Hole Accumulation Diode (HAD) is the P+NPNsub junction dynamic photo transistor with the surface P+ hole collecting and accumulation region is pinned and grounded, which is now widely called as Pinned Photodiode with the vertical overflow drain (VOD) function. Only Pinned Photodiode with the VOD function can realize the electrical shutter function.

SONY HAD Sensor 1975 was hinted by SONY PNP Bipolar Transistor Process Technology

Sony Hole Accumulation Diode (HAD) is the P+NPNsub junction dynamic photo transistor with the surface P+ hole collecting and accumulation region is pinned and grounded, which is now widely called as Pinned Photodiode with the vertical overflow drain (VOD) function. Only Pinned Photodiode with the VOD function can realize the electrical shutter function.

SONY HAD Sensor 1975 was hinted by SONY PNP Bipolar Transistor Process Technology Conventional Static Phototransistor

Image Sensor Story

84

Sony Hole Accumulation Diode (HAD) is the P+NPNsub junction dynamic photo transistor with the surface P+ hole collecting and accumulation region is pinned and grounded, which is now widely called as Pinned Photodiode with the vertical overflow drain (VOD) function. Only Pinned Photodiode with the VOD function can realize the electrical shutter function.

Image Sensor Story

85

Sony Hole Accumulation Diode (HAD) is the P+NPNsub junction dynamic photo transistor with the surface P+ hole collecting and accumulation region is pinned and grounded, which is now widely called as Pinned Photodiode with the vertical overflow drain (VOD) function. Only Pinned Photodiode with the VOD function can realize the electrical shutter function.

Image Sensor Story

87

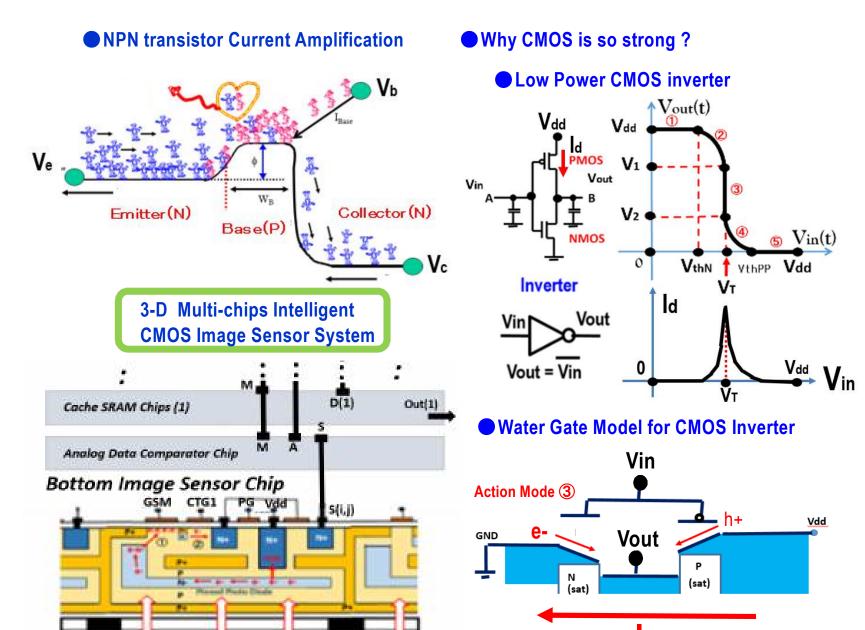

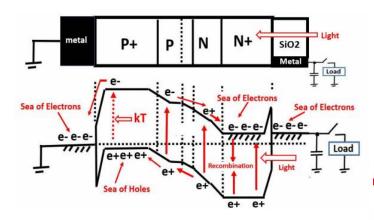

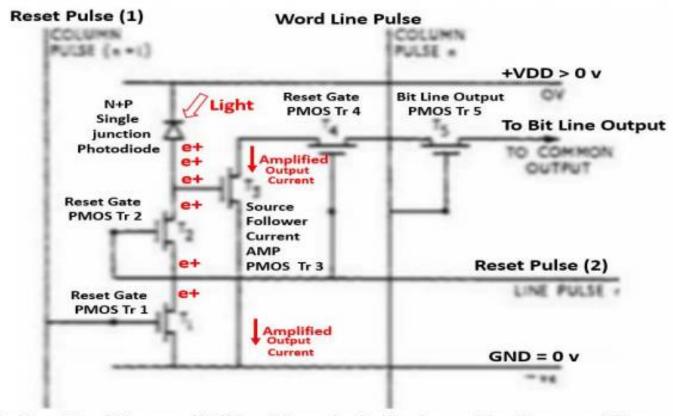

### NPN transistor Current Amplification

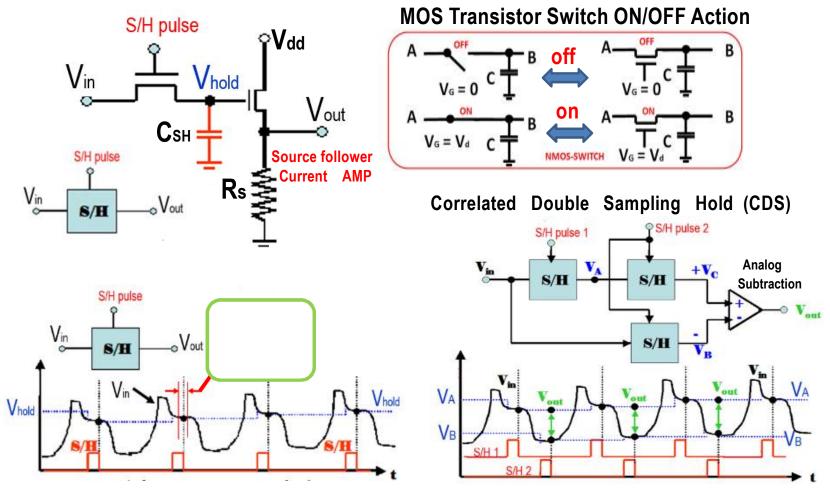

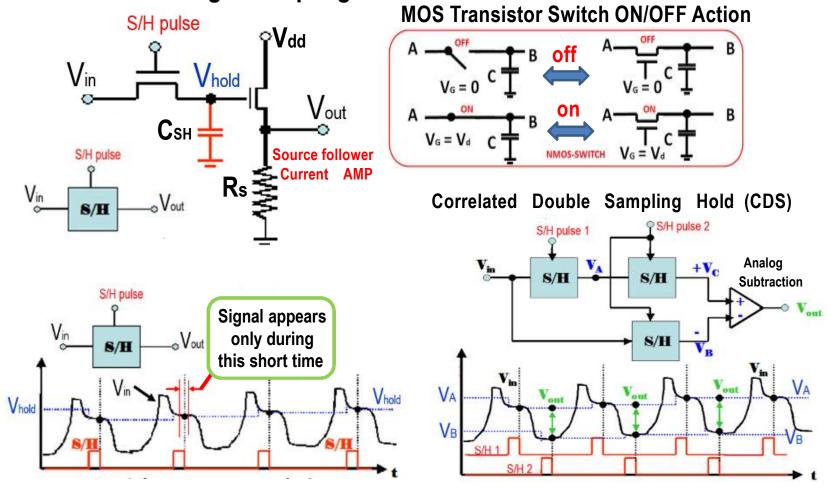

## **Correlated Double Sampling Hold by Prof. M. White, 1972**

## **Conventional Single Sampling Hold**

Image Sensor Signals are buried in the clock noises.

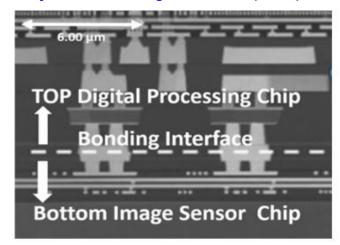

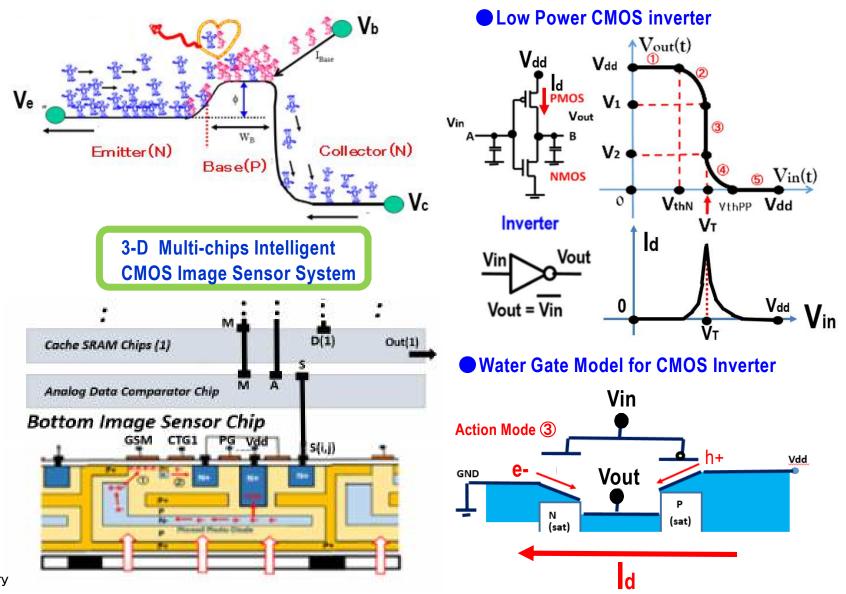

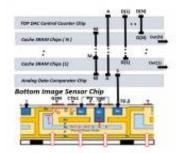

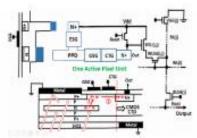

### Multichip CMOS Image Sensor Structure for Flash Image Acquisition

Yashiski Hagiwara

Artificial Intelligent Partner Laboratory

Attugi-city, Japan

hagiwara-yoshiski (ijaiplah com

Abstract — A new 3D Finned Photodinde (HAD) CMOS image sensor structure applied in the 3-Dimensional multichip high speed digital flash image data acquisition system is explained and the important features are discussed.

Keywords— Coche SRAM, ADC, Pinned Photodiode, Depletion Photodiode, Baried Photodiode, Back Light Illumination, Global Shutter Buffer Memory, In-pixel Three Transistor Currons Source Amplifier.

#### 1. Beneattee move

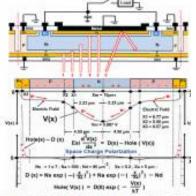

Basically there are five types of photodiode. They are (1) Classic N-Psub jurction with serious image by problem (2) PNPsub jurction Buried Photodiode (3) PN-Psub jurction Depletion Photodiode with the facely doped Psurface Insend Photodiode with the heavily doped Psurface hole accumulation with no serface dark current feature and (5) P-N-Psub junction type hole accumulation with no serface dark current feature and (5) P-N-Psub junction type hole accumulation dode (HAD) with the vertical overflow dram (VOD) function which is by necessity Buried, Depletion and Pinnad Photodiode (Fig. 1 shows the 3D milliothip CMOS image sensor structure with the 3D Panned Photodiode (HAD) image sensors with the MOS capacier Global Shutter Buffer Memany (GSBM) which was originally reverted in 1975.

Fig.1. Cross Section of Buried Depletion Pinned Photodode stacked with two Global Shatter Buffer Memory (GSBM) and CTG stages in two chip configuration for synchronizing data transfer to the receiving ADC and Cache SRAM chips

#### II. HOLE ROLE IN PINNED PHOTODIODE

The importance of hules in the hole accumulation byer HAD structure of Pinnell Photodiode was first reported in Hagiroura 1978 paper<sup>2</sup>, and then explained in details by Theravisien<sup>3</sup> in relationship with IDEM/1982<sup>2</sup> paper and IEDM/1982<sup>4</sup> paper. Today's success of super light sensitive digital imaging in based on the SiO2 exposed printed window invented by Hagiroura in 1975<sup>3</sup> with the surface Phole accumulation HAD layer. Printed Photodiode was originally invented<sup>3</sup> in the Sens of the back illumination scheme as libratized in Fig. 2.

Fig. 2: The P+PNP junction type Buried Depletion Pinned Photodiode with no image lag feature with MOS Capacitor type Global Shatter Baffer Memory (GSBM) invented and defined in Japanese 1975 patent by Hagiwara.

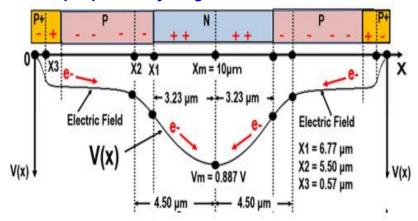

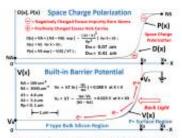

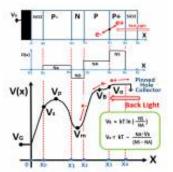

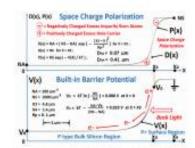

Fig. 3: Exact numerical calculations of Gaussian P+P depung profile D(x), the hole carrier density P(x) and the built-in harner potential V(x).

#### III. ROLE OF BUILT-IN POTENTAL BARRER IN HAD

Exact numerical calculation of the built-in potential hurrier is shown in Fig.3, explaining the hole electron generation and separation in the built-in electric field created by the heavily doped P+ surface bule accumulation HAD.

Note that the local unbalance of the hole concentration P(x) and the impurity botton atom density D(x) gives the local space change polarization, resulting the built-in potential V<sub>m</sub>. The built-in electric field separates photo electron hole pairs, and resulting in the excellent quantum efficiency of the short wave blac light seministrity.

Although CCD was just a charge transfer device (CTD), later taken over by CMOS type CTD, both CCD and CMOS strauge semest have the super ensitive light detecting feature with very good color reproduction at low light level because of the Firneal Pheedwided which was invented and described in Japanese 1975 patient by Hagiwara.

In solar cells and image sensors, the photo electron and hole pur generation is considered to occur normally in the PN junction depletion region. However, the photo electron and hole pair generation in Pinned Photodiode is performed by an entire different physical principle. In 1975, Haginean proposed that the photo electron and hole pair separation can also be achieved in the strong electric field created by the built-in barrier potential as shown in Fig. 2. that was the result of space charge polarization effect explained in Fig. 3.

Photo electrons are separated from holes in the presence of sendace P+ hole accumulation HAD layer. And then, photogenerated electrons can drift towards Burnel Photoshole, which is the charge collecting stonage, by using the holes, that in, positively charged Scient attents, as stepping stones, from one Si atom to another, like an energetic space necket until it loses energy. If the photo electron, generated at the surface built-in potential barrier electric field, in recombined with a hole drifting deep in the bulk silices, the hole becomes a neutral silicen atom that cannot move. Then, by the silicon bulk thermal manufality condition, the excess negative space charge is present in the form of the trapped electron by the regulatorly charged boron or in the external solution to the neutral silicen and a bigh energy state.

The electron has high energy state and can jump out into the ce space. In this very, the excess negative charged electron cannot stay in the neutral silicon atom permanently and can be transferred in the positively charged silicon atom (hole) nearby, acting as stepping stones for the excess electron charge, eventually to drift towards the receiving fluried N type charge collecting region. Eventually the excess electron negative charge is collected in the buried N type diffusion storage region. If the electric field of the PN purchion depletion region edge of the hursed photochode in near the serface PP hole accumulation edge, the drifting plots electrons can be quickly and instantly collected in the buried N type charge collecting storage area.

#### IV. VIRTICAL OVERFLOW DRAIN (VOD) PUNCTION

Fig. 4 shows Penned Photodiside with the vertical overflow drain (VOD), which is also Deplotion Photodiside with no image lag feature. The following is the direct English translation of the Patent Claim of the Japanese 1975 patent<sup>2</sup> on Pinned Photodiside (HAD) invented by Hagiware.

- In the substrate, the first region P1 of the first impurity type is formed, on which, the second region N2 of the second impurity type is formed.

- The charge e- from the light collecting part is transferred to the adjacent charge transfer device (CTD). Both are placed along the main surface of the correspondence substitute.

- In the solid stare image sensor so defined, a rectifying junction. Je is formed on the second light collecting region N2 forming the P3 and N2 junction as the emitter junction Je.

- 4. The result is a photo transistor P3N2PI structure on the substrate with the N2 and P1 junction as the collector junction Re. The charge, stored in the base N2 region according to the illuminated light intensity, is transferred to the adjacent charge transfer device.

Fig. 4: The P+NPNish junction type Hole Accumulation Diode (HADF invented by Hagowara in 1975.

978-1-7281-4870-0/19/830 309/2009 EEE

Fig. 5. Reproduction of figures reported in Hagiwara 1978 paper<sup>2</sup>, (A) P+NPsub junction type Finned Photedode structure, (B) the Excellent Blue Light Sensitivity (C) no dark current feature and (D) no image lag feature.

It is now well understood that the blue light of short wave length in needed for the satinfactory color reproduction of high irrage quality. However, the blue light cannot penetrate more than 0.5 micro mater in depth thru the silican reystal. The bush-in surface potential barrier, created by the surface abrapt deeping level difference, can in octurn create the atrong electric field at the vicinity of the electron hele pair generation at the silicent surface of 0.3 micro meter in depth, which can effectively separate photo electron and hole pairs, resulting in the excellent quantum efficiency for the blue light needed for the satisfactory color reproduction.

P+NP junction type Pinned Photodiode(A) has the following three very important features, (B) Excellent short wave blue fight quantum efficiency, which is the most important feature of Hagiroura 1975 patent\*, (C) no surface dark current problem and (D) no image lag problem, with also the feature of no surface interface trap (Nos) noise (E). But nothing is new about the feature (D) and (E) since CCD had these two features already by 1975.

In 1966, the in-pixel active source follower amplifier corcuit for MOS image sensors was invented by Perter Noble See Fig. 6.

Fig. 6: In-pixel amplifier circuit by Peter Noble, 1966

Fig. 7. Bispolar Transistor Process invented and developed by Yoshiyuki Kawana (A) and Toshio Kato (B) in 1950s.

But MOS scaling technology was not so advanced and the CCD type change transfer device (CTD) was preferred imply because MOS transitions were too large. However, CCD imager process shown in Fig. 4 was not as simple as MOS process for digital circuits. Compiles bipolar transistir process experience was required. See Fig. 7. But now, owing to the advancement of CMOS process scaling, the active circuit of Fig. 6 became the most important element needed to build the modern CMOS image sensors.

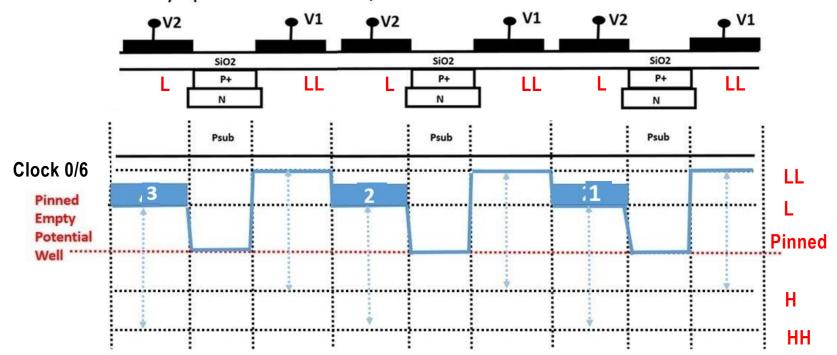

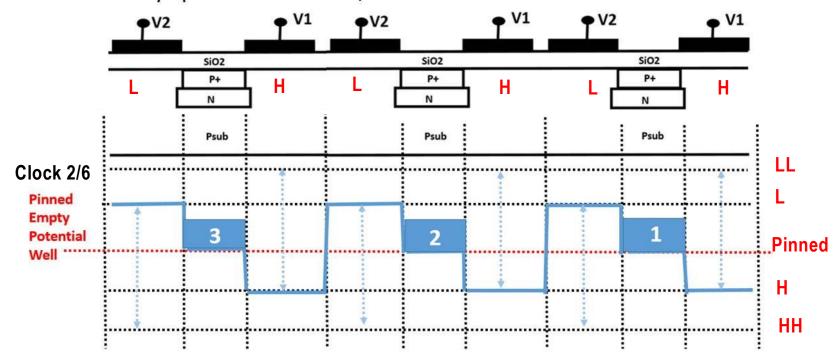

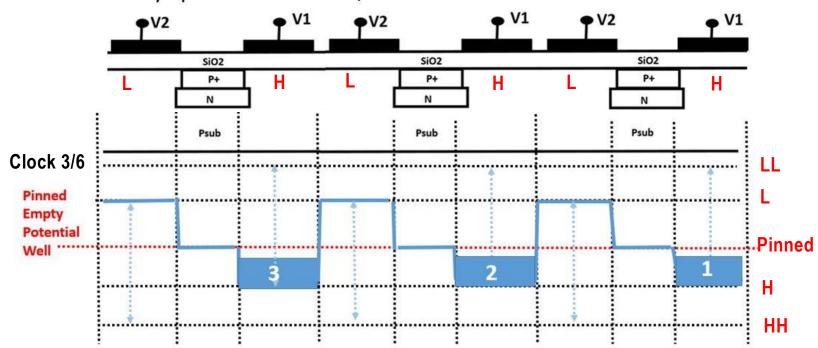

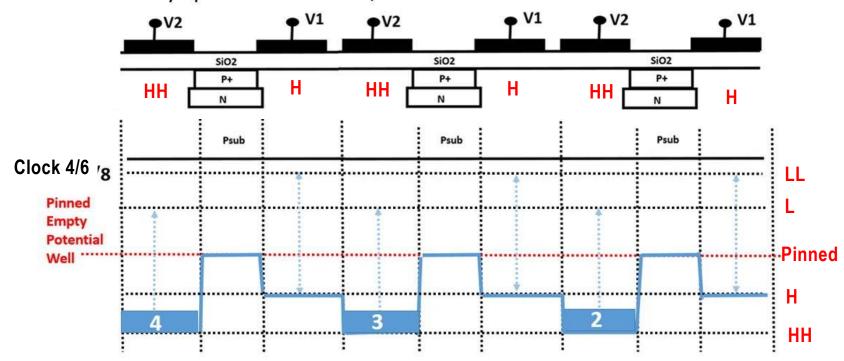

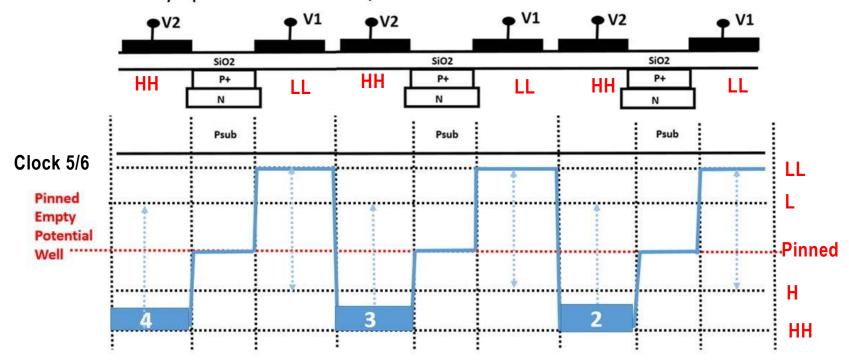

#### V. NPN JUNCTION CHARGE TRANSFER GATING (CTG)

Fig. 8 is a reproduction of the picture drawn in the 1975 patent<sup>10</sup> by Hagouars. This charge transfer action is very miritar to the well-known purch thro operation mode of the PNPN junction thyristen. Note that this is very similar to the PNPNs punction type Princed Photodiode shown in Fig. 4. Both are the same PNPN junction type Princed Photodiode.

Fig. 8: The P+PNPN junction type Pinned Photodiode<sup>20</sup> with Global Shatter MOS Buffer Memory (GSBM) and the NPN junction type vertical charge transfer gating (CTG).

Fig.9. The important concept of Virtual Phase Charge Transfer of the Pinised Photodiode with the complete charge transfer operation mode for no image lag feature, described and invented by Hagiroura 1975 patents<sup>1, to 10, 11</sup>

#### VI. PINNED SURFACE VIRTUAL CHARGE TRANSFER

The charge transfer operation with the pinned surface potential for the virtual gating concept is very similar to fite CCD charge transfer operation. Fig. 9 shows the virtual charge transfer concept explained by Hagiwam <sup>(a)</sup> in 1975. Hencock<sup>(a)</sup> invented an additional potential batter or stage to achieve the directionality of the virtual phase signal charge transfer operation, which was hinted by Hagiwara 1975 invention<sup>a</sup> and fite virtual phase charge transfer operation of the tronge lag free Printed Photododed: a solution in Sultania Physical Physical

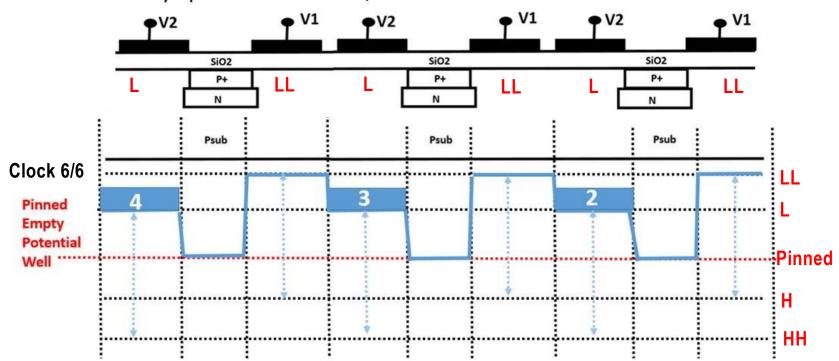

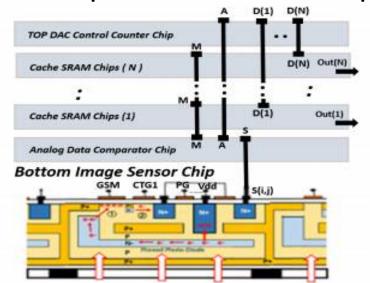

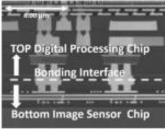

Fig. 10: Cross sectional photos of CMOS image sensors

Fig. 11: Metal Cu pillar signal pass wires thru multichip for the future 3D multichip flash image acquisition system.

#### VII. 3D MULTICHP IMAGE SENSOR SYSTEM

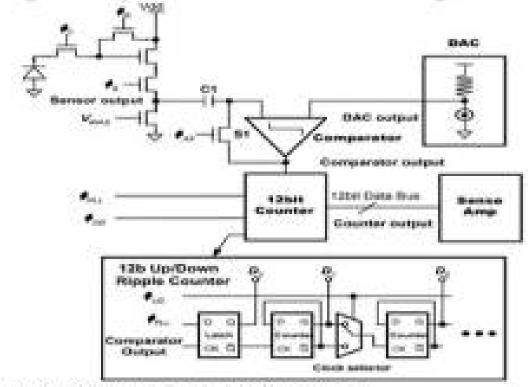

Cross sectional photos of back light illuminated CMOS image somers are shown in Fig. 10 whale Fig. 11 shows the 3D multichip CMOS image sensor system. If time sharing scheme is used, we only need one data comparator circuit. However, for fast ADC operations, we must have the inpact data comparator circuit sharing the comparator circuit is a conventional one that can also be used for a simple IR sensor detector as shown in Fig. 12.

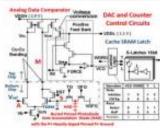

Fig. 12: Conventional Analog Data Comparator Circuit

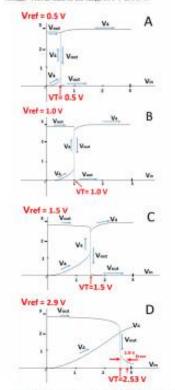

VIII CIRCUIT SIMULATION OF ANALOG DATA COMPATOR

Fig.13 summarized the circuit simulation of the analog data comparator for the various reference voltage. A in Fig. 11. The input voltage Vin which corresponds to the voltage A in Fig. 11. The input voltage Vin which corresponds to the output signal S in Fig.11 is scanned to obtain the value of the threshold voltage. VT, which corresponds to the match signal M in Fig.11. With this match signal M, the cache SRAM lackes the values of the centrol counter data D(1) in D(N) in each SRAM level chip. This simulation analysis shown the good circuit performance for the input reference voltage. Verf at least in the cange of O V to 1.5 V.

Fig. 13: the circuit simulation results of the analog data comparator for the various reference voltage Vief values

Fig. 14: Cross Sectional View of two chip stacked backilluminated CMOS Image Sensor's with the in-pixel analog comparator control circuits to generate the match signal M from the reference voltage A and the image sensor signal S.

#### EX. ALL SOLID STATE DIGITAL CAMERA

The 25 transsecond access time fast Cache 4 Mega Bit SRAM<sup>11</sup> was first developed in 1989, with the dynamic bit line load circuits inserted by Miraga, and was used as the very fast Digital Buffer Memory for the early all solid state digital CCD camera to cornect and enhance the picture quality such as Jitte correction, color reproduction, pattern correction and image recognition processing system units for inflastrial and predictional applications of high definition television broadcasting level.

Fig. 14 shows the cross sectional view of two chip stacked back-illuminated CMOS image sensor<sup>18 th</sup> with the in-pixel making computator control circuits to generate the match signal M from the reference voltage A and the image sensor signal S, as originally illustrated in Fig. 11 for the future multichip system.

Photo election and hole generation and separation at the surface electric field is performed at the back side allicon surface of the P+ heavily doped pinned hole accumulation (HAD) layer acting as the Pinned Hole Collector Geounded Terminal. Salient physical parameters are defined in Fig. 15. The all solid state CMOS image sensor technology in now being extended to the 3D multichip flash image acquinition system illustrated in Fig. 1 and Fig. 11.

#### VIII CIRCUIT SIMULATION OF ANALOG DATA COMPATOR.

30 02019 4017

Fig.13 numerative of the circuit simulation of the maling data comparative for the various reference voltage. Verf values which correspond to the voltage A in Fig. 11. The input voltage Vin which corresponds to the output signal S in Fig.11 is scanned to obtain the value of the threshold voltage. VT, which corresponds to the match signal M in Fig.11. With this match signal M, the cache SRAM latches the values of the control constend that D(1) to D(N) in each SRAM level chip. This simulation analysis shows the good circuit performance for the input reference voltage. Verd at least in the range of 0 V to 1.5 V.

Fig.13: the circuit simulation results of the analog data comparator for the various reference voltage Vief values

Fig. 14: Cross Sectional View of two chip stacked backilluminated CMOS Image Sensor<sup>11</sup> with the in-pixel studies comparator control executs to generate the match signal M from the reference voltage A and the image sensor signal S.

#### DK. ALL SOLID STATE DIGITAL CAMERA

The 25 nanosecord access time fast Cache 4 Mega Bit SRAM<sup>11</sup> was first developed in 1989, with the dynamic bit line load circuits invented by Mynga, and was used as the very fast Digital Buffer Memory for the early all solid state digital CCD carriers to correct and enhance the picture quality such as Jitter correction, color reproduction, pattern correction and image recognition processing system units for industrial and professional applications of high definition television broadcasting level.

Fig. 14 shows the cross sectional view of two chip stacked back-illuminated CMOS image sensor<sup>18,18</sup> with the in-pixel making companions control careatis to generate the match signal M from the reference voltage A and the image sensor signal S, so originally illustrated in Fig. 11 for the future multi-chip system.

Photo electron and hole genuration and separation at the surface electric field it performed at the back side silicon surface of the P+ heavily deped gimned hole accumulation (HAD) layer acting as the Panned Hole Collector Geouwhed Terminal, Salient physical parameters are defined in Fig. 15. The all solid state CMOS image sensor technology is now being extended to the 3D multi-rip flash image acquisition system illustrated in Fig. 1 and Fig. 11. 3D CXXXI ALL TO A STATE OF THE PROPERTY OF THE

VIII CIRCUIT SIMULATION OF ANALOG DATA COMPATOR

Fig.13 summarized the circuit simulation of the warding data comparator for the various reference voltage. Virtl' values which correspond to the voltage. A in Fig. 13. The input voltage Vin which corresponds to the output signal S in Fig.11 is scanned to obtain the value of the threshold voltage. VI, which corresponds to the match signal M in Fig.11. With this match signal M, the cache SRAM latches the values of the centrol contert data D(1) to D(N) in each SRAM level chip. This simulation analysis shows the good circuit performance for the input reference voltage. Viref at least in the cause of 0 V to 1.5 V.

Fig. 13: the circuit simulation results of the analog data comparator for the various reference voltage Vief values

Fig. 14. Cross Sectional View of two chip stacked backilluminated CMOS Image Senser<sup>11</sup> with the in-pixel analog comparator control circuits to generate the match signal M from the reference voltage A and the image sensor signal S.

#### EX. ALL SOLID STATE DIGITAL CAMERA

The 25 manesecond access time fast Cache 4 Mega Bit SRAM<sup>11</sup> was first developed in 1989, with the dynamic bit line lead circuits inserted by Mirags, and was used as the very fast Digital Buffer Memory for the early all solid state digital CCD camera to cornect and enhance the picture quality such as lifter correction, color reproduction, pattern correction and image recognition processing system units for influstrial and preferesional applications of high definition television broadcasting level.

Fig. 14 shows the cross sectional view of two chip stacked back-illuminated CMOS image sensor<sup>1 to</sup> with the in-pixel amiling comparator control circuits to generate the statch signal M from the reference voltage A and the image sensor signal S, so originally illustrated in Fig. 11 for the future multichip system.

Photo election and hole generation and separation at the surface electric field is performed at the back side allicon surface of the P+ heavily doped pinned hole accumulation (HAD) layer acting as the Pinned Hole Collector Geounded Germanal. Salient physical parameters are defined in Fig. 15. The all solid state CMOS image sensor technology in now being extended to the 2D multichip flash image acquinition system illustrated in Fig. 1 and Fig. 11.

Fig. 15: Electrostatic Analysis of the surface Built-in Barrier Potential Vs and V- by Depletion Approximation.

#### X. CONCLUSION

Hole Accumulation Diode<sup>6</sup> (HAD), with the P<sup>6</sup> heavily doped surface hole accumulation layer, invented in 1975, is very important, because first of all it has the excellent short wave length blue light sensitivity feature producing the high richare quality of color reproduction in low level light illumination, which is realized by the photo electron and hole pair generation and separation in the halft-in potential harmin and the electric field at the surface housely doped P<sup>6</sup>hole accumulation HAD. No dark current is the second important feature. And no image lag is the third one since CCD was known to have the no image lag feature abready. But CCD itself does NOT have the excellent blue light sensitivity and does NOT have the low dark current feature which the Panned Photodiode<sup>1,2,6,10</sup> invented by Hagowara has.

HAD is defined as the PNPN junction Photodiode with the VOD function. HAD is also by necessity the P+N-P junction Pinsed Photodiode with no dark current feature. HAD is also by necessity the PN-P junction Depletion Photodiode defined as Buried Photodiode with no image lag feature. When Hagiwara invented HAD12418 in 1975 Hantware also invented (1) Pinned Photodiode<sup>a</sup> (2) Depletion Photodiode (3) Buried Photodiode (4) the inpixel vertical overflow drain\* (VOD) function and (5) the m-pixel Global Shutter function. The surface pinned potential<sup>1, 4, 18</sup> also serves as the hole collector terminal separating the holes from photo electrons which drift more than the distance estimated by Debye length until being collected into the Buried<sup>10</sup>, Depletion and Pinned Photodiode (HAD), with the back light illumination scheme which is the most important feature peoded to build the surser sensitive 3D CMOS image sensor with the high blue-light quantum efficiency and the excellent color reproduction at low light level for fast action pictures with no image lag.

Finure Al traffic control system will need at least the high definition 8K image format of 7080H x 4320V, with 33 million procks to obtain the details of flush action images, with the in-pixel flush AD convertien, and fast Cache SRAM chips in the 3D multichip CMOS image sensor with the more complex future digital circuit system amplementations of the human friendly artificial intelligent partner system." (AIPS) to realize the smart AI image sensors for the smart AI robot vision system and home AI sectisity and house cares.

#### Acknowledgment

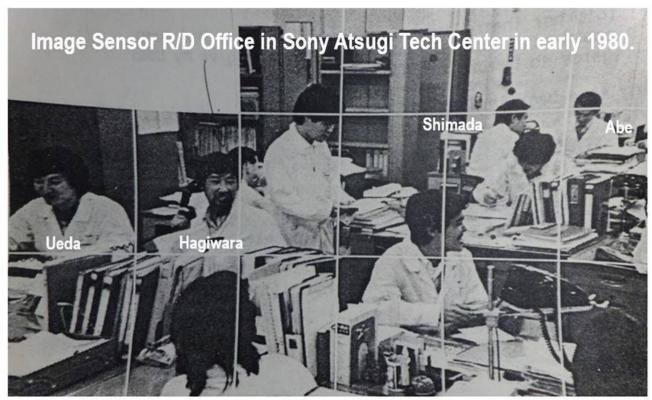

The author expresses sincere gratitude in Turushi Shimton, Yasuhim Ueda, Tadakani Narahu, Junya Sunski, Kato Toshis and Yoshiyuki Kawana, my dear friends and respecifid mentors throughout private and public life at Soare.

#### REFERENCES

- [1] Inparent 1975-12769? Patent, Elied on Oct 23, 1975 on Bushul Deprion and Pramad Phonalised with complem charge transfer and no large lag feature with MOS Capacitor type Global Sharter Budler Memory (CSIDM) features (notword by Yandash Haghwara in 1975.

- [2] Y. Damoo-Hagirura, M. Abe, and C. Okada, "A 200Ho-00IV CCD imager with survive channel massfer game, "Prox. of the 10th Conference on Solid State Devices, Tokye, 1878; Japanese J. Appl. Phys., vol. 18, oxpolement 19–1, pp. 335–340.

- [3] After Theoreteen, "The Hele Rale", IEDM2005, IEDM Technical Digest, Dec 2005

- [4] N. Temanishi et al., IEE061992 Tech. Digon, pp. 324-32 on Bartiel Photodiode with its image log. See also Japanese 1995-123259 paters: filed in 1999., Eled Inter than Japanese 1975-124995 paters in 1975.

- [5] R.C. Barkey et al., EDM Yachnical Digot, 1994, pp. 28-31 on Planed Phenodicals with the nations P+ hole accommission layer, a depicture device defined in the original. Japanese 1975-134995 parent.

- [6] Sapanese 1975-134985 Patent filed on New 10, 1975 on the P-NPNinch Buried Depletion and Primed Photodiode with the nurface P+ hole accentishation layer and the vertical overflow drain (VOD).

- [7] See Fig. 3, p.750, S. M. Soc, "Physics of Semiconductor Devices", 2nd Februar, Wiley.

- [8] K. Ishakama and T. Kratia, "One-reach 2M pixel CCD with Hyper SIAD summer and Camera Systems for HDFV", SPIE proc. Vol. 1656, pp.36–40, Folymany 1992.

- [9] K. Yosomoto and H. Sumi, "A CMOS litings Sensor with a Simple FPN Reduction Technology and a Hole Accumulation Deale", ISSCC2000, Digies of Technical Papers, pp.302–301, Edinary 2000.

- [16] Japanese 1975-127646 Patrial, Slad on Oct 23, 2975 on the P-NPN parties type Baried, Depletion and Primed Percedicule with the in-pixel MOG capation type buffer namony and the vertical NPN parties type charge transfer gaing (CTG) Set Global Shutter executive solution.

- [13] Y. Hagiwara, "High-density and high-quality frame transfer CCD imager with very low smart, low dark current and very high blass wealth'sis," EEE Train. Electron Deviate, vol. 43, no. 12, pp. 2122–2130. Doc. 1996.

- [12] J. Blyacck, "Virtal plane CCD technology," in Proc. IEDM1979, pp. 613–614 Dec. 1979.

- [13] Famio Mhaji, Yasuch Mattayana, Yoshikam Kanaishi, Kanasuri Suodi, Takashi Enson and Yoshishi Hagisura, "A 25 nanosu: 4 Maga Int CMOSRAM with Dynasics Ros-Line Leads", ISSCC1990 and J Solid State Circuits, VoDA, No.5, Certifier 1998.

- [14] M. Sakakhan, et al, "A Back-thormood Gobal-Shanor CMOS longer Sensor with Picol-Parallel 14h Subbasshold ADC", ISSCC2018, Feb. 2018

- [15] V. Kartagai, et al, "Back-thoronous 2.74 int-Pixel-Pixel Gobal Shatar CMOS Image Server with Charge-Domain Memory Archiving 10t o- Struttino Signal." IEEM 2018. Doc 2018.

- [16] Y. Kagoria and H. Immoni, "3D Integration Technologies for Sucted CMOS Image Sources", an arcited paper at the IEEE 3DIC2009 conference, Oct 8, 2019, Soulai, Japan.

- [17] Vochaki Hagemen, "The World of Digital Creams the Artificial Intelligent Farmer Science (ASFST) published by Sciencela co.jp. in 2016, SENSYST-4-88539-1375-2, 450 pages, Hard Concer 9005year-tai.

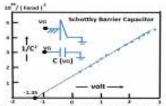

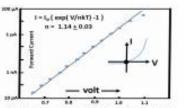

#### Simulation and Device Characterization of the P+PN+P Junction Type Pinned Photodiode and Schottky Barrier Photodiode

Vochiale Hagiwara

AIPS

Artificial Intelligent Partner Laboratory

Attags-city, Japan

hagiwara-yoshiale/jiapfab.com; +81-80-2062-5657

Abstract—Process parameter talerance of sentionalucine device is very impactant for measurfacturability and yield. Phinod Photodiode has by definition the pinned surface potential of the loss surface dark current feature and the pinned empty potential will of the no image be feature with the excellent blue light somitivity of the ideal quantum efficiency. This paper reports simulation and device characterization of the anique P-PN-P junction type Barried, Depletion and Planed Photodiode with evolution transferaturability, originally invented in 1978. Related various historical photodiode structures are reviewed, including the metal surfaceductor Schottley Barrier photosessor of Asi.

3. Gacth type in search for the law leakage and dark current photodiode which led the 1975 invention of the loss leakage P-NNP with junction Planed Photodiode by Bagivara.

Keywards—Baried Depletion Pinned Photodisde, builtin harrier potential, Hole Accumulation Diode (HAD), electron hole pair separation, built-in barrier potential

#### 1. INTRODUCTION

Many fatheres in device applications are related to loss of the device current blocking capability. The very loss reverse leakage current feathers of the commencially available. Therebelsed Schottky burnier crediter avoids, is a key guaranture for device performance, including the high performance required for the susper light sensitive, the low surface dark current and the low 1/1 noise image sensitive art very low light level with the low image lay feather.

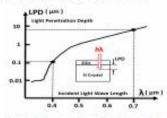

Fig. 1 shows the light penemation depth in the silicon crystal with respect to the incident light wave length. The maximum light penemation depth into the obscion-crystal is about 0.2 micro-meter for the obsci light of 0.4 micro-meter wave length and 37.6 eV photos energy while the light penemation depth in about 8 micro-meter for the red light of 0.7 micro-meter wave length and 12.3 eV photos energy. To achieve the boot color reproduction pieches quality for the CMCS image sensors we need a photochode which can convert the incident blue light energy into the electric energy very afficiently. Various types of photos sensors are compared in Fig. 2. The N/0<sup>4</sup> janction (type A) Lenks Diode has the two states, had and law carrent modes, on the forward bias Hostoner, it has a relative large leakage current in the reverse bias because both sides of the N<sup>4</sup> and P<sup>5</sup> regions are very much harsily doped.

Fig 1: Light Penetration Depth (LPD) in Silicon Crystal.

XXX-X-XXXX-XXXX-X-XXXXXX 00 02020 0300

Fig 2: various types of photo sensor structures.

Classical N+P praction type II photodiode is known to have the serious arrange lag problem. The type C Pinned Photodiode', evented in 1973 by Haghraux, has the pinned surface potential of the no leakage current former and the pinned empty potential of the no leakage current former and the pinned empty potential of the no image lag fination. See Fig. 3. As originally reported by Haghraux 1978 paper", the P+ surface HAD layer had the Gassian doping paolife with  $Q_0 = 2 \times 10^{14} \, \mathrm{cm^2}$  and No = 1 ×  $10^{14} \, \mathrm{cm^2}$  while the barried N sugion that  $M = 3 \times 10^{14} \, \mathrm{cm^2}$  and  $Q_0 = 1.7 \times 10^{12} \, \mathrm{cm^2}$  while the target N paper in the type D Pinned Photodiode has the unique beth-in barrier electric field, urbaneous the proposition at the surface of the silicon crystal for the short wave length this light.

Fig 3: Features of P+PN junction type Pinned Photodiode

2020 Electron Devices Technology and Manufacturing Confessors (EDTM)

Fig. 4. Exact numerical calculations of Gaussian P+P doping, profile D(x), the hole carrier density P(x) and the built-in harrier rotatiful V(x).

The excellent bias light sensitivity is achieved near the alteconstruct depth of less than 0. 2 micros natur. The substruct deping level was  $Na = 5 \times 10^{16} \, \mathrm{cm^2}$ . This idea of the unique  $V^{-1}N^2$  parents type  $V^{-1}$  princed Theolodook was introduced for the first time in 1975 by Elapovan in this three Lapovanese parents? In series, and Elapovane reported in his 1978 paper? the 2001 N 4999 VT CCD images sensor using this  $V^{-1}$  parents of  $V^{-1$

However, the actual formation of the daping profile of Firmal Photodiode is very likely to the type D because the normal ion implantation gives the Gaussian doping profile with smooth taking skepe, effectively resulting in the P+PN+P junction type D profile. See Fig. 4.

The heavily doped surface  $P^+$  hole accumulation layer and the relatively, heavily doped  $N^+$  charge collecting region, connected in between by the lightly doped P region of Na=5,  $10^{14} cm^{-2}$

Simulation and electric analysis of the P+PNP junction type D P mod Photodisade was performed. See Fig. 3 which shows the P+P depring profile with the space charge polarization inducing the built-in hurrier electric field enhancing the photo electron hale pair separation mode the built-in harrier potential of KT binNSVA, 0 – 4 KT ev. -0.1 volt.

Nammally the photo electron and hole pair generation and expansion is performed in the electric field monite the depletion region of the PN junction. But the photo-electron and hole pair generation and separation of the P-PNP junction (type II) Princial Photodode is different and quite stepas.

The surface P+P imposity doping alope radices the built-in hariter potential and the resulting built-in hariter electric field enhancies the photo electron pair separation at the very near surface, region of the aftern crystal to gove the encoders blue high sensitivity. This photo electron hole separation mechanism is swiges, quite different from the usual photo electron hole pair separation.

The tusson why the P+FN+P junction type D P most Photodocle can have the excellent blue light sensitivity near the silicon surface depth of 0.2 micro-meter is now explained in details. Simulation and the electrostatic analysis is based on the fact that the maximum depth for the blue light penetration into the silicon crystal is 0.2 micro mater which is very closu to the surface.

Fig. 5: P+PN+P jursation type Burnel Pinnel Photodiode defined in Hagiwara Japanese 1975-127647 patent.

The life time of the photo generated minority currier can be measured using the photoconduction effect and the diffusion length Ld can be determined, which is needed for electrons to survive in the majority carrier hole-rich P substrate area. See Fig. 5. Photo electrons are expected to neach the buried N charge collecting region. The situation is similar to the minority carrier electrons injected from the emitter terminal into the majority carrier hole-rich base area of a NPN bipolar transister. If the base region width is narrow, enough, one or two electrons may recombine with the holes in the base, but the most of the electrons can reach the collector terminal of the attentily reverse-bissed depletion region. The N buried resign of Premed Photodiode acts as if the collector region of the NPN hipolar transistor does. This photo electron generation separation physical mechanism is unique and quite different from the ordinary electron hole pair separation in the PN junction depletion region.

#### II. NO IMAGE LAG FEATURE