半導体基体に、第1電導型の第1半導体領域と、之の上に形成された第2導電型の第2半導体領域とが形成されて光感知部と之よりの電荷を転送する電荷転送部とが上記半導体基体の主面に沿う如〈配置されて成る固体撮像装置に於いて、上記光感知部の上記第2半導体領域に整流性接合が形成され、該接合をエミッタ接合とし、上記第1及び第2半導体領域間の接合をコレクタ接合とするトランジスタを形成し、該トランジスタのベースとなる上記第2半導体領域に光学像に応じた電荷を蓄積し、ここに蓄積された電荷を上記転送部に移行させて、その転送を行うようにしたことを特徴とする固体撮像装置。

半導体基体の一方の主面側に、絶縁膜を介して電荷転送用電極が被着配列される1の導電型の転送領域が形成され、之より上記半導体基体の他方の主面側に上記転送領域に接する他の導電型の領域と該領域に接する1の導電型の領域とより成る受光領域が形成され、上記転送用電極に所要の電圧を印加することにより、上記受光領域に蓄積した電荷を上記転送領域に転送し、上記電荷転送用電極に上記所要の電圧とは異るクロック電圧を印加して上記基体の上記一方の主面に沿って電荷の転送を行うようにしたことを特徴とする固体撮像装置。

半導体基体の一方の主面側に、絶縁膜を介して電荷転送用電極が被着配列される1の導電型の転送領域が形成され、之に対向し且つ之より上記半導体基体の他方の主面側に上記転送領域との間に他の導電型のベース領域を介して受光領域が形成され、上記ベース領域に所定電圧を印加することにより上記受光領域に蓄積した電荷を上記転送領域に転送し、上記電荷転送用電極に指定のクロック電圧を印加して電荷の転送を行うようにしたことを特徴とする固体撮像装置。

# Pinned Photodiode (Sony original HAD sensor) was invented by Hagiwara in 1975 at Sony

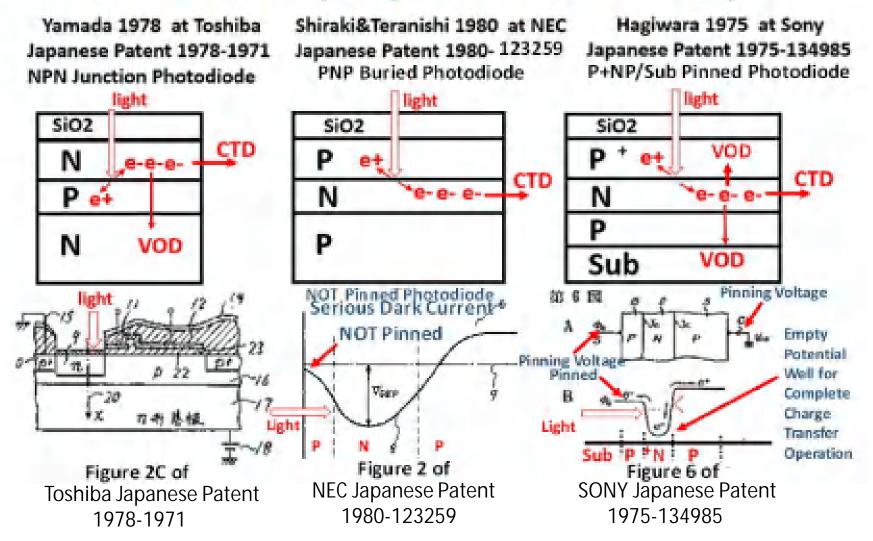

NEC 1980 Japanese Patent is NOT Pinned Photodiode Patent!

# Pinned Photodiode Family Tree

Hagiwara is the inventor of the KODAK Pinned Photodiode, the NEC Buried Photodiode and the SONY HAD sensor.

# Grand Father

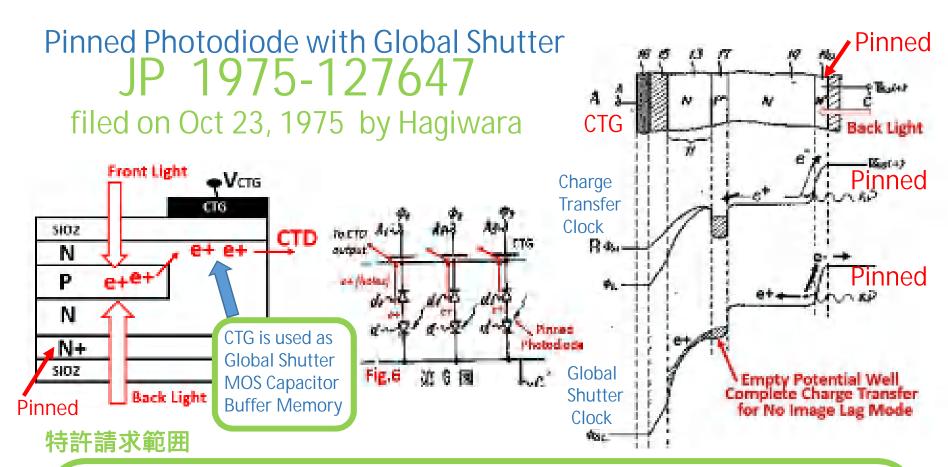

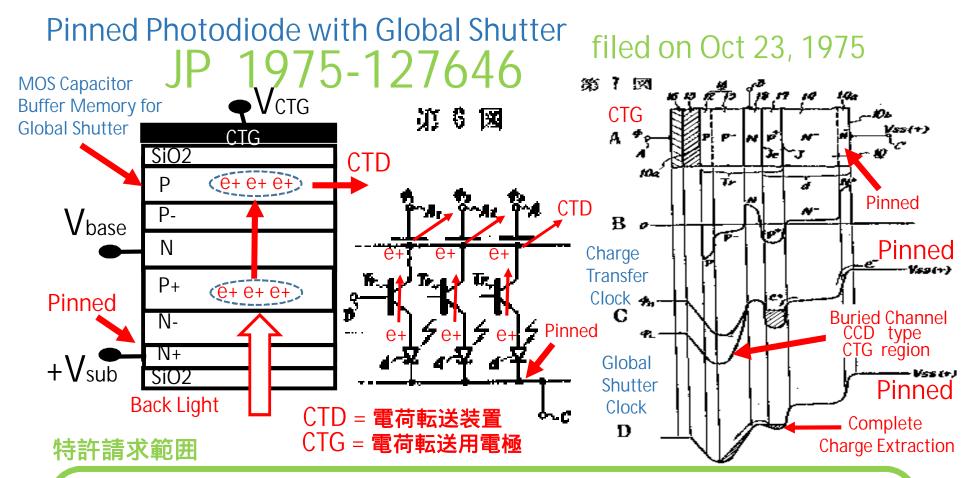

Hagiwara Patent 1975-127647 on the N+NsubP+N junction Pinned/Buried Photodiode with Global Shutter Scheme and Back Light Illumination

#### **Grand Mather**

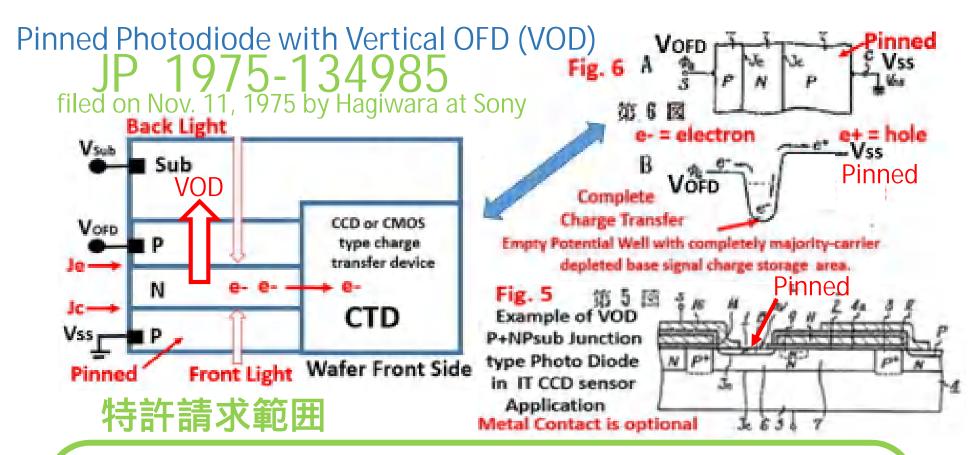

Hagiwara Patent 1975-134985 on the P+NPNsub junction Pinned Photodiode with Vertical OFD (VOD)

# MOTHER

Hagiwara CSSD 1978 Paper of the P+NP<sub>sub</sub> junction Pinned Photodiode on the 380H x 490V FT CCD Imager

#### First Child

NEC IEDM1982 Paper of the PNPsub junction Buried Photodiode on the ILT CCD Imager

## Second Child

KODAK IEDM1984 Paper of the P+NPsub junction Pinned Photodiode on the MOS Imager

## Third Child

SONY 1987 HAD Sensor of the P+NPwellNsub junction Pinned Photodiode with Vertical OFD (VOD)

| Type<br>Feature           | Classical<br>N+Psub<br>Photodiode | Surface<br>Channel CCD<br>Photodiode | Buried<br>Channel CCD<br>Photodiode | 11111338 | NEC<br>1980<br>PNP Buried<br>Photodiode | SONY HAD Hagiwara 1975 P+NPNsub Pinned Photodiode |

|---------------------------|-----------------------------------|--------------------------------------|-------------------------------------|----------|-----------------------------------------|---------------------------------------------------|

| Blue Light<br>Sensitivity | 0                                 | X                                    | X                                   | 0        | 0                                       | 0                                                 |

| Image Lag                 | X                                 | O                                    | O                                   | X        | O                                       | O                                                 |

| Surface<br>Dark Currer    | nt X                              | X                                    | X                                   | X        | X                                       | 0                                                 |

| Surface<br>Trap Noise     | X                                 | X                                    | 0                                   | X        | X                                       | 0                                                 |

| Vertical OF<br>(VOD)      |                                   | X                                    | X                                   | O        | X                                       | O                                                 |

| Global<br>Shutter         | X                                 | 0                                    | 0                                   | X        | X                                       | 0                                                 |

Hagiwara at Sony filed two Japanese Patents in 1975. One (JAP 1975-127647) is the N+NP+N junction type Pinned Photodiode with the MOS type CTG as the Global Shutter Buffer Memory. And the other (JAP 1975-134985) is the P+NPNsub junction type Pinned Photodiode with the built-in vertical overflow drain (VOD) and the hole accumulation surface P+ layer with the pinned surface potential. The P+ layer quenched the positively charged surface fixed trap states Qss that would create the serious surface dark current.