### Fossum insulted in his 2014 paper Sony and Hagiwara 1975 PPD invention.

The surface P+ layer

is NOT connected to

the LOCOS P+ layer.

N

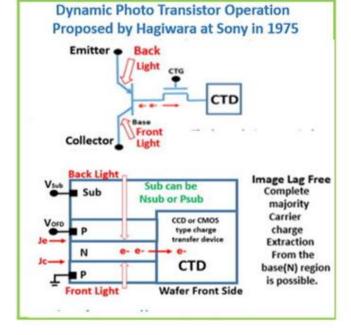

Indeed, Hagiwara invented PPD with VOD and the virtual charge transfer in 1975 !!

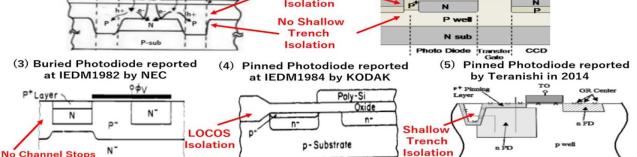

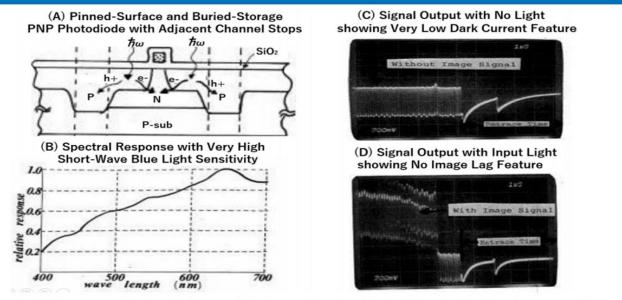

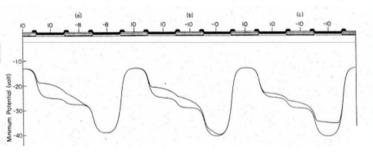

HEE JOURNAL OF THE ELECTRON DEVICES SOCIETY, VOL The surface P+ layer Sony HAD (PPD+VOD) does not use LOCOS !!! may be floating and P4 A Review of the Pinned Photodiode for this photodiode may CCD and CMOS Image Sensors have serious image lag. False P Eric R. Fossum, Fellow, IEEE, and Donald B. Hondongwa, Student Member, IEEE Many people now said this is a fake paper ! Serious Image Lag? C. Other Contributions to the PPD Invention did not address complete charge transfer, lag or anti-bloon NOT properties found in the NEC low-lag device, and does not False The PPD structure, while invented for low lag ILT CCD apconnected seem to contain the built-in potential step and charge transfer ation, shares a strong resemblance to the Hynecek virtual-se CCD structure, with the exception of the VOD. The two device aspects of the virtual-phase CCD. Hagiwara repeats These claims in a 2001 paper [26] and shows a VOD structure inventions were solving different problems with essentially the SW that is not found in the 1975 patent application. Sony did In the same device structure and operating principles. In 1975, Hagiwara at Sony filed a patent application on bipolar structures for CCDs in which a *pnp* vertical structure not seem to pursue the HAD structure until well after the NEC paper was published. However, the "narrow-gate" CCD with an open p-type surface region for improved QE also discloxed in the 1975 application was reported in more detail by Hagiwara et al. at Sony in 1978 [27]. A similar structure was disclosed, among several structures [24]. The top p layer was connected by metal to a bias used to control full-well This is NOT PPD ! capacity and the n-type base layer was proposed for carrier storage. In an unusual paper, Hagiwara, in 1996, revisited the by Hagiwara et al. at Sony in 1978 [27]. A similar structure was used extensively by Philips [28]. × 1975 invention and claimed it was essentially the invention of The PPD, as it is most con monly used today, bears the ned photodiode implemented in a CMOS image centrations. (Dimensional units are microns) both the virtual phase CCD and the NEC low-lag structures, as well as the basis of the Sony so-called "Hole Accumulation Diode," or HAD structure [25]. <u>However, the 1975 application</u> ongest resemblar nce to the Teranishi et al. ILT CCD device. Thus, these days Teranishi is considered as the primary inventor of the modern PPD [29]. Hagiwara in 1975 invented PPD with VOD and the virtual charge transfer.

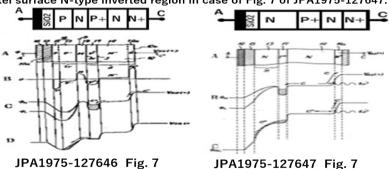

Study the Japanese Patents 1975-127646, 1975-127647 and 1975-134985.

## rue History of Photodiod

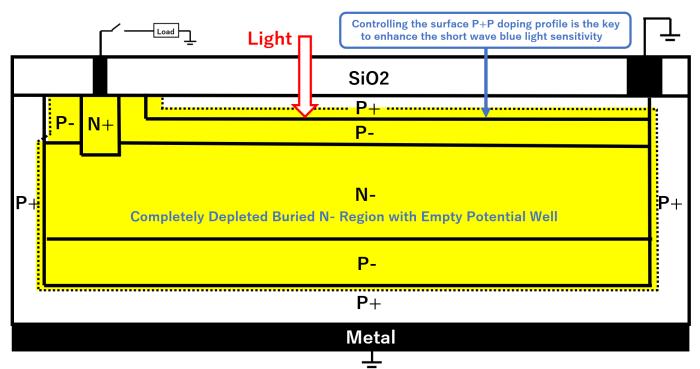

First Pinned Photodiode was invented by Hagiwara in 1975 and reported at SSDM1978 by Sony. Sony never used LOCOS isolation nor Shallow Trench Isolation. Both suffer the yield problem of Dark Current and White Defects. Instead, Sony used high energy ion implantation to form the adjacent heavily doped P+ channel stops region with the Lamp Anneal Technology invented by Kazuo Nishiyama at Sony.

(1) The first Pinned Photodiode with the adjacent (2) Pinned Photodiode with the adjacent P+ channel stops P+ channel stops and no LOCOS isolation and no LOCOS isolation as explained by ssis.or.jp in invented and reported at SSDM1978 by Hagiwara. the official Semiconductor History Museum WEB site. No LOCOS SiO (B) Isolation

Sony Pinned Photodiode has  $\,$  the adjacent P $_+$  heavily doped  $\,$  channel stops always  $\,$  directly grounded to the metal wire at the surface since 1978. Sony never used LOCOS isolation nor Shallow Trench Isolation.

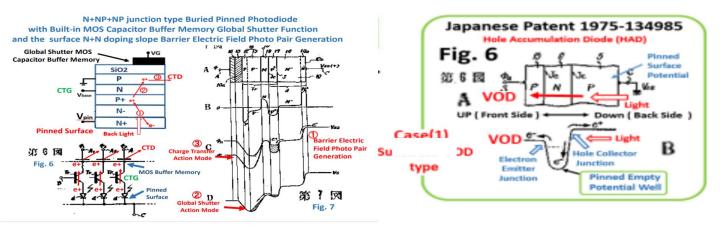

### Who invented Electric Shutter ?

Hagiwara at Sony invented Electric Shutter in October 23, 1975. The evidence is give and explained in Fig. 7 of the Japanese patent application, JPA1975-127646, in which the first Electric Shutter function was defined. The photo charge is transferred and drained to the in-pixel buried channel type vertical overflow drain (VOD) region, which is defined as the buried channel region of the buried channel type CCD/MOS buffer memory capacitor. The threevoltage-level clocking scheme (Clock C and D) of the first Electric Shutter Function mode was defined in Fig. 7 of JPA1975-127646, using the strong punch-thru action mode between the buried P type photo charge storage region and the P-type in-pixel vertical overflow drain (VOD) region. The strong draining gate clock D voltage as shown by creates the very deep potential well in the in-pixel P-type buried vertical overflow drain (VOD) region in case of Fig. 7 of JPA1975-127646 while the strong draining gate clock C voltage creates the very deep potential well in the in-pixel surface N-type inverted region in case of Fig. 7 of JPA1975-127647.

Hagiwara at Sony invented in 1975 the first Electric Shutter Function.

To achieve the complete Electric Shutter function, the surface of the photodiode must be pinned and fixed by the external constant voltage with the zero resistance.

The first Pinned Photodiode was invented by Hagiwara in 1975 to achieve the electric shutter function.

JPA1975-127646 Fig. 7

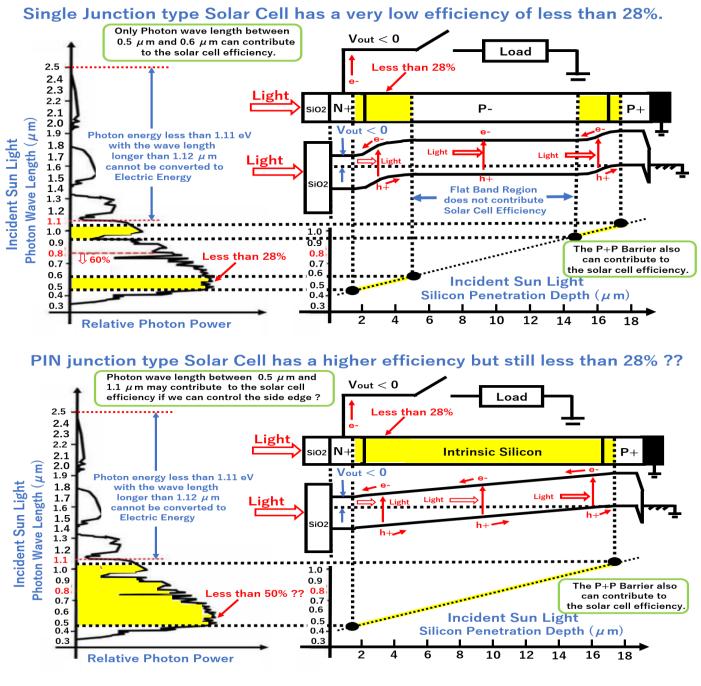

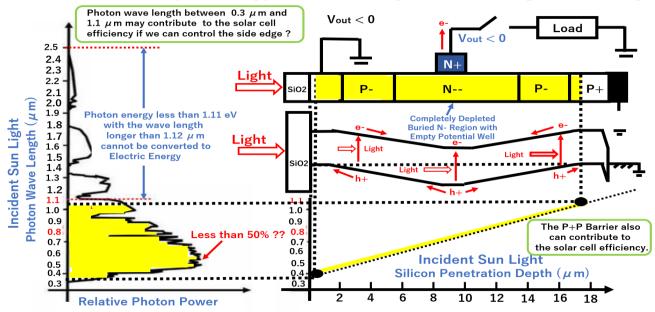

#### P+P-N-P-P+ double junction type Solar Cell may have much higher efficiency

The newly proposed P+P-N-P-P+ junction type Solar Cell may have a higher efficiency.

Wide Gap and Tandem Semiconductors were needed for the short-wave high-energy sun-light component to penetrate deep into the semiconductor crystal, where we can form the depletion region with the barrier electric field, which is needed to separate the photo electron and hole pairs. However, the surface P+P doping variation by the clever ion implantation technology can also create the surface barrier electric field for the short-wave blue light. This idea was confirmed in 1978 and reported in SSDM1978 by Hagiwara.

SSDM1978 paper on the PNP junction type Pinned Photodiode with the Pinned P+ surface connected to the adjacent P+ channel stop:

Yoshiaki Hagiwara, Motoaki Abe and Chikara Okada, "A 380H x 488V CCD Imager with Narrow Channel Transfer Gates", Proceeding of 10<sup>th</sup> Conference on Solid State Devices, Tokyo 1978, Japanese Journal of Applied Physics, Volume 18 Sup 18-1, pp. 367-369.

# $\begin{array}{c} \textbf{True History of Photodiode} \\ \textbf{(1) Single Junction Type Dynamic Photodiode before 1970} \\ \textbf{Thermal CkT Noise} \\ \textbf{Cout} \\ \textbf{C$

Figure 3. 1T1C type MOS Image Sensor with a Large Output Data Line Capacitance.

### (2) CCD/MOS Capacitor type Dynamic Photodiode invented in 1970

SONY 1980 Two-chip CCD Color Video Camera XC-1.

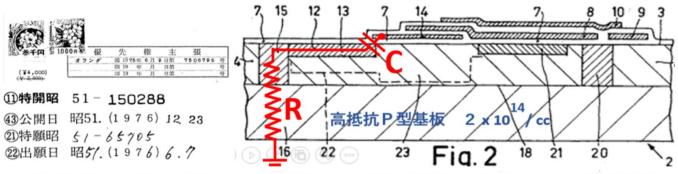

### (3) Double Junction Buried Photodiode by Philips in June 6, 1975.

JPA1976-150288( Netherland Patent 7506795, priority June 7, 1975)

# (4) Triple Junction type Pinned Photodiode with the pinned surface invented by Hagiwara at Sony in Oct 23, 1975.

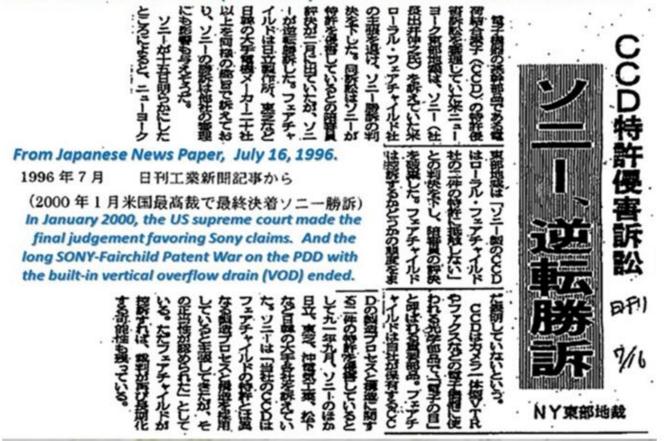

SONY- Fairchild Patent War (1991-2000) on Pinned Photo Diode with Vertical OFD

Finally the Sony-Fairchild Patent Wat(1991-2000) ended over the Sony HAD Sensor which is identical to the P+NPNsub junction type Pinned Photodiode with Vertical Overflow Drain, originally invented by Hagiwara at Sony in 1975.

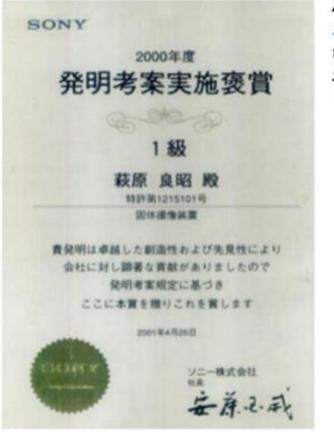

And finally Hagiwara received for his 1975-134985 Japanese Patent officially, the First Patent Award from Mr. Ando, Sony president in April, 2001 after more 26 years of struggles since his invention.

Hagiwara also proposed the thyristor type punch-thru clocking scheme, synchronized with the TV scanning system to achieve the electric shutter.

Electric Shutter Basic Patent Award from Sony President Idei to Yoshiaki Hagiwara for Japanese Patent 1977-126885 by Hagiwara

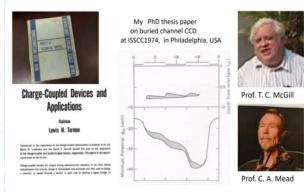

### Caltech\_1975\_PhD\_Thesis\_Yoshiaki\_Daimon\_Hagihara.pdf

Exact Numerical Computer Simulation of Charge Transfer Action in Buried Channel CCD presented in ISSCC1974 by Yoshiaki Daimon-Hagiwara

for details see the PhD Thesis by Yoshiaki Daimon-Hagiwara on June 1975 from Caltech.

Four Japanese Patent Applications on Pinned Photodiode with Electric Shutter Function and also With the in-Pixel Global Shutter MOS/CCD Buffer Memory Function for Modern CMOS Image Sensors.

Japanese Patent Application JPA1975-127646 Japanese Patent Application JPA1975-127647 Japanese Patent Application JPA1975-134985 Japanese Patent Application JPA1977-126885

Five Recently Published Papers by Hagiwara(AIPS) ICECET2021\_Paper75.pdf ICECET2021\_Paper61.pdf

IJSSM2021 e-Journal Paper on Pinned Photodiode.html EDTM2020 Conference Paper\_ID\_3C4\_by\_Hagiwara(PDF)

P2019\_3DIC2019\_Paper\_on\_3D\_Pinned\_Photodiode\_6\_pages.pdf

The first Pinned Photodiode papers in 1977 and 1978 by Hagiwara at Sony Hagiwara\_SSDM1978\_Paper\_on\_Pinned\_Buried\_Photodiode.pdf

P1977\_Narrow\_Cahnnel\_Transfer\_Gate\_CCD\_SSDM1977\_Paper\_by\_Hagiwara.pdf"

**Prof. James McCaldin and Hagiwara**