# JPA 1980-138026

昭55-138026 **GD\$**\$ 留55(1980)10月2日 Ø## 飅 寺西信一 72-元 石原保維 70年 明 白木廣光 の発 193 2 日 NOT

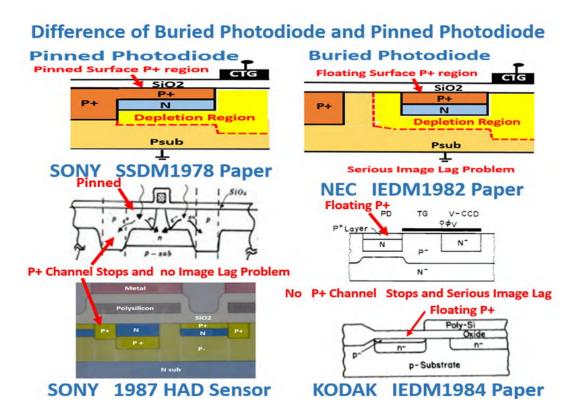

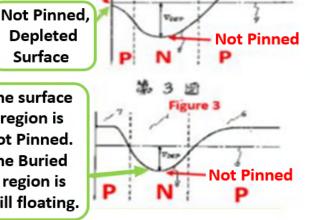

The surface P region is not Pinned. The Buried N region is still floating.

**Electrical Shutter**

Depleted

Surface

1980年10月2日出願

This patent is on the PNP junction type Buried Photodiode but NOT Pinned Photodiode. The surface P region is not pinned and grounded. The surface potential can be of any value depending on the floating buried N region potential, which is actually controlled by the substrate Psub potential which is grounded in this case, but in case of a built-in VOD function P+NPNsub junction photodiode, the P region potential is controlled by the Nsub VOD voltage and can be any value. The surface P region must be pinned by the adjacent P+ channel Stops region or the adjacent metal contact wiring.

#### Comparison of Various Light Detecting Photo Sensor Structures

●P+NPNsub 接合型HAD受光素子 (JPA 1975-134985) 萩原(1975) 基板(Nsub)に P+NP 接合を形成する。Pinned

●NPNsub 接合型 VOD受光素子 ( JPA 1978-1971)

山田(1978) 基板(Nsub)にNP接合を形成する。

●PNPsub 接合型埋込み型受光素子(JPA 1980-138026)

寺西(1980) 基板(Psub) に PN 接合を形成する。

| feature                | N+Psub<br>Photodiode | Channel | Channel | 1978<br>NPNsub | 1980<br>PNPsub | 1975<br>PNPNsub |

|------------------------|----------------------|---------|---------|----------------|----------------|-----------------|

| Blue Light Sensitivity | 0                    | x       | x       | 0              | 0              | 0               |

| Low Image Lag          | ×                    | 0       | 0       | x              | 0              | 0               |

| Surface Dark Current   | x                    | ×       | ×       | x              | 0              | 0               |

| Surface Trap Noise     | ×                    | ×       | 0       | ×              | 0              | 0               |

| Vertical OFD (VOD)     | ~                    | ~       | ~       | 0              | ~              | 0               |

電子 shutter機能は VOD付き Pinned Photodiodeのみが可能です。

## 19 日本国特許庁 (JP)

⑪特許出願公開

# ⑩ 公開特許公報 (A)

昭57-62557

⑤Int. Cl.<sup>3</sup> H 01 L 27/14 29/76 31/10 識別記号

庁内整理番号 7021-5F 6851-5F 7021-5F ❸公開 昭和57年(1982)4月15日

発明の数 2 審査請求 未請求

(全 5 頁)

#### **匈固体撮像装置とその駆動方法**

②特 願 昭55-138026

②出 願 昭55(1980)10月2日

70発 明 者 寺西信一

東京都港区芝五丁目33番1号日

本電気株式会社内

⑫発 明 者 石原保雄

東京都港区芝五丁目33番1号日本電気株式会社内

72発 明 者 白木廣光

東京都港区芝五丁目33番1号日

本電気株式会社内

⑪出。願 人 日本電気株式会社

東京都港区芝5丁目33番1号

仰代 理 人 弁理士 内原晋

明 湖 蓄

発明の名称 固体撮像装置とその駆動方法

#### 特許請求の範囲

1. 第1簿電型の半導体基板と、この基板の主面に形成され光の入射による信号電荷を蓄積する第1導電型と逆導電性の第2導電型の蓄積領域と、この審積領域に対応して設けられた信号電荷転送手段と、前記蓄積武域と前記信号電荷転送手段への信号電荷の転送を制御するトランスファゲートとを有する固体液像装置の単位セルにおいて、前記蓄積領域の表面の全面に前記第1導電型の表面層が設けられ、かつ前記蓄積領域が完全に空乏化するのに必要な前記基板と前記蓄積領域との間の逆バイアス電圧が30ボルト以下であることを确たすように構成されてなることを特象とする固体域像装蔵。

2. 男1編記製の半線体を板と、この基板の主面

に形成され光の入射による信号電荷を蓄積する前 記第1導電型と逆導電性の第2導電型の蓄積領域 と、この蓄積領域に対応して設けられた信号電荷 慰送手段と、前記蓄積領域と前記信号電荷転送手 段との間に設けられ前記蓄積領域から前記信号電 荷転送手段への信号電荷の転送を制御するトラン スファゲートとを有する固体搬像装置の単位セル の、前記蓄積領域の表面の全面に前記第1導電型 の表面層が設けられ、かつ前記蓄積領域が完全に 空乏化するのに必要な前記基板と前記蓄積領域と の間の逆バイアス電圧VDEPが30ボルト以下で あることを満たすように構成された固体撮像装置 において、前記トランスファゲートのチャネル部 の電気的に中性のときのフェルミ電位と真性フェ ルミ電位との差を Vr としたとき、前記基板の内 部の空乏化していない部分のフェルミ電位を基準 とした前記トランスファゲートのチャネル電位の 絶対値 Vch を VDEP + 2VF 以上にすることによっ て前記蓄積領域から前記信号電荷転送手段へ電荷 を移すことを特徴とする固体撮像装置の駆動方法。 発明の詳細な説明

この発明は残像を小さくした固体擬像荘厳とその駆動方法に関する。

国体海像在底の中でも電荷結合素子(CCD)を用いた固体機像装置は出力容量が小さいために維音が小さく、きわめて低照度での機像が可能である。しかし、例えば、従来のp‐n接合を蓄積領域に用いたインターライン転送方式 CCD固体機像装置では低照度ほど残像は目立つようになり、再生画像は見るに耐えないものになってしまう。従って維音が低照度機像展界を決めるのではなく、残像が低照度限界を決めることになる。残像を減少すれば機像可能な展界照度を供くすることが出来る。

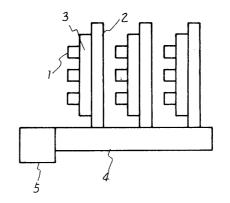

第1図はp-n接合を蓄積領域に用いたインターフイン転送方式 CCD2 次元固体機像装置の平面 模式図である。p型半導体基板の受光側の主面に この基板とpn接合し、入射光による信号電荷を 蓄積するn型の蓄積領域1が多数個複数列に配列 形成されている。蓄積領域1の各列ごとに近接し

次に残像の原因を説明する。p型の塞板の内部のフェルミ電位を基準としたn型の蓄積領域1の電位を Va、トランスファゲート3がオン状態のときのチャンネル電位を Vchとする。この Vaはp型の塞板とn型の蓄積領域1との間の遊バイアス電圧である。また、トランスファゲート3のチャネル部の国域内に中性のときのフェルミ電位と異性フェルミ電位との虚を VFとする。すると VFは、

$$V_F = \frac{kT}{g} \left| \ln \frac{NB}{Ni} \right|$$

と表わされる。ただしkはボルツマン定数、Tは 絶対温度、Yは単位電荷重、NBはチャネル部の 不純物濃度、niは真性微度である。 n 型の番積 領域1を完全に空乏化させるのに必要な VA を VDEP とする。従来の固体擴像装置では番積領域 1のドナー治度が大きく、VDEP は週常の動作条 件の VA よりはるかに大きい。 週常、MO S型の集 対応して信号電荷転送手段としての垂直 CCDレジスタ 2 が形成されている。蓄積領域 1 と垂直CCDレジスタ 2 との間にはトランスフェゲート 3 が設けられている。垂直 CCDレジスタ 2 の一方の端部は水平 CCDレジスタ 4 化接続されており、 この水平 CCDレジスタ 4 の一方の端部は出力装置 5 に接続されている。光電変痕を行なう蓄積領域 1 以外の部分はアルミニウムによって光遮蔽されている。このようなインターライン転送方式 CCD 2 次元イメージセンサの駆動方法と転作の様子を記明する

信号電荷蓄積時に、入射光に反応して蓄積領域

1に信号電荷が蓄積される。との信号はトランスファゲート3がオン状態になりチャネルが形成されることによって、垂直CCDレジスタ2に移される。トランスファゲート3がオフ状態になりチャスルがなくなると、垂直CCDレジスタ2と蓄積領域1との間に電位障壁ができ、信号電荷の次の蓄積が始まる。垂直CCDレジスタ2と水平CCDレジスタ4はパルスによって駆動され、垂直CCDレジスタ4はパルスによって駆動され、垂直CCDレジ

精回路の最高電圧はp-n接合の耐圧とゲート酸 化膜の耐圧によって決まり、30Vである。信号 電荷蓄積時には、入射光に反応して蓄積領域1に 信号電荷である電子が蓄積され、蓄積領域1中の 空乏層は小さくなり、 VA は小さくなる。 トラン スファゲート3がオン状態になり、チャネル電位 がVchとなると、蓄積領域1より垂直CCDレジス タ2へ信号電荷が移り始める。トランスファゲー ト3をMOS電界効果トランジスタ (MOSFET)と みなし、薔癇頭域1をプスとし、垂直CCDレジス 92をドレインと考える。すると  $V_A$  <  $V_{ch}$   $\sim$   $2V_F$ ならばこのMOSFETは強反転状態で動作し、電 荷転送はすみやかに行なわれ、VAはVch-2VF 程度になる。しかし VA > Vch - 2VF ではこの NOSFETは弱反転状態で動作するために、電荷 転送は遅く、VAは最終到達電位であるVch-VF になかなか到達しない、トランスファゲート3を カン状態にするのは垂直帰線期间のうちの1部期 間である。標準テレビジョン方式では垂直帰線期 間は約1110 #secであり、トランスファゲート3

をオン状態にする期間は通常 1 μsee程度から 5 00 μsec 程度までである。例えばトランスファゲート 3 のチャネル長を 5 μm、チャネル幅を 5 μm、 落積領域 1 の容量を 0.0 3 pF とすると、 VA が Ve h - 2 VF程度から Ve h - VF になるのに必要な時間は数十 msec であり、トランスファゲート 3 がオン状態の期間に比較してはるかに大きい。このため、通常のトランスファゲート 3 のオン状態の期間では、信号電荷は蓄積領域 1 より垂直 CCDレジスタ 2 へには転送されず、 1 部の信号電荷が蓄積領域 1 に取り残されることになり、この取り残された信号電荷は以後のトランスファゲート 3 がオン状態になったときに蓄積領域 1 より垂直 CCDレジスタ 2 へ転送され、再生画面上では残像となって表われる欠点があった。

この発明の目的は上記のような残像をなくした 固体環像装置とその駆動方法を提供することにある。

この 完明によれば、第1 導電型の半導体基板と、 この基板の主面に形成され光の入射による信号電

特徴とする固体撮像装置の斟動方法が得られる。 以下この発明の実施例に基いて説明する。

この発明による残像をなくした固体撮像装置で は、従来に比較して蓄積領域1のドナー濃度が低 くなっており、かつ、蓄積領域1の表面の全面に p型の表面層が設けられている。このため蓄積領 域1を完全に空乏化させるのに必要な逆バイアス 毎 圧 VDEP は小さく、VDEP + 2VF は通常のMOS 型集積回路の最高電圧30Vより小さい。 VDEP +2VF <30ボルトであるので、VchをVDEP+ 2VF以上にすることができる。 Vch > VDEP + 2VF とした駆動方法では、トランスファゲート3かオ ン状態になり、チャネル電位がVchになると、蓄 積領域1より垂直CCDレジスタ2へ信号電荷が移 り始める。トランスファゲート3をMOSFETと みなし、畜積領域1をソースとし、垂直CCDレジ スタ2をドレインと考える。すると、 VA の厳終 到達電位 VDEP においても VA < Vch - 2VF である ので、この MOSFET は常に強反転状態で動作し、 電荷転返はすみやかに行なわれ、蓄積領域1が完

荷を蓄積する第1導電型と逆導電性の第2導電型 の蓄積領域と、この蓄積領域に対応して設けられ た信号電荷転送手段と、前記蓄積領域と前記信号 電荷転送手段との間に設けられ前記蓄積領域から 前記信号電荷転送手段への信号電荷の転送を制御 するトランスファゲートとを有する固体撮像装置 の単位セルにおいて、前記蓄積領域の表面の全面 に前記第1導電型の表面層が設けられ、かつ前記 蓄積領域が完全に空乏化するのに必要な前記基板 と雨記蓄積領域との間の逆バイアス電圧が30ボ ルト以下であることを満たすように構成されてな ることを特徴とする固体撮像装置が得られる。さ らに前記との発明の固体撮像装置において、前記 トランスファゲートのチャネル部の電気的に中性 のときのフェルミ電位と真性フェルミ電位との差 を VF としたとき、前記基板の内部の空乏化して いない部分のフェルミ電位を基準とした前記トラ ンスファゲートのチャネル電位の絶対値Vchを VDEP + 2VF以上にすることによって前記蓄積領 域から前記信号電荷転送手段へ電荷を移すことを

全に空乏化し、VA が最終到達電位 VDEP になる。例えばトランスファゲート 3 のチャンネル長が 5  $\mu$ m、チャネル幅が 5  $\mu$ m、蓄積領域 1 の容量が 0.03 pF の場合に、VA が VDEP-2 V 程度から VDEP になるのに必要な時間は高々 100 nsec 程度であり、トランスファゲートがオン状態にある時間 1  $\mu$ soc 程度から 500  $\mu$ soc 程度に比較して非常に速い。この結果、信号電荷は蓄積領域 1 より垂直 CCDレジスタ 2 へ完全に転送され、蓄積領域 1 に信号電荷が取り残されることはなく、残像規象は 起こらない。

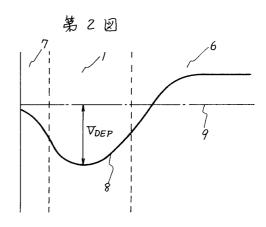

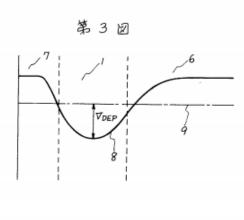

□型の蓄積領域1の表面の全面に設けられた p型の表面層の効果を説明する。第2図と第3図はこの発明のそれぞれ異なる実施例において、蓄横領域1を表面と垂直方向に見たときの電位分布を示した図である。左側が表面であり、表回より p型の表面層7と□型の蓄積領域1と p型の基板6がある。実際8は電子が感じるボテンシャルの分布である。1点鎖線9は p型の基板6の内部の空乏化していない領域でのフェルミ電位であり、電

位の規準とする。これらの図ではn型の蓄積領域 1 が完全に空乏化した場合を示している。第2図 は表面層7のアクセプタ機度が小さく、表面層7 が完全に空乏化している場合であり、第3図は表 血層 7 の表面付近が空乏化していない場合である。 後者の場合、表面層7の空乏化していない部分の 電位は基板6の内部の空乏化していない部分の電 位と等しい。さて表面層7の第1の効果は、上述 したように VDEP を小さくすることである。 n型 の蓄積領域1はp型の基板6とp-n接合するだ けではなく、p型の表面層7ともp-n接合する ために、両方のp-n接合面から空乏層が拡がる ために VDEP は小さくなるのである。第2の効果 は、電位の最大点がシリコンとシリコン表面に設 けられた酸化膜との界面に位置しないだめに、信 号電荷が界面に接触しない。この結果、信号電荷 が界面付近に分布しているトラップにトラップさ れないので、トラップによる残像が生じないとい うことである。さらに第3図に示した実施例の場 合、デバイス表面に設けられた酸化順中や酸化膜

表面上の浮遊電荷の影響が表面層のうちの空乏化 していない表面付近でシードされ、蓄積領域1に は及ばず、ロットやデバイス間での特性のばらつ きが小さくなるという効果がある。またシリコン と酸化膜の界面付近が空乏化していないので、暗 電流が小さいという効果もある。

この発明は、垂直方向の信号電荷転送手段として信号線を用い、この信号線が1個または複数個のMOSFETを介して水平方向の信号電荷転送手段としての水平CCDレジスタや水平バケットブリゲード(BBD)レジスタに接続されている、いわゆるMOS+CCD型2次元間体摄像装置やMOS+BBD型2次元固体撮像装置にも適用できる。また2次元固体撮像装置にも適用できる。

以上nチャネル型の場合の実施例について説明した。pチャネル型の場合は、nチャネル型の場合はでから、行号のある電位は絶対値を用いればよい。例えば、蓄積領域1と基板との間の逆バイアス電圧VAやトランスファゲート

のチャネル部のフェルミ電位と真性フェルミ電位との差 VF は適常絶対値を用いるので、 Pチャンネルでも絶対値を用いる。 基板の内部の空乏化していない部分のフェルミ電位を基準としたトランスファゲートのチャネル電位は R チャネル型の場合は正であり、 Pチャネル型の場合は負なので、絶対値を用いる。

#### 図皿の簡単な説明

第1図は固体微像装置の模式的平面図、第2図 と前3図はこの発明のそれぞれ異なる実施例において、蓄積領域を表面と垂直方向に見たときの電 位分布を示した図である。

1 …… 審積領域、 2 ……信号電荷転送手段(垂直 CCDレジスタ)、 3 ……トランスファゲート、 6 …… 泰板、 7 …… 表面層、 9 …… 基板の内部の空 乏化していない部分のフェルミ電位、 VDEP …… 審積領域が完全に空乏化するのに必要な基板と蓄 積領域との間の逆バイアス電圧。

### 第1回

-237-

Figure 2 of this JPA 1978-138026 patent above shows that both of the surface P region and the Buried N region are completely depleted. The surface P region is evidently not pinned. The buried N region is not pinned by the surface potential. Figure 2 is not evidently Pinned Photodiode. Figure 3 shows that the surface P region has enough holes, more than the total impurity atoms in the total buried N region. However, the surface P region is not by necessity connected to the external voltage and can be floating evidently. There is no description about a pinned surface P region in this JPA 1978-138026 patent. Figure 3 is not by necessity Pinned Photodiode. This JPA 1978-138026 patent is not Pinned Photodiode patent. For Pinned Photodiode, the surface P region must be connected to the external wiring or by the adjacent P+ channel stops region.